ложения запятой частного, триггеров коммутатора и со входами третьей схемы «ИЛИ, выход которой через первый элемент задержки соединен со входами первой схемы «ИЛИ и третьего управляющего триггера, выход последнего соединен через вторую схему «ИЛИ со входом пятого вентиля. Входы четвертого и пятого вентилей соединены через второй элемент задержки с выходом схемы сравнения. Выход пятого вентиля соедипен со входом четвертого управляющего триггера, выход которого соединен с выходными вентилями двоично-десятичного счетчика.

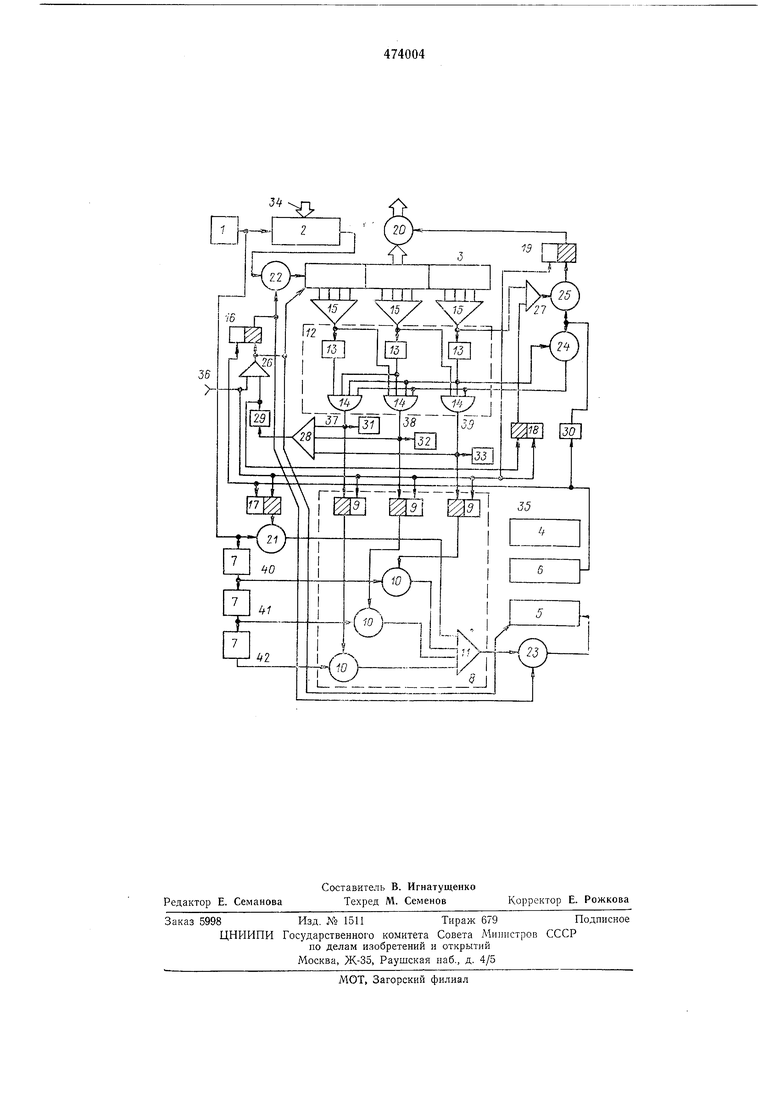

Схема устройства изображена на чертеже.

Устройство содержит генератор 1 импульсов постоянной частоты /о, преобразователь 2 кода делителя в частоту (выполпенный с использованием счетчика, регистра и схемы сравнения), /г-тетрадный двоично-десятичный счетчик 3 (я взято равным трем), регистр 4 делимого, двоичный счетчик 5, схему 6 сравнения, делители 7 частоты на «десять, коммутатор 8 (содержащий триггеры 9, вентпли 10 и схему «ИЛИ 11), схему 12 анализа (содерлсащую инверторы 13 и схемы «И 14), дополнительные схемы «Р1ЛИ 15, объединяющие выходы двоично-десятичного счетчика по тетрадам, управляющие триггеры 16, 17, 18 и 19, выходные вентили 20, вентили 21, 22, 23, 24 и 25, схемы «ИЛИ 26, 27 и 28, элементы задержки 29 и 30 и индикаторы 31, 32 и 33 положения запятой частного.

Работа устройства осуществляется за один-два цикла в зависимости от порядка полученного частного.

Первоначально в устройство по шинам 34 и 35 заносят коды делителя Aj и делимого N. Ири этом код делителя преобразуется в преобразователе 2 в частоту и.мпульсов

В исходном состоянии управляющие триггеры 16 и 17 находятся в состоянии «О. Командой «Пуск по шине 36 управляющие триггеры 16 и 17 устанавливаются в состояние «1, а триггеры 9, 18 и 19, и счетчики 3 и 5 - в состояние «О. При этом вентили 21, 22 и 23 открываются, а вентили 10 и 20 оказываются закрытыми. На вход двоично-десятичного счетчика 3 поступают импульсы частоты fi, а на вход двоичного счетчика 5 - импульсы частоты /о через вентиль 21, схему «ИЛИ 11 н вентиль 23. При достижении в счетчике 5 кода, равного коду делимого, на выходе схемы 6 сравнения образуется импульс, который переводит управляющие триггеры 16 и 17 в состояние «О. При этом вентили 21, 22 и 23 закрываются, и поступление импульсов на счетчики 3 и 5 прекращается. В двоично-десятичном счетчике 3 образуется код частного

-М fo

yVa

Л

Л ,

Импульс с выхода схемы 6 сравнения также поступает через элемент задержки 30 на вентили 23 и 24.

Далее управление устройством осуществляется в зависимости от степени заполнения тетрад двоично-десятичного счетчика 3, т. е. порядком частпого. При этом для случая трехтетрадного двоично-десятичного счетчика 3 возможны четыре ситуации образования

частного (см. таблицу, где А, В, и С - цифры десятичных разрядов частного, приче.м А 7 0). В случае (ситуация а), когда образовавшееся частное в двоично-десятичном счетчике 3 - трехзначное (ABC), т. е. все тетрады

счетчика 3 заполнены, на выходе дополнительной схемы «ИЛИ 15 старшей тетрады двоично-десятичного счетчика 3 образуется единичный потенциал, который через схему «ИЛИ 27 открывает вентнль 25. Тогда импульс с выхода элемента задержки 30 поступает через вентиль 25 на управляющий триггер 19 и переводит его в состояние «1, при этом открываются выходные вентили 20, п код частного jV. поступает на выход устройства.

Таким образом, работа устройства завершается за один цикл.

Если же образовавшееся частное имеет количество значащих цифр меньше трех, т. е. старшая тетрада двоично-десятичного счетчика 3 не заполнена (ситуации б, в пли г в таблице 1), то на выходе дополпительной схемы «ИЛИ 15 старшей тетрады нрисутствует нулевой потенциал, при этом на выходе инвертора 13 схемы 12 анализа, соответствующего

старшей тетраде двоично-десятичного счетчика 3, образуется единичный потенциал, который открывает вентиль 24. В этом случае импульс с выхода элемента задержки 30 поступает через вентиль 24 на управляющий

вход схемы 12 анализа. Схема 12 анализа построена так, что импульс появляется на одном из ее выходов 37, 38 или 39 в зависимости от порядка частного.

Так как не заполнена старшая тетрада

двоично-десятичного счетчика 3, в случае (ситуация б), когда образовавшееся частное в двоично-десятичном счетчике 3 - двухзначное («О АВ), то импульс образуется на выходе 39 схемы 12 анализа и поступает на индикатер 33 полол :ения запятой частного, а также переводит соответствующий триггер 9 коммутатора 8 в состояние «Ь. При этом открывается соответствующий вентиль 10 коммутатора 8. Этот же импульс через схему «ИЛИ

28 и элемент задержки 29 переводит в состояние «Ь управляющие триггеры 16, 18 и в состояние «О - счетчики 3 и 5. Открываются вентили 22, 23 п 25. Выполняется второй цикл работы устройства. На двоично-десятичный счетчик 3 поступают импульсы частоты /j, а

на двоичный счетчик 5 - импульсы частоты /о 10 с выхода 40 делителя 7 частоты через открытый вентиль 10 и схему «ИЛИ И коммутатора 8 и вентиль 23. На выходе схемы 6

сравнения образуется импульс, который переводит управляющий триггер 16 в состояние «О. При этом веитили 22 и 23 закрываются. Импульс с выхода схемы 6 сравнения поступает также через элемент задержки 30 и вентиль 25 на управляющий триггер 19 и переводит его в состояние «1. При этом выходные веитили 20 открываются, и частное

lQ.N,.h

с двоично-десятичного счетчика 3 поступает на выход устройства.

В случае (ситуация в), когда образовавшееся частное в двоично-десятичном счетчике 3 - однозначное («О «О А), так как не заполнены две старн ие тетрады двоично-десятичного счетчика 3, то импульс образуется на выходе 38 схемы 12 анализа, поступает на ипдикатор 32 положения запятой частного и переводит соответствующий триггер 9 коммутатора 8 в состояние «1. Далее устройство работает так же, как в случае ситуации б, но на двоичный счетчик 5 поступают импульсы частоты fo/100 с выхода 41 делителя 7 частоты, а на выход устройства поступает частное.

1000-Л 2-/1

v /о

в случае (ситуация г), когда не заполнена ни одна из тетрад двоично-десятичного счетчика 3, импульс образуется на выходе 37 схемы 12 анализа, поступают на индикатор 31 положения запятой частиого и т. д., апалогично рассмотренным ситуациям бив, но на вход двоичиого счетчика 5 поступают импульсы частоты /0/1000 с выхода 42 делителя 7 частоты, и образуется частное

lOO-JVa-fi

которое независимо от своего порядка поступает на выход устройства.

Элементы задержки 29 и 30 обеспечивают последовательную работу отдельных узлов устройства, исключая ложные срабатывания.

Ситуации образования частного

Предмет изобретения Устройство для деления двоичных чисел, содержащее генератор импульсов, выход которого соединен со входами преобразователя кода делителя в частоту, первого вептпля и цепочки последовательно соединенных делителей частоты, двоично-десятичный счетчик,

вход которого через второй вентиль соединен с выходом преобразователя кода делителя в частоту, коммутатор, выполнеппый на триггерах, веитилях и схеме «ИЛИ, вход которой соедииеп с выходом первого вентиля, а выходы делителей частоты соединены с соответствующими информациониыми входами коммутатора, выход которого через третий вентиль соединен со входом двоичного счетчика, схему сравнения, входы которой соединены с

выходами регистра делимого и двоичного счетчика, первый уиравляющий триггер, выход которого соединен со входами второго и третьего вентилей, второй управляющий триггер, выход которого соединен со входом первого вентиля, щину «Пуск, соединенную с установочными входами второго, третьего и четвертого управляющих триггеров, триггеров коммутатора и через первую схе.му «Р1ЛИ - с установочными входами второго управляющего триггера, двоичного и двоично-десятичного счетчиков, выход схемы сравнения соединен со входами первого и второго управляющих триггеров, схему анализа, выполненную на инверторах и схемах «И, схемы «ИЛИ,

вентили, элементы задержки и индикаторы положения запятой частного, отличающееся тем, что, с целью повышения точности деления, выходы тетрад.двоично-десятичного счетчика соединены со входами соответствующих

дополнительных схем «ИЛИ, выход дополнительной схемы «ИЛИ i-й тетрады соединен через соответствующий инвертор схемы анализа со входом схемы «И 1-й тетрады и входами схем «И всех предыдущпх младшпх

тетрад и иепосредствеино соединен со входом схе.мы «И последующей старщей тетрады, выход дополнительной схемы «ИЛИ старшей тетрады непосредственно соединен со входом второй схемы «РШИ и через соответствующий инвертор схемы анализа - со входом четвертого вентиля, выход которого соединен со входами всех схем «И, последних соединены со входами соответствующих индикаторов положения запятой частного, триггеров коммутатора и со входами третьей схемы «ИЛИ, выход которой через первый элемент задержки соединен со входами первой схемы «ИЛИ и третьего управляющего триггера, выход последнего соединен через вторую схему

«ИЛИ со входом пятого вентиля, входы четвертого и пятого вентилей соединены через второй элемент задержки с выходом схе.мы сравнения, выход иятого вентиля соединен со входом четвертого управляющего триггера,

выход которого соединен с выходными вентилями.

3

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1151957A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Преобразователь параллельного двоично- десятичного кода 8-4-2-1 в частоту | 1977 |

|

SU714644A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления двоичных чисел | 1984 |

|

SU1233139A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

Авторы

Даты

1975-06-15—Публикация

1972-12-19—Подача