1

Изобретение может быть использовано в автоматике и вычислительной технике.

Известно устройство приоритетного подключения процессоров к ЗУ, содержащее Л блоков коммутации, каждый из которых содерл{ит триггер памяти запроса, триггер разрешения, один из входов которого соединен с выходом первого элемента «И.

Известно также устройство приоритетного обращения к блоку оперативной памяти (ОЗУ) в мультивычислительной системе, в котором вычислители (процессоры) на-правляют запросы на обращение к ЗУ в соответствующие разряды регистра заявок. Число разрядов регистра заявок равно числу вычислителей. В зависимости от наличия заявки и приоритетности задачи вычислитель получает разрешение на обращение к ЗУ. Динамические приоритеты обрабатываемых задач содержатся в регистрах приоритета. Перед каждым обращепием вычислителя к ЗУ сигнал разрешения обращения к ОЗУ последовательно проходит ряд ло -ических схем и в зависимости от наличия запроса и приоритетности задачи формируется сигнал обращения к блоку ОЗУ, который проходит через элемент «И.

Недостатком таких устройств является малое быстродействие.

С целью устранения этого недостатка в предложенное устройство дополнительно вве2

ден генератор тактовых импульсов, выход которого соединен со входами триггеров разрещения блоков коммутации. В состав каждого блока коммутации введены второй и третий элементы «И и триггер запроса.

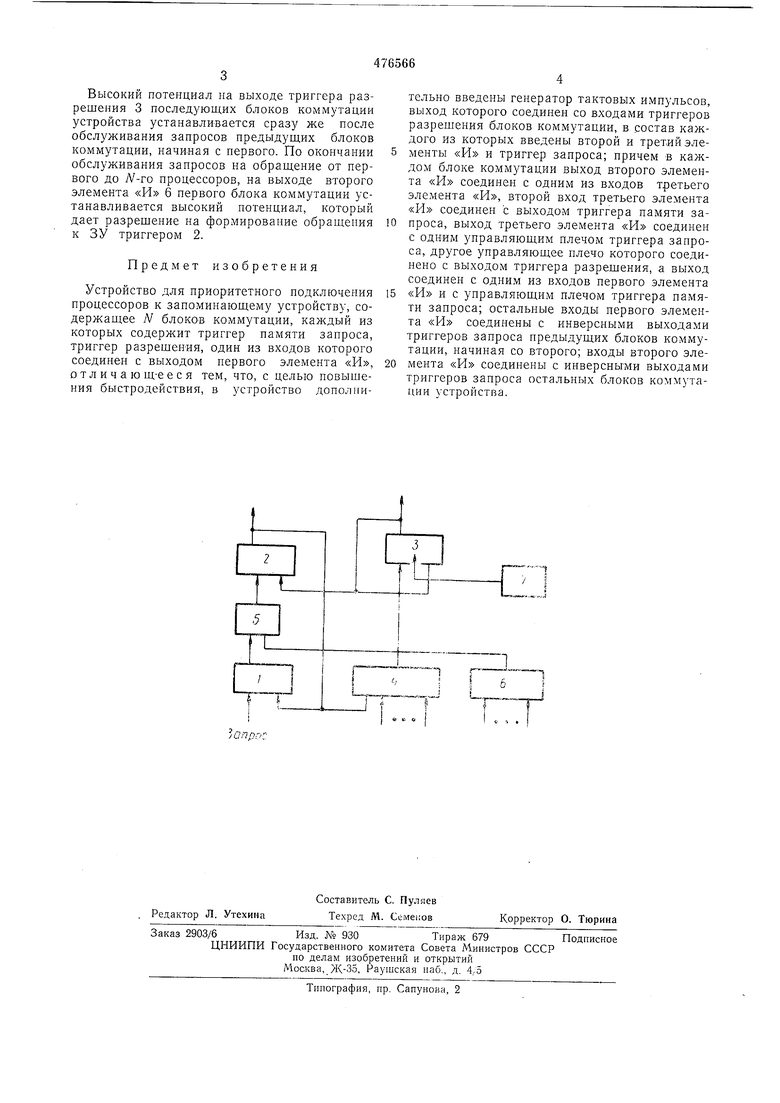

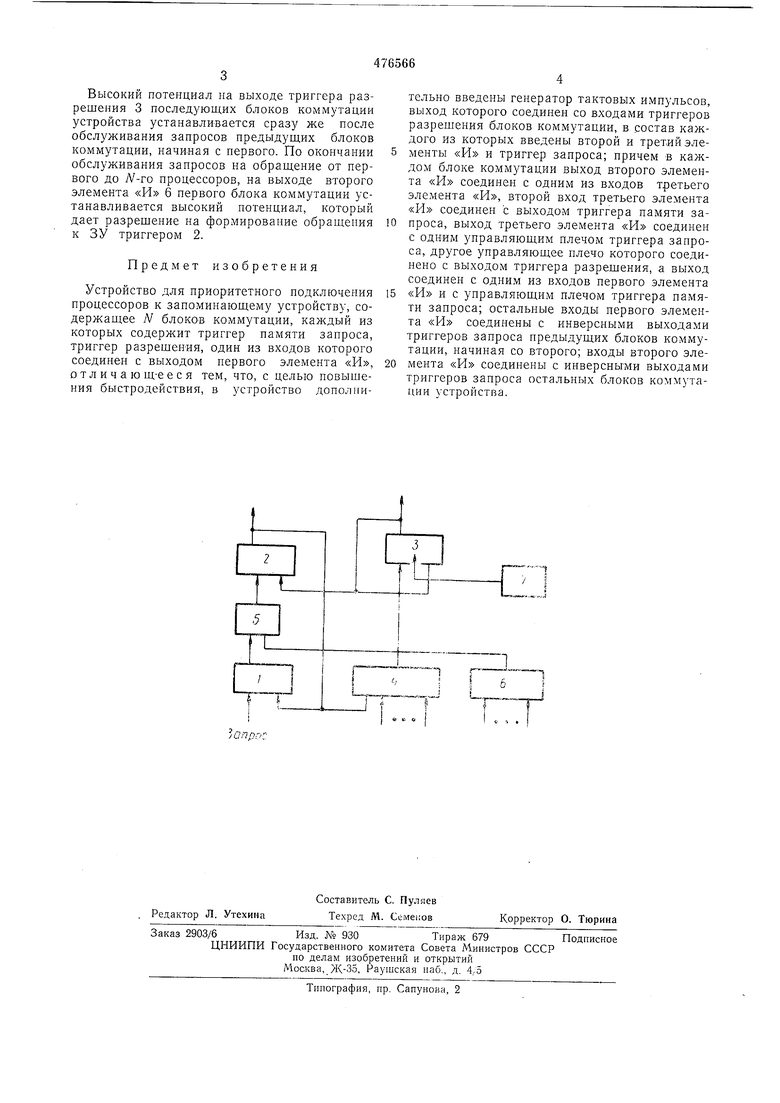

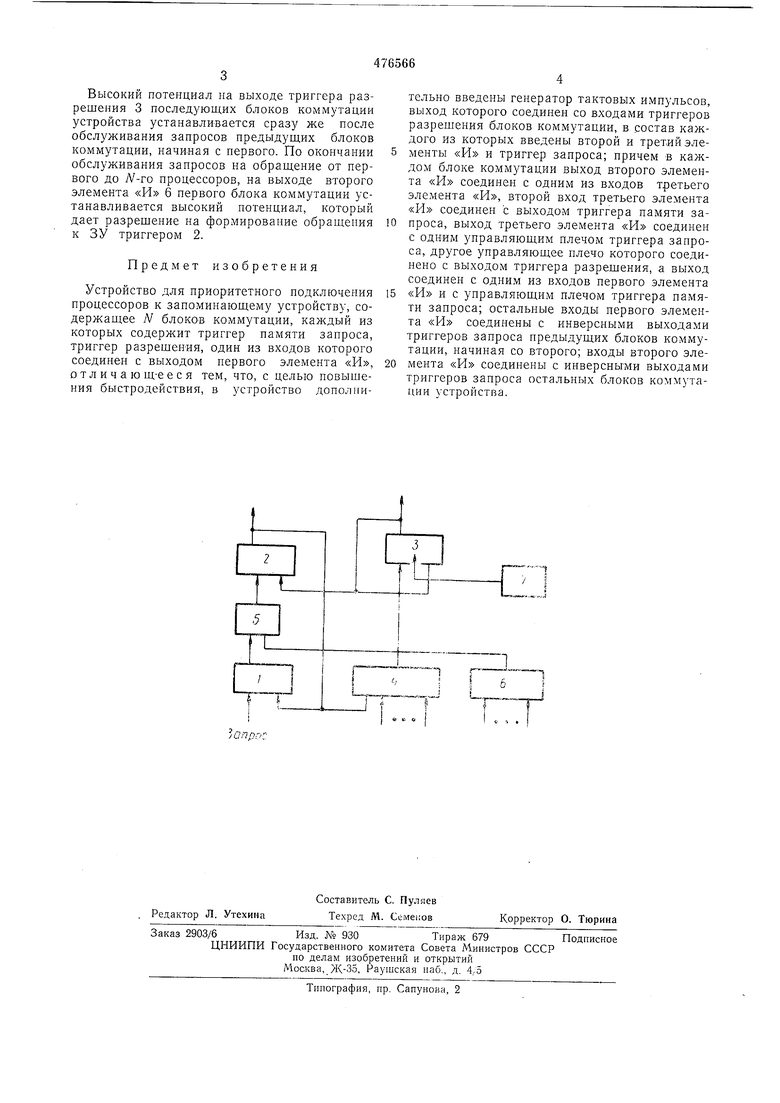

На чертел е изображено устройство для приоритетного подключепия процессоров. Работу устройства разберем на примере работы одного блока коммутации (звена).

В исходном состоянии на выходах триггера намяти запроса 1, триггера запроса 2, триггера разрещения 3, первого 4 и третьего 5 элементов «И - низкий потенциал, на выходе

второго элемента «П 6 - высокий потенциал. От сигнала «Запрос триггер памяти запроса устанавливается в «единичное состояние и через элел1ент «П 5 устанавливает триггер занроса 2 в единичное состояние, при котором

через первый элемент «И 4 устанавливается на выходе триггера разрешения 3 высокий потенциал, а триггер памяти запроса 1 устанавливается в нулевое состояние. От заднего фронта тактового импульса генератора тактовых имнульсов 7 при наличии высокого потенциала на выходе первого элемента «Н 4 триггер разрещения устанавливается в единичное состояние, разрещая обращение к ЗУ, и устанавливает триггер запроса 2 в нулевое состояние.

Высокий потенциал иа выходе триггера разрешения 3 последующих блоков коммутации устройства устанавливается сразу же после обслуживания запросов предыдущих блоков коммутации, начиная с первого. По окончании обслуживания запросов на обращение от первого до Л-го процессоров, на выходе второго элемента «И 6 первого блока коммутации устанавливается высокий потенциал, который дает разрешение на формирование обращения к ЗУ триггером 2.

Предмет изобретения

Устройство для приоритетного нодключения процессоров к запоминающему устройству, содержащее N блоков коммутации, каждый из которых содержит триггер памяти запроса, триггер разрещения, один из входов которого соединен с выходом первого элемента «И, от л и ч а ю щ-е е с я тем, что, с целью повышения быстродействия, в устройство дополнительно введены генератор тактовых импульсов, выход которого соединен со входами триггеров разрещения блоков коммутации, в состав каждого из которых введены второй и третий элементы «И и триггер запроса; причем в каждом блоке коммутации выход второго элемента «И соединен с одним из входов третьего элемента «И, второй вход третьего элемента «И соединен с выходом триггера памяти запроса, выход третьего элемента «И соединен с одним управляющим нлечом триггера запроса, другое управляющее плечо которого соединено с выходом триггера разрещения, а выход соединен с одним из входов первого элемента

«И и с управляющим плечом триггера памяти запроса; остальные входы первого элемента «И соединены с инверсными выходами триггеров запроса предыдущих блоков коммутации, начиная со второго; входы второго элемента «И соединены с инверсными выходами триггеров запроса остальных блоков коммутации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1970 |

|

SU281901A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Авторы

Даты

1975-07-05—Публикация

1973-04-12—Подача