(54) ДИНАМИЧЕСКАЯ 51ЧЕЙКА ПАМЯТИ НА МДП ТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Ячейка памяти | 1987 |

|

SU1444888A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

1

I Изобретение относится к вычислительной технике и предназначено для построения полупроводниковых запоминающих устройств с произвольной выборкой.

Известна ячейка памяти на МДГ1 транзисторах с индуцировшшыми каналами,

содержащая информационные ;транзисторы, соединенные по триггер ной схеме и адрес- ные транз11С1хэры, включенные между плечами триггера и разрядными шинами, эатворы которых подключены к адресной шине.

Цель изобретения - уменьшение площади, занимаемой ячейкой на кристалле, увеличение быстродействия и уменьшение потребляемой мощности.

В предлагаемой схеме последовательно с адресными транзисторами включены дополнительные нагрузочные транзисторы с встроенным каналом, затворы и истоки которых подключены к стокам адресных транзисторов, стоки - к разрядным шинам

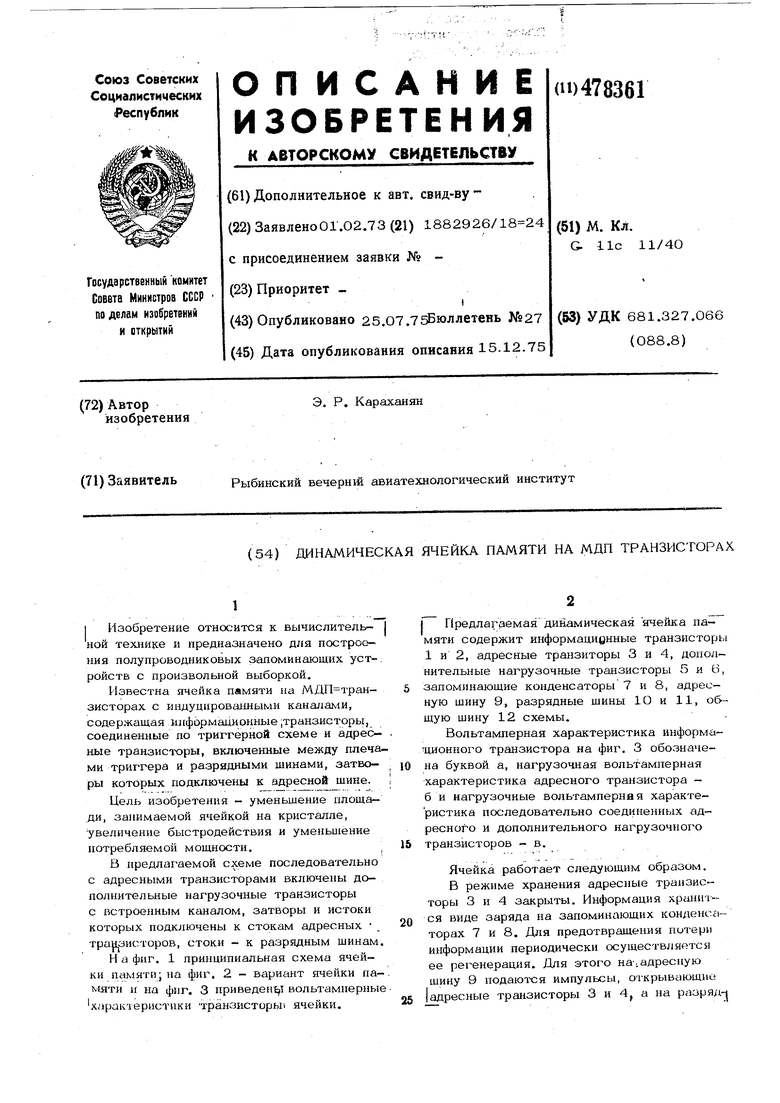

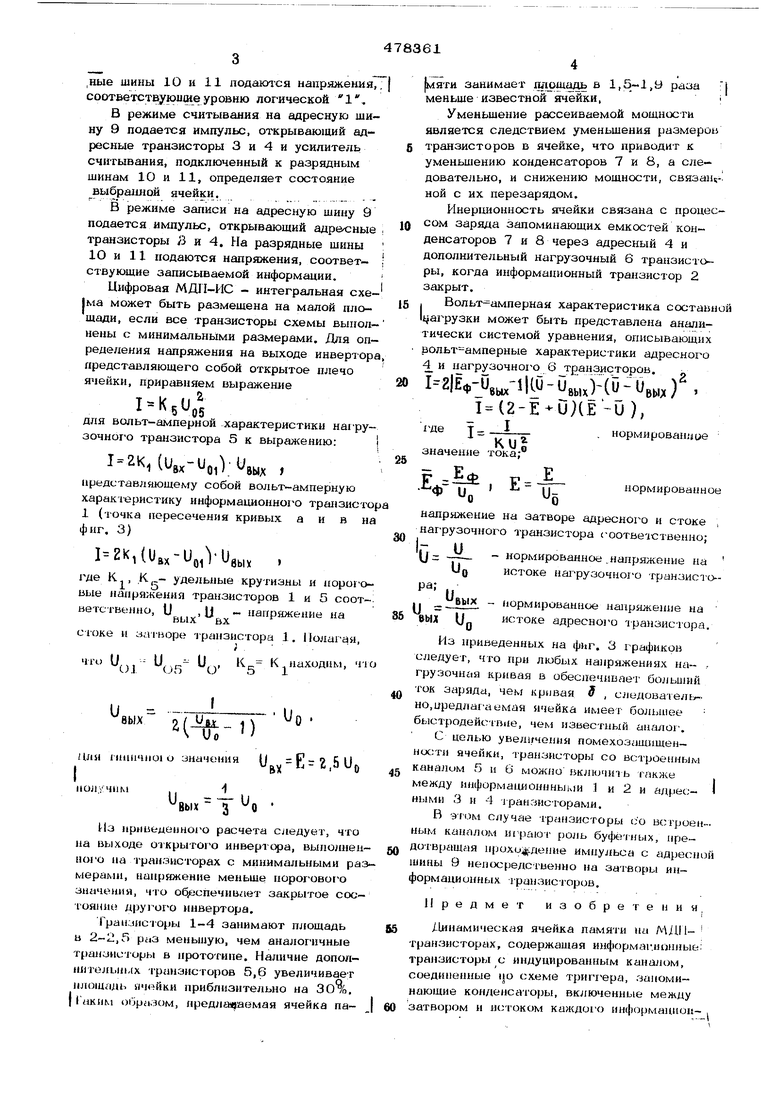

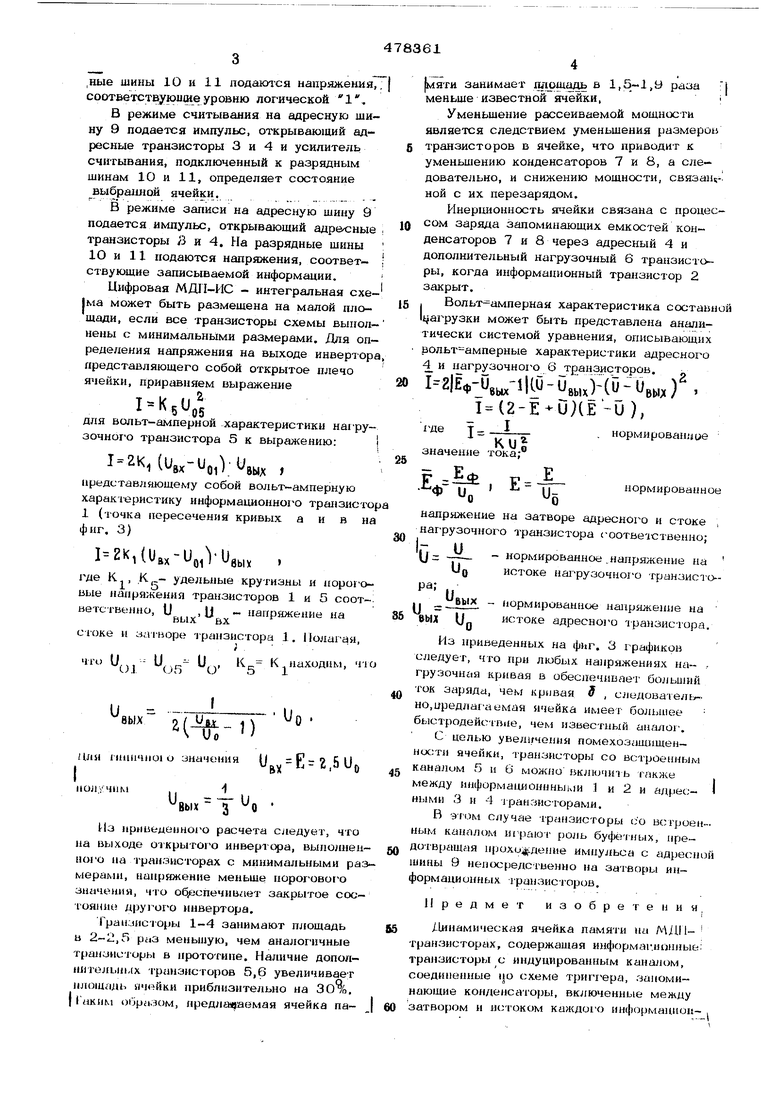

И а фиг. 1 принципиальная схема ячейки памяти; на фиг. 2 - варигшт ячейки па- мяти н на фиг. 3 приведен вольтамиерны характеристики транзисторы ячейки.

I Предлагаемая динамическая ячейка памяти содержит информациенные транзисторы 1 и 2, адресные транзиторы 3 и 4, дополнительные нагрузочные транзисторы 5 и в,

запоминающие конденсаторы 7 и 8, адресную шину 9, разрядные шины 1О и 11, об шую шину 12 схемы.

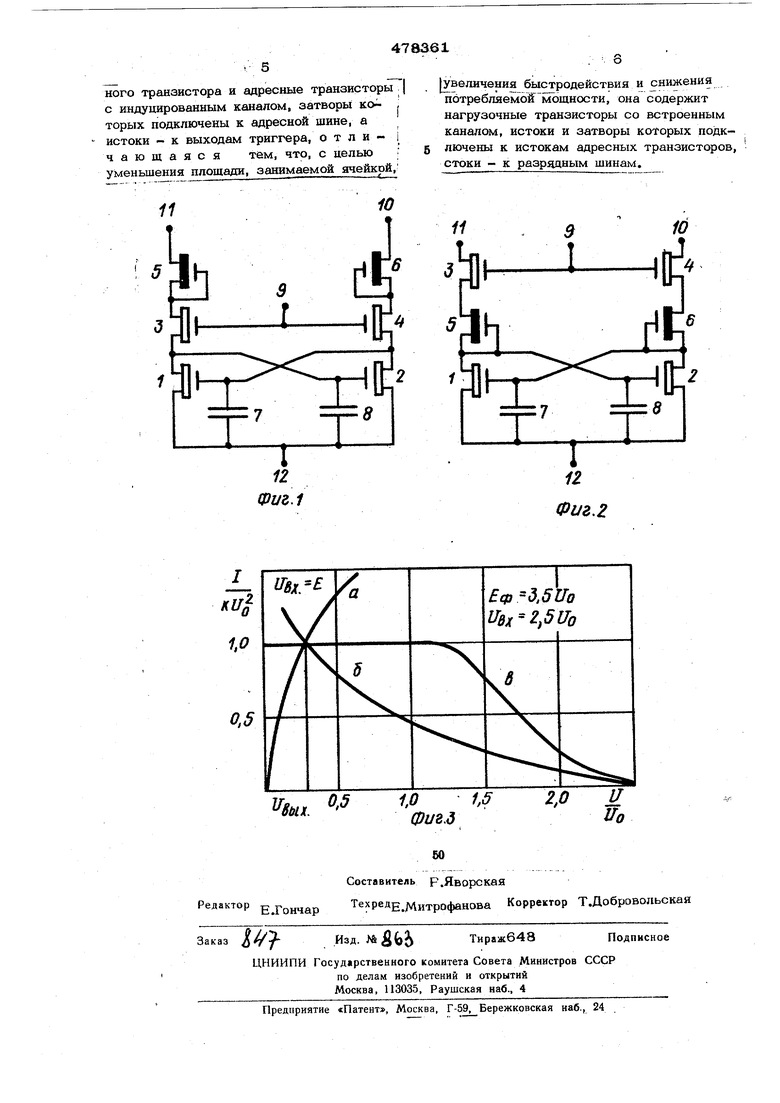

Вольтамперная характеристика информационного транзистора на фиг. 3 обозначена буквой а, нагрузочная вольтамперная характеристика адресного транзистора б и нагрузочные вольтамперная характеристика последовательно соединенных адресного и дополнительного нагрузочного

транзисторов - в.

Ячейка работает следующим образом. В режиме хранения адресные транзисторы 3 и 4 закрыты. Информация хранич-ся виде заряда на запоминающих конденсаторах 7 и 8. Для предотвращения потери информации периодически осуществляется ее регенерация. Для этого на-, адресную шину 9 подаю1х;я импульсы, открывающие I адресные транзисторы 3 и 4, а на разряд.,ные шины 10 и 11 подаются напряжения, соответствуюишеуровню логической 1. В режиме считывания на адресную шину 9 подается импульс, открывающий адресные транзисторы 3 и 4 и усилитель считывания, подключенный к разрядным шинам 10 и 11, определяет состояние выбралшой ячейки.. . В режиме записи на адресную шину 9 подается импульс, открывающий адр&сные транзисторы /3 и 4. На разрядные шины 10 и 11 подаются напряжения, соответствуюш;ие записываемой информации. Цифровая МДП-ИС - интегральная схе 1ма может быть размешена на малой площади, если все транзисторы схемы выпол иены с минимальными размерами. Для оп ределения напряжения на выходе инвертор представляющего собой открытое плечо ячейки, приравняем выражение . для вольт-амперной характеристики нагру зочного транзистора 5 к выражению: b-2K,(Uex-UoO. представляющему собой вольт-амперную харакч-еристику информационно о транзист 1 (точка пересечения кривых а и в н фиг. 3) ,(U,,-Uo, 1 вЫ)( где К, К,-- удельные крутизны и порого вые tiaapJiiKBHan транзисторов 1 и 5 соот Бвтственно, и , И напряжение вых вх стоке и затворе транзистора 1. llojiaiasi, и..- и К к находим, ч О 5 2№-) /1ля niiuiHiioi о значения (J Е-2 5U tЛ л. получим (1L 11 Вых 3 О Из приведенного расчета следует, что па выходе О1крытого инвертора, выполпен ного па чранзисторах с минимальными ра мерами, напряжение меньше порогового значения, что oб icпeчивaeт закрытое сое- чояпие другого инвертора. Граизисч-оры 1-4 занимают площадь в 2-2,5 раз меньшую, чем аналогичные трапзисчоры в прототипе. Наличие дополничольпьсх чранзисторов 5,6 увеличивает нлсзщсщь ичейки приблизительно на 30%. I Таким образом, предлагаемая ячейка па1мяти занимает щшщадь в 1,5-1,9 раза :| меньше известной ячейки, Уменьшение рассеиваемой мощности является следствием уменьшения размеров транзисторов в ячейке, что приводит к уменьшению конденсаторов 7 и 8, а следовательно, и снижению мошности, связан5-. ной с их перезарядом. Инерционность ячейки связана с процессом заряда запоминающих емкостей конденсаторов 7 и 8 через адресный 4 и дополнительный нагрузочный 6 транзисторы, когда информационный транзистор 2 закрыт. . Вольт-амперная характеристика составной lt arpy3KH может быть представлена аналитически системой уравнения, описывающих вольт-амперные характеристики адресного 4 и нагрузочного 6 транзисторов. 1-2|Ёф-3 1|(и-ивь,,Ни-ив„ , 1(2-Е-иДЕ-и), I нормирована ие значение тока; F Ф Uo нормированное напряжение на затворе адресного и стоке нагрузочного транзистора гоотвеиственио; -нормированное .напряжение на истоке Hai-рузочногю транзисто-нормированное напряжение на истоке адресного транзистора. Из приведенных на фиг. 3 графиков следует, что при любых напряжениях на- , грузочная кривая в обеспечивает больший ток заряда, чем кривая S , следователв но,цредла1аемая ячейка имеет большее быстродейс-1-Biie, чем известный аналог. С целью увел1мепия помехозащишенносгги ячейки, транзисторы со всароенным каналом 5 и 6 можло включи ь ггжже между информациопиныкш 1 и 2 и адрес- I ными 3 и 4 транзисторами. В этом случае транзисторы со всгроеиным каналом И1|.1аю-с роль буф ггных, предотвращая прохи -деиие импульса с адресной шины 9 непсюредствепно па затворы ип формациопных грапзисторов. JI р е д м е т изобретения, ХЫиамическая ячейка памяти на ААДПтранзисторах, содержащая информаг.ионпые: транзисторы с индуцирован 1ым канал1)м, соединенные по схеме триггера, запоминающие конденсаторы, включенные между затвором и ис-гоком каждо1о ипформаииаи-.

Авторы

Даты

1975-07-25—Публикация

1973-02-01—Подача