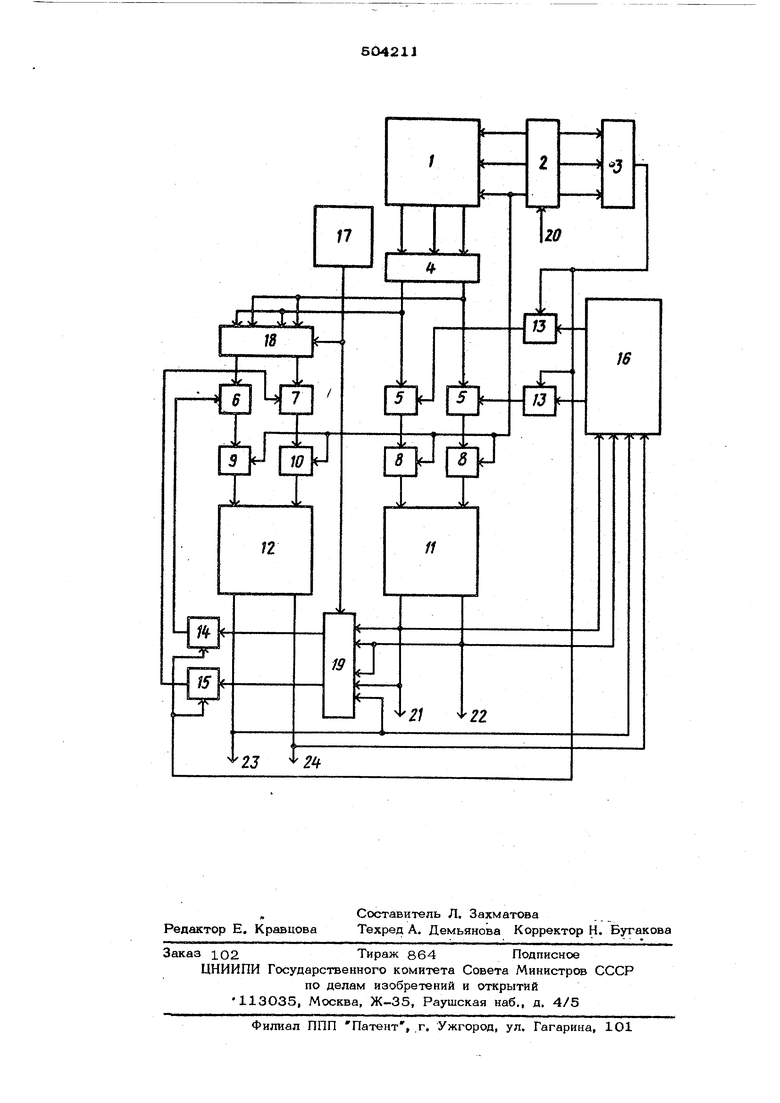

3 вторая группа схем сравненкя, соединенная «жоими входами с вызолами первого цифровкалогхжого преобразователя, а выходами со «ходами второй группы элементст И, вто|Юй чоммутатор, управляющий вход которого соединен с выходом блока управления, япформаиионны J входы соединены с вьсясдал в второго цифро-аналогового прюобразоаа- теля, а выходы - со входами второй группы схем сравнения, третий цифро-ан1.логовый шреобразоват«ль, входы которого соединены с выходами дополнительных логических схем ойределения направления приращений, соедивениых вторыми входами с вьЕходами триггврог двух младших разрядов регистра адреса, а выходы третьего цифро-аиалогового преобразователя - с информационными входами второго коммутатора и вь ходами аналогового вычислительного блока. Схема предложенной с стемы предст лена на чертеже. Она содержит эапоминаюш ни блок 1, регистр адреса 2, иифро-аналоговый преобразователь 3, усилит и считьтания 4, первую и вторую группы элементов 5, б и 7, логические схен«ы определения направления прирашения 8, 9, 1О, второй аифро-аналоговый преобразс«атель 11, третий цифроаналоговый преобразователь 12, схемы срав нения 13, 14 и 15, акалог жый вычислительный блок 16, блок управления 17, первый коммутатор 18 и второй коммут;;тор 19 вход 2 О регистра адреса 2. Входы запоминающего блока 1 соединены с выходами регистра адреса 2, другие выходы которого подктючены ко входам цифро-аналогового преобразователя 3, соединенного своим выходом со входами схем сравнения 13, другие входы которых подключены к выходам аналогового вычислител ного блока 16, входы которого соединены с выходами цифро-аналогсжого преобразователя 11. Первые входы логических схем опре деления направления приращения 8 соединены с выходами вентильных схем 5. Выходы триггеров двух младших разрядо регистра адреса 2 соединены со вторыми входами логических схем определения направлекир приращений 8, выходы которых соединены со входЯ и цифро-аналогового пр образсжателя 11. Выходы схем сравнения 13 соединены со входами вентильных схем 5, другие входы которых подключены к выходам усилителей считьтания 4, соединенных своими входа: .и с выходами запоминающего блока 1. Выход блока управления 17 соединен с управляющим входом первого коммутатора 18, информационные .входы которого подключены к выходам усилителей считьшания 4, и с управляющим входом второго ком

4 мутатора 19, ннформациомные входы которого подключены к выходам цифро-аналогового преобразсжателя 11. Между выходами первого коммутатора 18 н ВАОдами аналогсшого вычислительного блока 16 включены две цепочки включенных поаледова-гельно вентильной схемы 6 (7), логической схемы определения направления превращений 9 (Ю), цифро-аналогового преобразователя 12. Выходы второго коммутатора 19 с .хэдинёны с первыми входами схем сравнения 14 и 15, вторые входы которых соединены с выходом цифро-аналопжого преобраз(жателя о, а выходы схем сравнения 14 и 15 соединены со вторыми входами вентильных схем 6 и 7. Вторые входы логических схем определения направления прирашения 9 и 16 соединены с выходами триггеров двух младших разрядов регистра адреса 2, а вььход иифро-аналогового преобразователя 12 подключен к одному из информационных входов рторого коммутатора 19. Разрядность запоминающего блока 1 определяет количество нелинейных зависимостей, которые выдаются на выходы 21 .i 22, Кроме того, устройство позволяет реализовать сложные нелинейные зависимости первого (X)JH второго (X)| типов, при,чем функции f. f и 9 принадлежат множеству нелинейных зависимостей, записанных в запоминающек- блоке 1. Для реализации сложной зависимости первого типа необходимо с помощью первого коммутатора 1-8 подключить выход усилителя считывания 4, соответствующего функции Н , к первому входу вентиля 6 или 7, а один из выходов цифро-аналогового преобразователя соответствуюший функции f с помощью второго коммутатора 19 необходимо подключить к первому входу схемы сравнения 14 или 15. Тогда ф -ткция f(X) будет выступать в роли аргумента и на выходе 23 или 24 получится искомая нелинейчая зависимость первого типа Sff (X)j. При реализации сложной нелинейной зависимости второго типа необходимо с помошью второго коммутатора 19 выход пифро-аг-алогового преобразователя 11, на к ото,, ом получена нелинейная зависимость SL(X)j , подключить к первому входу схемы сравнения 15. При помоши первого коммутатора 18 выход усилителя 4, соответствующего функции т , подключается к первому входу вентиля 7. Теперь в роли аргумента выступает функцияЧ fCX)J , и на выходе 24 образуется I 1 J ч- f JI «. и.1 I yv - X .j л Iw- нелинейная зависимость второго , При наличии в запоминающем блоке 1 п. базовых нелинейных зависимостей предлагаемая система позволяет реализоватьn(Ti-2)-«fn видов разнообразных нелинейных зависимсхгтей. Формула изобретения Многоканальная система формирования сложных нелинейных зависимостей, содержащая запоминающий блок, входы которого соединены с выходами регистра адреса, другие выходы которого подсоединены ко входам пе вого цифро-аналбгоеого преобразователя, соединенного своим выходом со входами схем сравнения, другие входы которых подсоедине ны к выходам аналогового вычислительного блока, входы которого соединены с выходами второго цифро-аналогс ого преЬбразователя, выходы схем сравнения соединены со входами первой группы элементов И, логические схемы определения направления приращений, соединенные первыми входами с выходами первой группы элементов И, входы которой подсоединены к выходам усилителей считывания, соединенных своими входами с выходами запоминающего блока, вторыми входами логические схемы определения направления прирашений соединены с выходами двух младших разрядов регистра адреса, а выходами - со входами второг: цифро-аналогового преобразователя, отличаюшаяс я тем, что, с целью расширения функциональных возможностей, она содержит блок управления, первый коммутатор, управляюши) вход которого соединен с выходом блока .управления, а информационные входы - с выходами усилителей считывания, вторую группу элементов И, соединенную входами с выходами первого коммутатора, а ехода,ми - с первыми входами дополнительных (Логических схем определения направления 1приращений, схемы сравнения, соединенные ;своими входами с выходами первого цифроIаналогового преобразователя, а выходами - со входами второй группы элементов И, второй коммутатор, управляющий вход которого соединен с выходом блока управле:ния, информационные входы соединены с |выходами второго цифро-аналогового пре(Образователя, а выходы - со входами схем |сравнения, третий цифро-аналоговый пре- рбразсжатель, входы которого соединены |с выходами дополнительных логических схем определения направления прирашений, соеди ненных вторыми входами с выходами тригjrepOB дьух младших разрядов регистра ад:реса, а выходы третьего цифро-аналогово|го преобразователя с информационными входами второго коммутатора и входами аналогового вычислительного блока,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство возведения в дробную степень | 1973 |

|

SU596941A1 |

| Устройство для возведения в дробную степень | 1974 |

|

SU571812A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Цифро-аналоговая система для регистрации и статистической обработки информации | 1979 |

|

SU858023A1 |

Авторы

Даты

1976-02-25—Публикация

1973-04-09—Подача