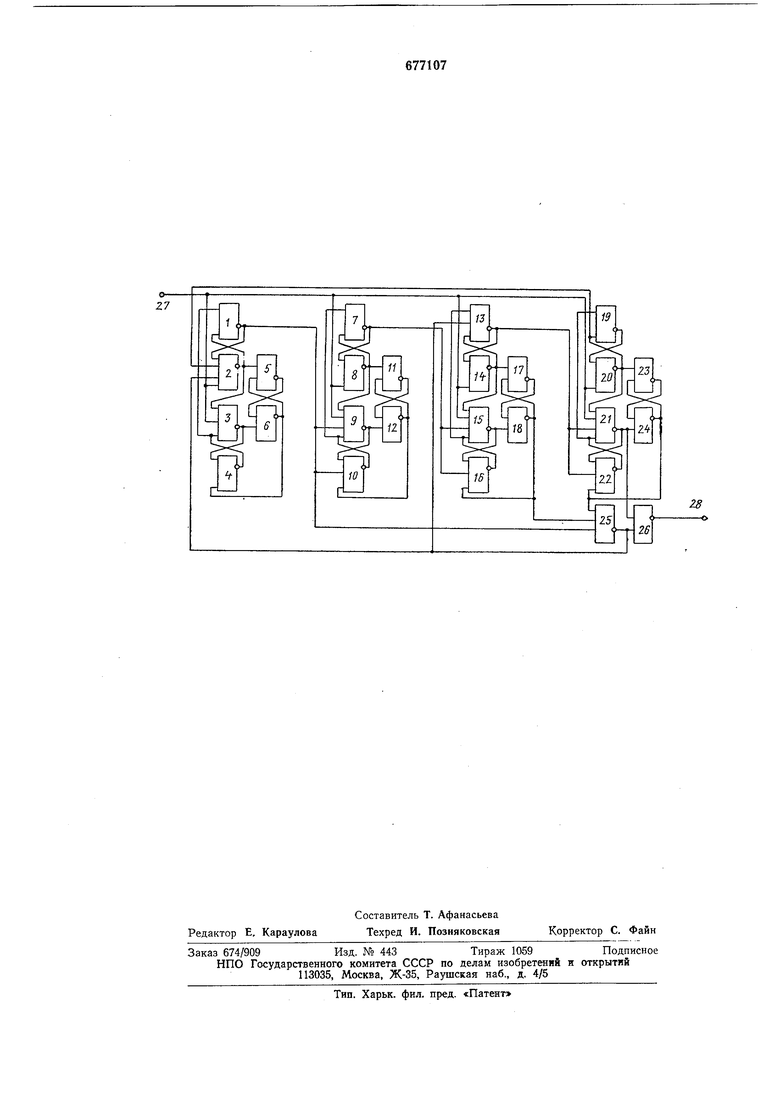

(54) БЫСТРОДЕЙСТВУЮЩИЙ СЧЕТЧИК И-НЕ 7-10, образующие аналогично коммутационные триггеры, элементы И-НЕ 11, 12, образующие триггер памяти второго разряда, элементы И-НЕ 13-18, образующие триггеры третьего разряда, элементы И-НЕ 19-24, образующие триггеры четвертого разряда, первый элемент И-НЕ 25, второй элемент И-НЕ 26, щину 27 тактирующего сигнала, выходную щину 28 устройства. Счетчик работает следующим образом. В исходном состоянии триггеры памяти первых двух разрядов находятся в единичном состоянии, триггеры памяти третьего и четвертого разрядов в нулевом состоянии. Под действием тактирующего сигнала в счетчике осуществляется обычный пересчет поступающих импульсов в двоичном коде. При этом осуществляется следующая последовательность смены состояний триггеров памяти: Видно, что с приходом пятого по счету тактирующего сигнала на выходе элемента И-НЕ 21 появляется сигнал, равный логическому нулю, который устанавливает триггер памяти четвертого разряда в единичное состояние и который через элемент И-НЕ 26 поступает на выходную щину 28 устройства. Далее осуществляется обычный пересчет поступающих импульсов и с приходом десятого импульса в счетчике устанавливается код 1101. После окончания действия десятого импульса на выходе элемента И-НЕ 1 появляется сигнал, равный логической единице, следовательно открывается элемент И- НЕ 25 и на его выходе появляется сигнал, равный логическому нулю, который через элемент И-НЕ 26 поступает на выходную щину 28 устройства. Одновременно сигнал, равный логическому нулю, с выхода элемента И-НЕ 25 поступает на входы элементов И-НЕ 2 и 13, при этом на выходе элемента И-НЕ 13 появляется сигнал, равный логической единице. С приходом одиннадцатого по счету тактирующего импульса открываются элементы И-НЕ 9, 14, 20 на выходе этих элементов появляются сигналы, равные логическому нулю, которые устанавливают триггеры памяти второго разряда в единичное состояние, а триггеры памяти третьего и четвертого разряда - в нулевое, элемент И- НЕ 25 закрывается и прекращается формирование выходного сигнала. Триггер памяти первого разряда свое состояние не изменяет, поскольку элемент И-НЕ 2 остается закрытым сначала сигналом, равным логическому нулю с выхода элемента И-НЕ 25, а затем сигналом с выхода элемента И-НЕ 20. После окончания действия тактирующего сигнала схема возвращается в исходное состояние 001I. Таким образом, на 11 входных импульсов схема выдает два выходных, т. е. происходит деление частоты на 5,5 причем выходные сигналы формируются через равные интервалы времени. Кроме того, счетчик позволяет осуществить деление частоты на П. Выходным сигналом при этом будет сигнал с выхода элемента И-НЕ 21 или 25. Формула изобретения Быстродействующий счетчик по авт. св. № 444330, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в него введены элементы И-НЕ, первый вход первого из которых подключен к единичному выходу второго коммутационного триггера первого разряда, второй вход к единичному выходу триггера памяти третьего разряда, третий вход - к единичному выходу триггера памяти четвертого разряда, а выход - к нулевому входу второго коммутационного триггера первого разряда, к единичному входу второго коммутационного триггера третьего разряда и к первому входу второго элемента И-НЕ, второй вход которого соединен с нулевым выходом первого коммутационного триггера четвертого разряда, при этом нулевой выход второго коммутационного триггера четвертого разряда подключен к нулевому входу второго коммутационного триггера первого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель частоты на 4,5 | 1977 |

|

SU677106A1 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

Авторы

Даты

1979-07-30—Публикация

1977-04-01—Подача