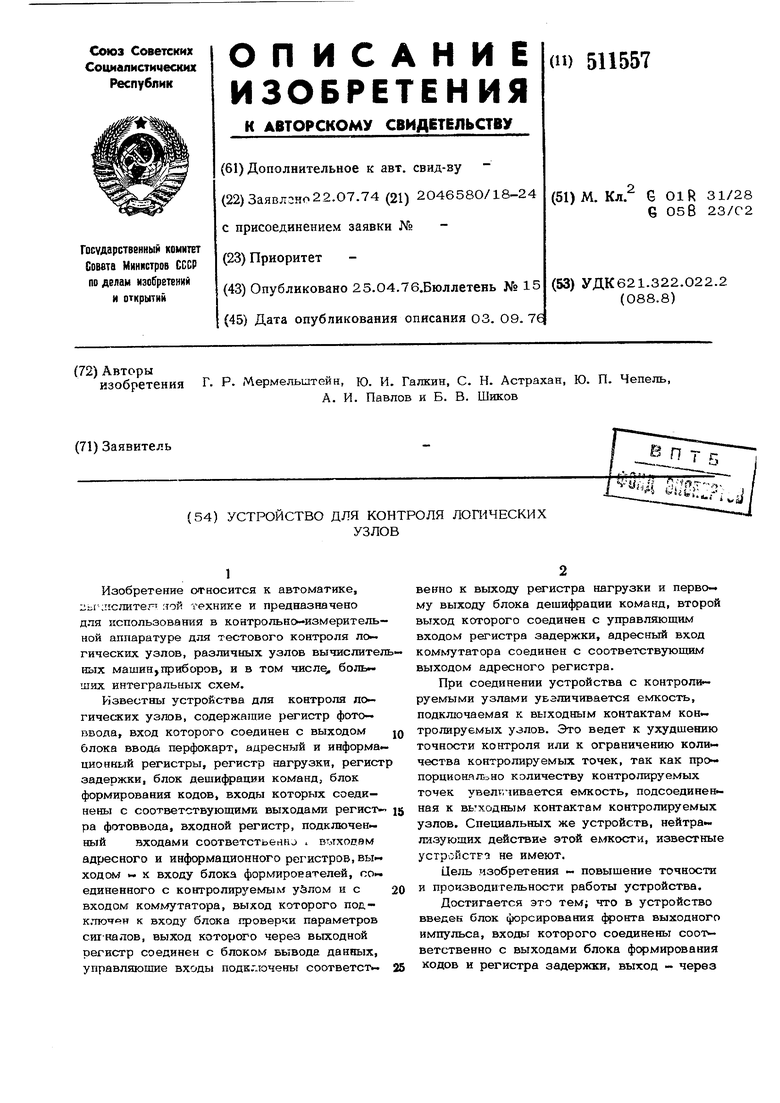

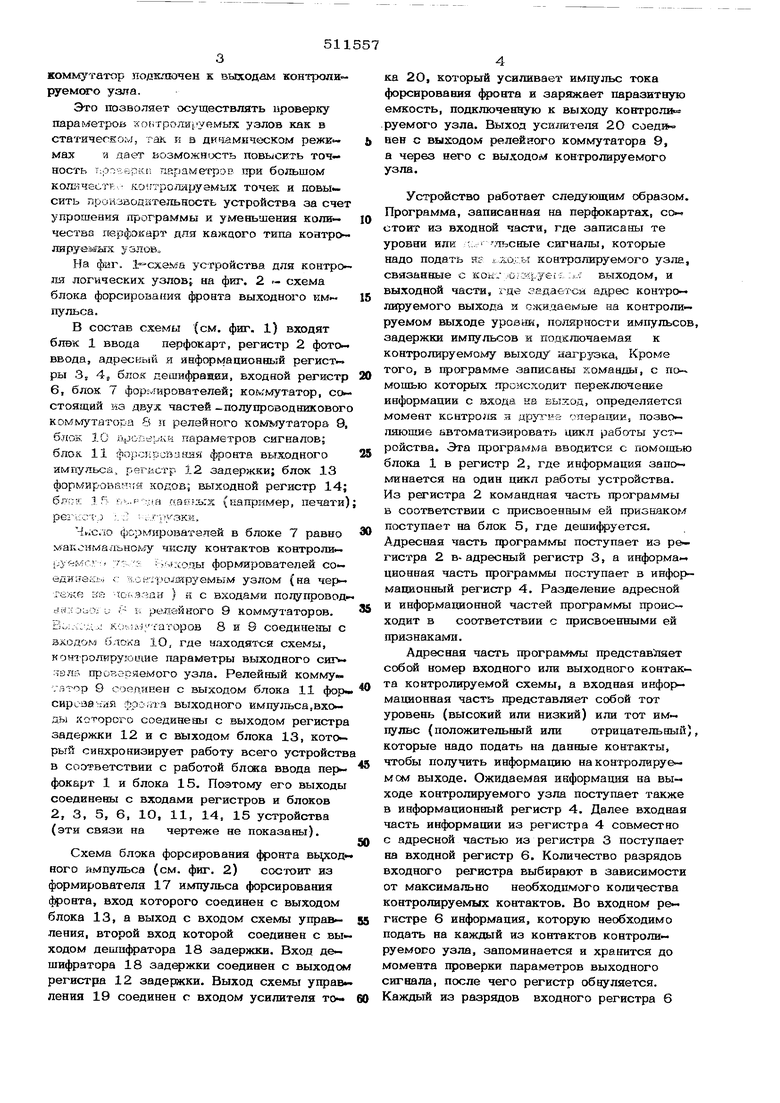

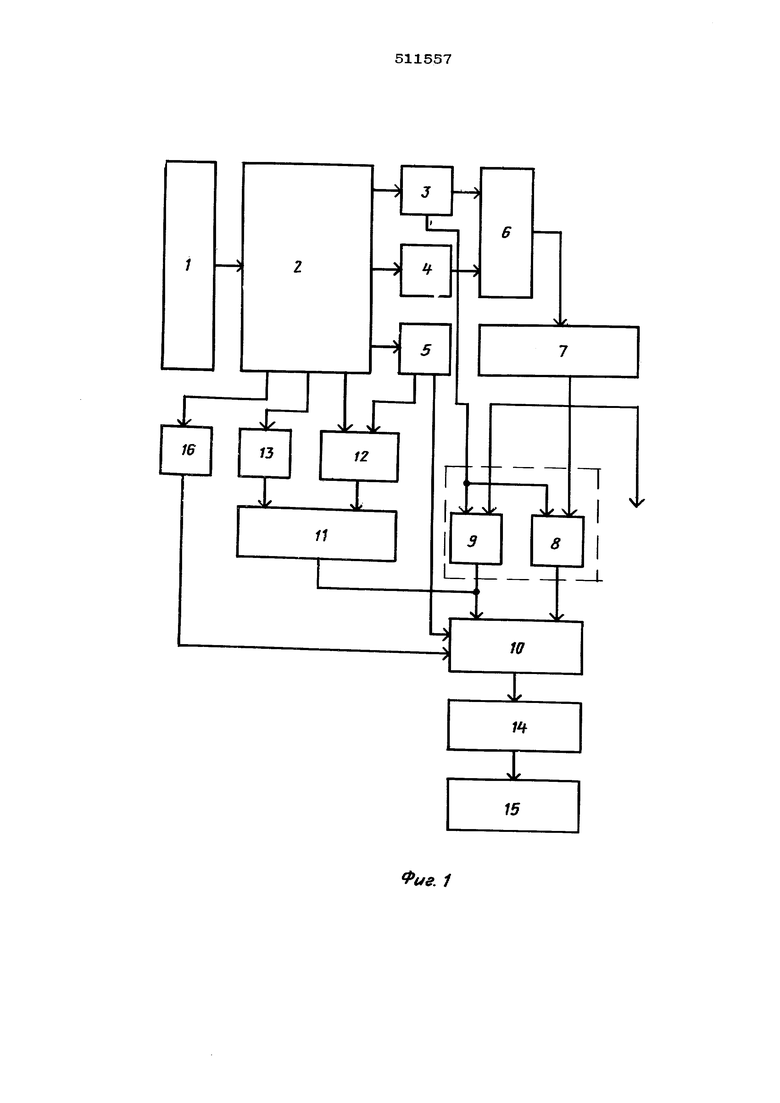

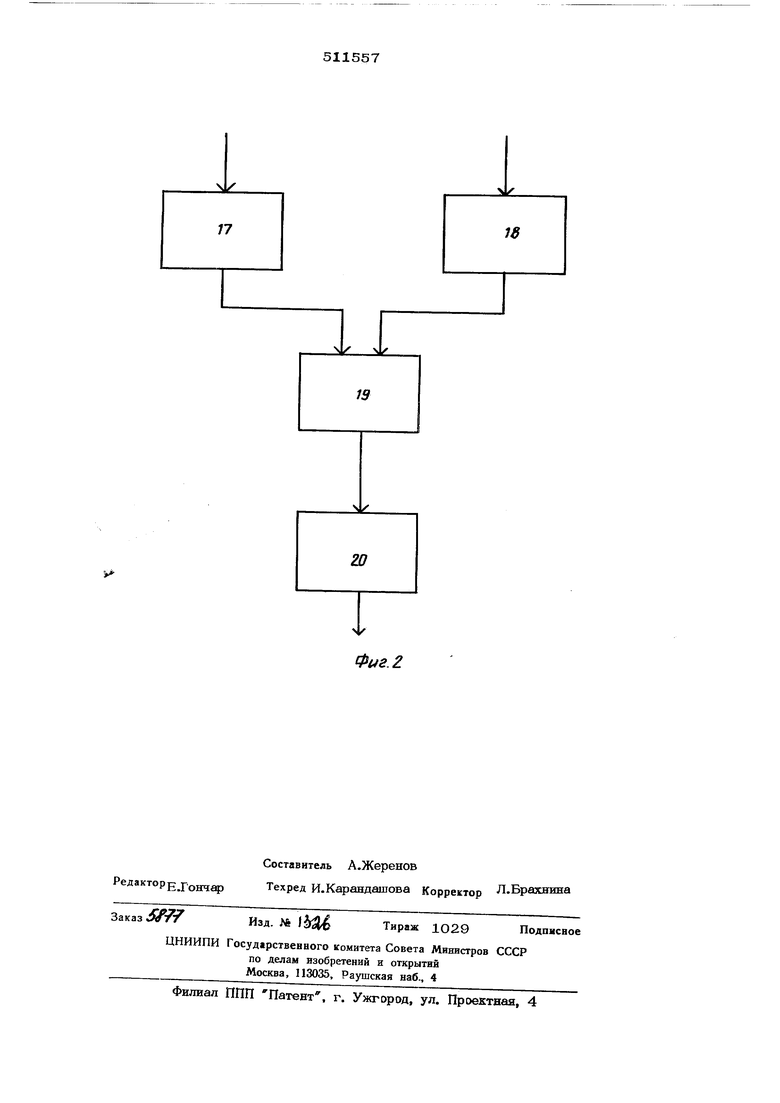

511 коммутатор подключен к выходам контролируемого узла. Это позволяет осуществлять проверку параметров контролируемых узлов как в статическом, гак и а дичамическом режЕ- мах я дает возможн(х:ть повысить точность Tip-rs-epKii параметров при большом кошзчеств.- ко .гтроляруемыж точек и повы. сить пракзвоцйтельность устройства за счет упрошеаия программы и уменьшения коли- чества перфокарт для кажцого типа коатрсьлируемьгх узлов. На фиг. 1«-схема устройства для контро ля логических узлов; на фиг. 2 « схема блока форсирования фронта выходного им пульса. В состав схемы (см. фиг. 1) входят блэк 1 ввода перфокарт, регистр 2 фото« ввода, адрескь|й я инфop faциoннь;й регист- ры 3, 4j блож дешифраиЕи, входной регистр 6, блок 7 фор: трователей; коугмут-атор, со стоящий из двух частей -полупроводникового KOiVFNfyTaropa i н релейного коммутатора 9, блок 10 ti, параметров сигналов; блок 11 форсиройзлгия фронта выходного имг1ул,ьса, регистр 12 задержки; блок 13 форьл-ировая;:гя кодов; выходной регистр 14; бл«я; 15 f,i...;ia давгых (капример, печати) pei4LC -j :-:: ; .г гузка. 4irXiio формирователей в блоке 7 равно макоимальноьгу числу контактов контроли« jyvftMCA; ;7;.:- (j-vxo.abi формирователей со- едияек;;.. с «.о(.ро я руемым узлом (на ,:G ье то .з.заи ) и с входами полупровод« релейного 9 коммутаторов. tiи ::.;.:,. .К:;ил : гаторов 8 и 9 соединены с входом блока 1О, где находят-ся схемы, контролирующие параметры выходного сиг- проваряемого узла. Релейный коммутатор 9 соединен с выходом блока 11 фор сирс-за-гйя фроата выходного импульса,входы которого соединены с выходом регистра задержки 12 и с выходом блока 13, который синхронизирует работу всего устройств в соответствии с работой блсжа ввода пер)- фокарт 1 и блока 15. Поэтому его выходы соединены с входами регистров и блоков 2, 3, 5, 6, 10, 11, 14, 15 устройства (эти связи на чертеже не показаны). Схема блока форсирования фронта ного импульса (см. фиг. 2) состоит из формирователя 17 импульса форсирования фронта, вход которого соединен с выходом блока 13, а выход с входом схемы управ- ления, второй вход которой соединен с выходом дешп(}чэатора 18 задержки. Вход дешифратора 18 соединен с выходом регистра 12 задержки. Выход схемы управ. ления 19 соединен с входом усилителя то ка 20, который усиливает импульс тока форсирования и заряжает паразитную емкость, подключенную к выходу контроле руемого узла. Выход ycв:JШтeля 20 соед1 нен с выходом релей sroro коммутатора 9, а через него с выходом контролируемого узла. Устройство работает следующим образом. Программа, записанная на перфокартах, состоит из входной части, где записаны те уровни или v:, льсные сигналы, которые надо подать яе ,.хо,;:,ы контралнруемого узла, связанные с кокг-Ю/и -уе; ;,;;..: выходом, и выходной части, где эндается адрес контролируемого выхода и ожидаемые на контролируемом выходе уровни, полярности импульсов, задержки импульсов и подключаемая к контролируемому выходу нагр5 зка, Кроме того, в программе записаны команды, с по- мощью которых происходит переключение информации с входа ка выход, определяется момент контроля; н дрзтч е операции, позволяющие автоматизировать цикл работы устройства. Эта программа вводится с помощью блока 1 в регистр 2, где информация запоминается на один цикл работы устройства. Из регистра 2 командная часть программы Б соответствии с присвоенным ей признаком поступает на блок 5, где дешифруется. Адресная часть программы поступает из регистра 2 в-адресный регистр 3, а информационная часть программы поступает в информационный регистр 4. Разделение адресной и информационной частей программы происходит в соответствии с присвоенными ей признаками. Адресная часть программы представляет собой номер входного или выходного контакта контролируемой схемы, а входная инфор мационная часть представляет собой тот уровень (высокий или низкий) или тот им- пулвс (положительный или отрицательный), которые надо подать на данные контакты, чтобы получить информацию на контролируемом выходе. Ожидаемая информация на выходе контролируемого узла поступает также в информационный регистр 4. Далее входная часть информации из регистра 4 совместно с адресной частью из регистра 3 поступает на входной регистр 6. Количество разрядов входного регистра выбирают в зависимости от максимально необходимого количества контролируемых контактов. Во входном регистре 6 информация, которую необходимо подать на каждый из контактов контролируемого узла, запоминается и хранится до момента проверки параметров выходного сигнала, после чего регистр обнуляется. Каждый из разрядов входного регистра 6 представляет собой память на тригтерных схемах. Каждый раарзвд расчитан на хранени определенного количества бит информашш, Спрзр.ел5юмого количеством уровней и У1М пульсов, которые необходимо подать на входные контакты контролнруемого узла д,:;я liposepEH. проверки комбинаци онЕЫ схем необходимо подавать на входны коктакты два уровня и один импульс, для проверки трштерных схем в динамическом режиме необход 1МО|кроме основного (глав й:м-о; ИМтгугаэса,подавать еще и задержал. лс.; стдссктелЕ г-то главного импульс для проверки счетчиков в динамическом режиме необходимо три сдвинутых относительно друх друга имяульса. Кроме того, каждый из может быть любой полярности Все зто количество типов информаш1и опре- друшет емхость одного разряда входного регистра в, который управляет работой бло 7формирователей. Количество последних в нем также равпо максимально-возможном кс ш-5частв5- контактов контролируемого узла И «формация в виде сформированных уровней ияй импульсов с выхода формирователей блока 7 поступает навходы контролируемого узла. С помощью формирователей блока 7 и репейного комк утатора 9 проис- 5 соотзетствии с программой азтома ческзя коммутация входных и выходных контак- ов. Если данный контакт контролируемого узла является входным, то подсоединенный к нему формирователь вырабаты вает информацию, определяемую входным регистром 6. а разряд релейного коммутат рл, пойСэединенный к этому же контакту отключее.г измерительные схемы от него. ЕСШ-: хе контролируемый контакт является Бытсодмым, ТО релейнькй комьлутатор 9 под кпточает этот контаг т к контрольйьтм схе- мам блока 1О, а формирователь блока 7, подсоединеЕ 1а 1Й к этому контакту, отключается от него. Посло; того как во вхоаной регистр 6 KB& jeaJ. jjrHMeCKiieкомбинации и в соот« д:.этс,ь,;; . :-jiuM формирователи блока 7 is€;j.-.ajj-H 3T(v комбинации ка входы контро- ,::.. .-;л-мгс у.:;ла тчинается выходная часть : , :.::/---pa-z также состонт из адресной - , мацйовкой частей. Адресная часть -ес-та тюступает в адресный регистр 3, пг вз-1г:-ош.ий работой полупроводниковог 8и pejieUKoro 8 коммутаторов. Последний ь соет-ветствии с записанным в программе ;оитро,)л :руеглым выполним контактом, подccsfis-icyv аго ic блоку 1О, в котором нахс;дттс:я схэмы, контролируюшке уровни и оялернслу выходного сигнала. Инх{юрмацион- пая часть выходного теста, записанная на перфокарте, представляет собой ожидав- мые аа выходе контролируемого узла уровень (высокий или низкий) или полярность импульса ( положительного или отрица. ельного). Кроме того, информационная часть содержит ожидаемую задержку н величину необходимой нaгrJyзки, которую необходимо подключить к контролируемому выходному контакту. Ожидаемые величины вга- грузки и задержки регистра фотоввода 2 поступают на входы регистра 16 нагрузки и регистра 12 задержки соответственно. Выходы этих регистров управляют выбором ожидаемой нагрузки и задфзкки. Выбранная нагрузка подсоединяется к контролируемому выходному контакту. Одноврюменно регистр12 задержки управляет работой блока 11 форсирования (JpoffTB выходного импульса контролируемого узла. Работа этого блока поясняется с помощью схемы, изображенной аа фиг. 2. На фход формирователя 17, фор сируюшего иКгаульсы, поступает от блока 13 импульс, начинающийся несколько раньше импульса, подаваемого ва вход контролиру емого узла, и длительностью, тфевышаюшей максимально возможную величину задержки на которую рассчитьгеается устройство. Таким образом, независимо от задержки контролируемого узла импульс, поступающий на вход формирователя 17, перекрывает импульс на выходе контролируемого узла. Формирователь 17 создает ряд коротких импульсов длительностью но перекрывающих друг друга. С выхода формирователя 17 эти импульсы поступают на вход схемы управления 19. Второй вход схемы управлешш 19 соединен с выходом дешифратора 18, который весь диапазон возможной задержки импульса ковстролируе- мого узла разбивает на отрезки, равные длите;ъностям импульсов, сформированных схемой формирователя 17. В соответствии с ожидаемой задержкой дешифратор 18 выбирает один из отрезков этой задержки, благодаря чему схема управления 19 пропускает только один сформированный формирователем 17 импульс, временное положение которого соответствует фронту выходного импульса контролируемого узла. Далее этот импульс поступает на импульсный усилитель тока 2О, который во время импульса контролируемого узла формирует импулБс тока, заряжающий парвк зитную емкость, вносимую подсоединением устройства контроля к контролируемому узлу. После выполнения выходной части теста, которая подготавливает контролирующие схемы и подсоединяет с помопсью релейного коммутатора 9 эти схемы к выкод- ному контакту контролируемого узла, а перфокарты в ригистр фотоввода 2 и далее

в блок 5J поступает команда измерение . Эта комавда в блоке 5 дешифруется и поступает в качестве разрешающего сигнала в блок 10, где контролирующиесхемы

производят сравнение параметров сигнала с выхода контролируемого узла с заданны ми (ожидаемыми) параметрами. Эти схемы в случае отклонения параметра сигнала от ожидаемых фиксируют ошибку, которая поступает с выхода блока 1О на вход выходного регистра 14, где она запоминается. Далее цикл работы устрой- ства повторяется до момента выполнения определенного числа измерений или до смены выходного адреса. После этого с

выхода выходного регистра накопленные ошибки в виде кода ошибок поступают на блок 15 вывода для печати вместе с номером выходного контакта. Формула изобретения

Устройство для контроля логических узлов,содержащее регистр фотоввода, вход которого соединен с выходом блока ввода перфокарт, адресный и информацион. ный регистры, регистр нагрузки, регистр задержки, блок деши эации команд, блок

формирования кодов, входы которых соединены с соответствующими выходами регистра фотоввода, входной регистр, подключенный входами соответственно к выходам адресного и информационного регистров, выходом - к входу блока формирователей, соединенново с контролируемым узлом и со входом коммутатора, выход которого подключен к входу блока проверки параметров сигналов, выход которого через выходной регистр соединен с блоком вывода данных, управляющие входы - подключены соответственно к выходу регистра нагрузки и первому выходу блока дешифрации команд, второй выхог ссторого соединен с управляющим входом регистра задержки, адресный вход коммутатора соединен с соответствующим выходом адресного регистра, отличающее- с я тем, что, с целью повыи1ения точ;.с.-. сти и производительности работы устройства, в него введен блок форсирования фронта выходного импульса, входы которого соединены соответственно с выходами блока формирования кодов и регистра задержки, выход через коммутатор подключен к выходам контролируемого узла.

I

JZ

16

13

11

г:

i

1

f N

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1166120A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

. /

77

1в

Фиг. г

Авторы

Даты

1976-04-25—Публикация

1974-07-22—Подача