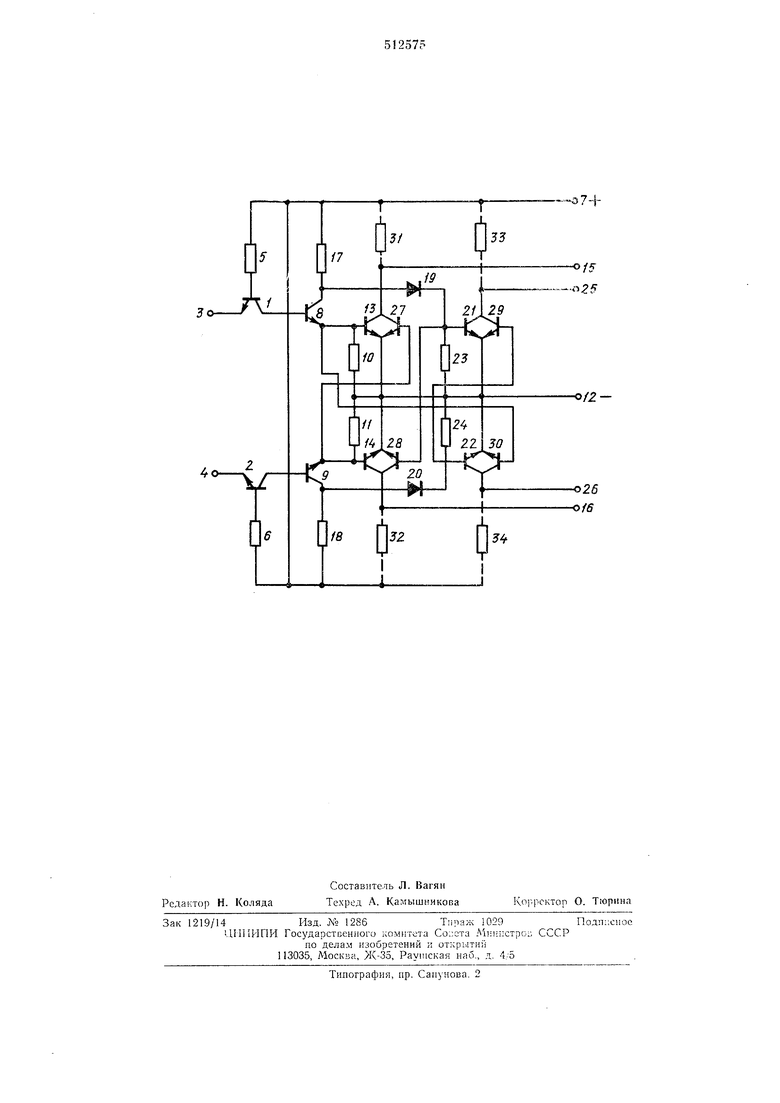

ложительной шине 7, а через диоды 19 и 20 к базам вторых инвертирующих транзисторов 21 и 22, базы которых соответственно через резисторы 23 и 24, а эмиттеры непосредственно, подключены к отрицательной шипе 12; коллекторы транзисторов 21 к 22 являются выходами дешифратора 25 и 26. Коллекторы и эмиттеры дополнительных инвертируюш,их транзисторов 27, 28, 29 и 30 подключены соответственно к коллекторам и эмиттерам транзисторов 13, 14, 21 и 22, а базы транзисторов 27, 28, 29 и 30 соединены соответственно с базами транзисторов 14, 21, 22 и 13. Между выходами дешифратора 15, 16, 25 и 26 и положительной шиной 7 включены нагрузочные резисторы 31, 32, 33 и 34.

Двухканальный дешифратор работает следуюш,им образом.

Ко входам 3 и 4 приложен высокий уровень потенциала. Током через резистор 5 открывается транзистор 8 и суммарным током через резисторы 5 и 17 - транзисторы 13 и 30. Аналогично током через резисторы 6 и 18 второго канала открываются транзисторы 14 и 27. Транзисторы 21, 22, 28 и 29 в этом случае закрыты, так как напряжение на коллекторах насыш,енных транзисторов 8 и 9 составляет и его недостаточно для открывания через диоды смещения 19 и 20 инвертирующих транзисторов 21, 22, 28 и 29. Поэтому на выходах 15, 16 и 26 устанавливается низкий, а на выходе 25 - высокий уровень потенциала.

Если на один из входов, например, на вход 3, подать низкий уровень потенциала, то коллекторным током транзистора 1 закрывается транзистор 8 и инвертирующие транзисторы 13 и 30, а ток, протекающий через резистор 17 и диод 19 поступает в базы транзисторов 21 и 28, вызывая их насыщение. При данном сочетаНИИ сигналов на входах 3 и 4 на выходах 15, 16 и 25 окажется низкий, а на выходе 26 - высокий уровень потенциала. При любых комбинациях сигналов на входах только на одном выходе будет высокий уровень потенцияла, и при выборе одной схемы из четырех необходим один логический вход в управляемой схеме. При применении дешифратора без промежуточной дешифрации на двух из его четырех входов будет высокий, а на двух других - низкий уровень потенциала, и в каждой управляемой схеме необходимо иметь два логических входа. При применении двух дешифраторов для дешифрации шестнадцати схем в первом случае в каждой схеме должно быть два, а во втором - четыре логических входа в каждой дешифрируемой схеме. Т. е. применение дешифраторов с промежуточной дешифрацией позволяет вдвое уменьшить количество логических входов дешифрируемых схем.

Формула изобретения

Двухканальный дешифратор, содержаший в каждом из двух каналов входной транзистор, база которого через резистор соединена с положительной шиной источника питания, эмиттер подключен к входной шине, а коллектор- к базе переключающего транзистора, коллектор которого соединен с анодом диода и через резистор с положительной шиной источника питания, а эмиттер - с базой первого инвертирующего транзистора и через резистор с отрицательной шиной источника питания, к которой также подклЕОчен эмиттер и через резистор база второго инвертирующего транзистора, о т л и ч а ю щ и и с я тем, что, с целью новышения быстродействия, в каждый из двух каналов дешифратора введены первый и второй дополнительные инвертирующие транзисторы, эмиттеры которых подключены к эмиттерам, а коллекторы - к коллекторам соответствующих инвертирующих транзисторов, причем база первого дополнительного инвертирующего транзистора первого канала подключена к базе первого инвертирующего транзистора второго канала, база первого дополнительного инвертирующего транзистора второго канала - к базе второго инвертирующего транзистора первого канала, база второго инвертирующего транзистора второго канала - к базе второго дополнительного инвертирующего транзистора первого канала, база первого инвертирующего транзистора первого канала - к базе второго дополнительного инвертирующего транзистора второго канала, а катоды диодов первого и второго каналов подключены соответственно к базам вторых инвертирующих транзисторов.

. о

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1975 |

|

SU547968A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Логический элемент | 1984 |

|

SU1261105A1 |

| Логический элемент | 1988 |

|

SU1529441A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Инвертор | 1976 |

|

SU661804A1 |

20

-о2б -0/5

о

54

Авторы

Даты

1976-04-30—Публикация

1974-11-15—Подача