УСТРОЙСТВО для ВЫЧйС,аЕН1-1Я КВАДРАТНОГО

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для ограничения чисел | 1978 |

|

SU767758A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для вычисления суммы произведений | 1985 |

|

SU1269125A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для кусочно-линейной интерполяции функций | 1983 |

|

SU1215117A1 |

| Цифровое устройство ограничения числа по модулю | 1977 |

|

SU690477A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

Изобретение относится, к зьлчислктеаьHoii технике и предназначено для использования в вычйслительыых машинах, работающих в реальном масшткбз времени.

Известны устройства для вычисления квадратного корня J1 .содержащие регистрры,сумматоры накопительного типа, счет- чих циклив, .иогическке элементы и схемы сдвига до гп разрядов включительно. В тэ- ккх устройствах используется асинхронный алгоритм, позволяюший для некоторых кодовых сочетаний подхорснного выражения достичь существенного повышения быстродействия. Однако, для целого ряда кодов э({х|зек7Ч1Вйость этого алгоритма значительно снижается и в пределе бысг1зодейсгвие указанных устройств может равняться быстродействию устройств, использующих синхронные (с жестко зафиксированным для требуемой точности число г шаг-ов вычисления) ал оритмы.. Кроме того, для этого алгоритма существует необходимость анализа групп разрядов остатка, что приводит к дополнительному расходу оборудования, и.

как следегвпо, снижению надежности и технологичности устройства в делом.

HaH6ejiee близким чо технической c mностн .к данному изобретению яьляеся усгройство L -. использующее синхронный алгоритм и co/jep/xaiuee сумматор-накопитель, регистр, триггер, регистр сдвига результата, блок управления, два элемен- та и, выход регистра соединен с первыт.-:

входом сумматора-накопителя, выход которого соединен со входом триггера, вылод которого соединен с первым входом блока управления, с первым входом первого элемента И, с первым входом второго элел1ента И и вторы.м входом сумматора-накопителя, третий вход которого соединен с выходом блока управления, второй вход которого соединен с выходом регистра сдвига результата. Схема такого устройства срав-нительно сложна и, следовательно, велики аппаратурные затраты.

Иель изобретения - упрощение устройства.

Это достигается тем, что устройство содержит блок коррекции, первый выход которого соединен со вторым входом второго элемента И, выход которого соединен с четвертым входом сумматора-накопителя, пятый вход которого соединен со вторым выходом блока коррекции, а шестой вход сумматора-накопителя соединен с третьим выходом блока коррекции и вторым входом первого элемента И, вы.ход которого соединен со входом регистра сдвига результата.

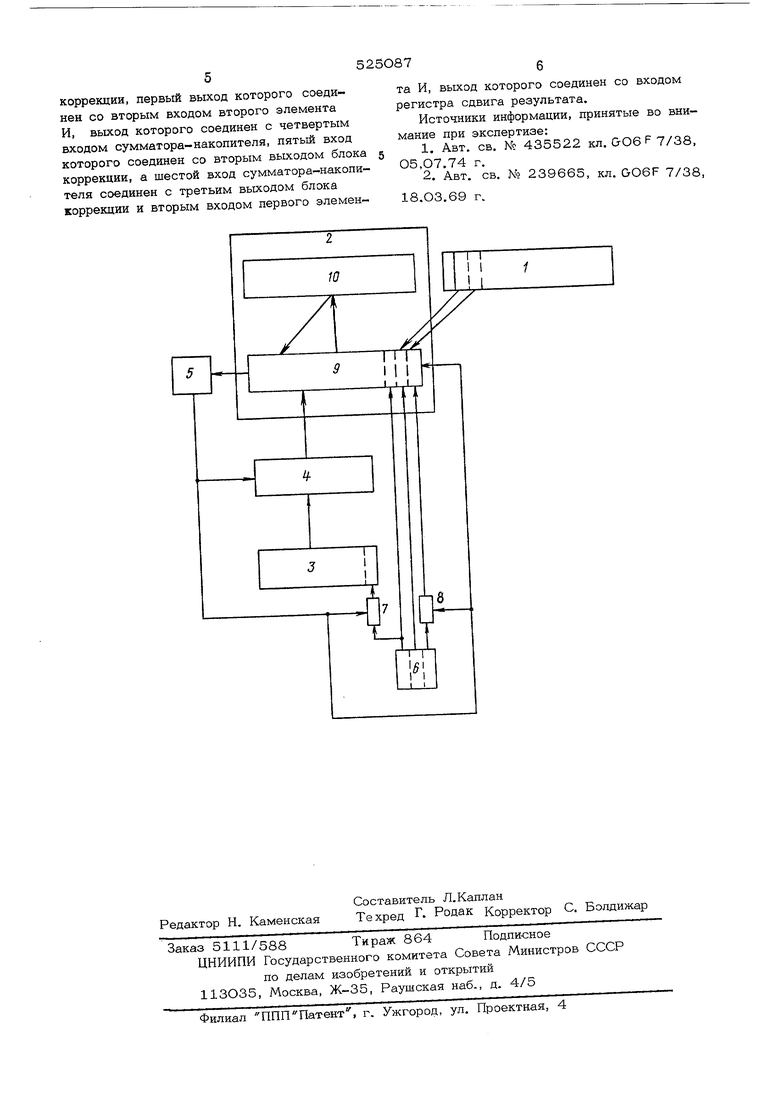

На чертеже изображена схема устройства.

Устройство содержит регистр 1, сумматор-накопитель 2, регистр 3 сдвига результата, блок управления 4, триггер 5 и блок коррекции 6, элементы И 7, 8.

Сумматор-накопитель 2 состоит из комбинационного сумматора 9 и накопителя 10. Сумматор 9 предназначен для работы, с числами лредставленными в дополнительном коде. Режим работы сумматора определяется состоянием триггера 5 знакового разряда. Выход триггера 5 подключен к управляющим входам блока управления 4 и цепи переноса в младший разряд сумматора 9.

Нулевое состояние триггера 5 для комбингщионного сумматора 9 соответствует режиму Вычитание. В этом случае код вычитаемого при прохождении через блок управления 4 инвертируется, а в цепи переноса в младший разряд комбинационного сумматора 9 формируется сигнал наличия переноса. Если триггер 5 находится в состоянии 1, что соответствует для комбинационного сумматора 9 режиму Суммирование, то через блок управления 4 на комбинационный сумматор поступает прямой код второго слагаемого и на входе младшего разряда комбинационного сумматора 9 сигнал переноса отсутствует.

Перед началом вычисления подкоренное выражение находится в регистре 1. Накопитель 1О, регистр 3 сдвига результата и триггер 5 обнуляются, а в блок коррекции 6 заносится код 111. В соответствии с этим в первом шаге вычислений осуществляется режим Вычитание.

Два младших разряда уменьшаемого поступают на вход комбинационного сумматора 9 из двух старших разрядов регистра 1, на остальные разряды поступает информация с накопителя 1О со сдвигом на два разряда влево. Обратный код вычитаемого передатся в сумматор с регистра сдвига результатов и с младшего разряда блока коррекии 6, информация с двух других его разядов подается в сумматор без инвертиования. Результат вычисления фиксируетя в накопителе Ю. По окончании первого шага вычислений вьшолняется сдвиг содержимого регистра 1 на два разряда влево, а регистра сдвига результата 3 на один разряд влево, при этом в младши разряд регистра 3 через блок управления 4 заносится содержимое старшего разряда блока коррекции 6, после чего этот разряд обнуляется и до окончания вычислений в блоке коррекции 6 хранится постоянный ко ОН. В триггер 5 заносится информация со знакового разряда комбинационного сумматора 9. С этого момента устройство готово к вьшолнению второго шага вычислений.

Далее вьшолнение операции в каждом шаге сводится к следуюш;ему:

передача содержимого накопителя 1О в комбинационный сумматор 9 со сдвигом на два разрада влево, в два разряда записывается информация из двух старших разрядов регистра 1 соответственно;

передача в сумматор содержимого регистра сдвига результата 3 и блока коррекции 6;

суммирование (вычитание);

запись результата суммирования (вычитания) в накопитель Ю, а информации из знакового разряда комбинационного сумматора 9 на триггер 5;

сдвиг содержимого регистра 1 и 3, при этом в младший разряд регистра 3 заносится очередной разряд результата.

По окончании последнего шага вычислений в регистре сдвига результата находится результат вычислений.

Использование данного изобретения позволяет упростить схему устройства и, следовательно, аппаратурные затраты при его пр оизводстве.

Формула изобретения

Устройство для вычисления квадратного корня, содержашее сумматор-накопитель, регистр, триггер, регистр сдвига результата, блок управления, два элемента И, выход регистра соединен с первым входом сумматора-накопителя, выход которого соединен со входом триггера, выход которого соединен с первым входом блока управления с первым входом первого элемента И, с первым входом второго элемента И и вторым входом сумматора-накопителя, третий вход которого соединен с выходом блока управления, второй вход которого соединен с выходом регистра сдвига результата, отличающееся тем, что, с цель упрощения устройства, оно содержит олок

коррекции, первый выход которого соединен со вторым входом второго элемента И, выход которого соединен с четвертым входом сумматора-накопителя, пятый вход которого соединен со вторым выходом блока коррекции, а шестой вход сумматора-накопителя соединен с третьим выходом блока коррекции и вторым входом первого элемента И, выход которого соединен со входом регистра сдвига результата.

Источники информации, принятые во внимание при экспертизе:

А

III

Авторы

Даты

1976-08-15—Публикация

1974-10-28—Подача