счет снижения величины тока записи в информационных шинах.

Это достигается тем, что в запоминающем элементе база первого транзистора соединена с коллекторами третьего и пятого транзисторов и с второй шиной питания, а база второго транзистора - с коллекторами четвертого и шестого транзисторов и с третьей шиной питания.

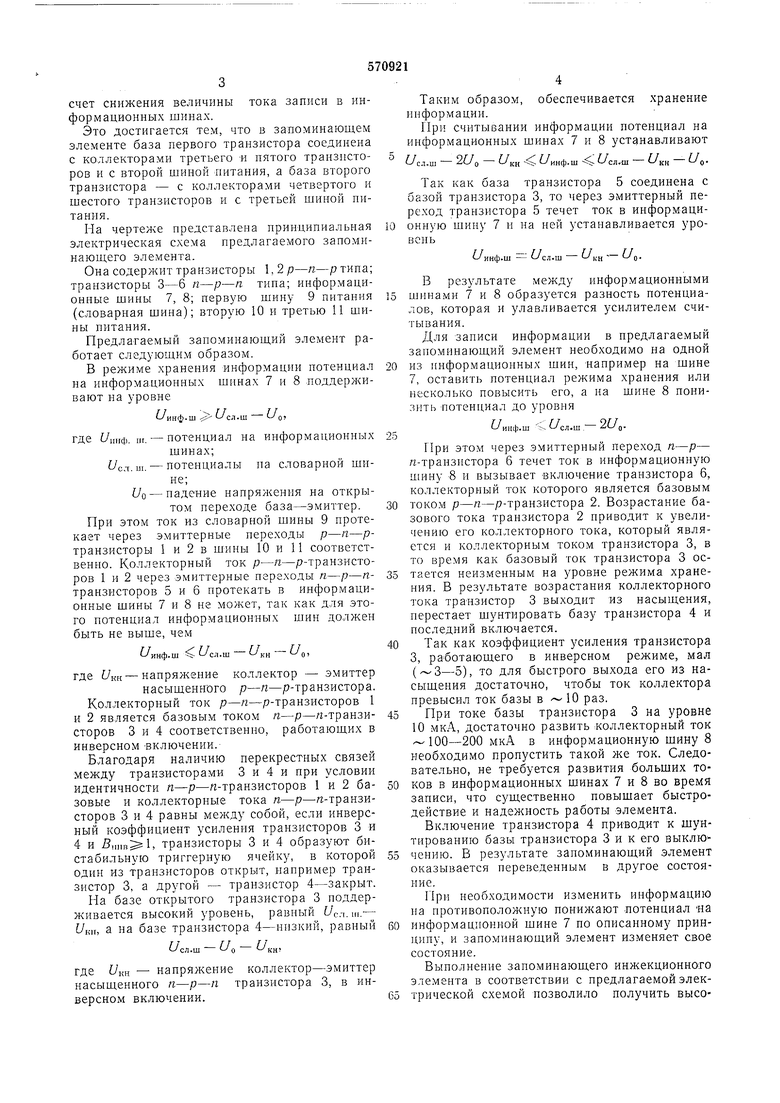

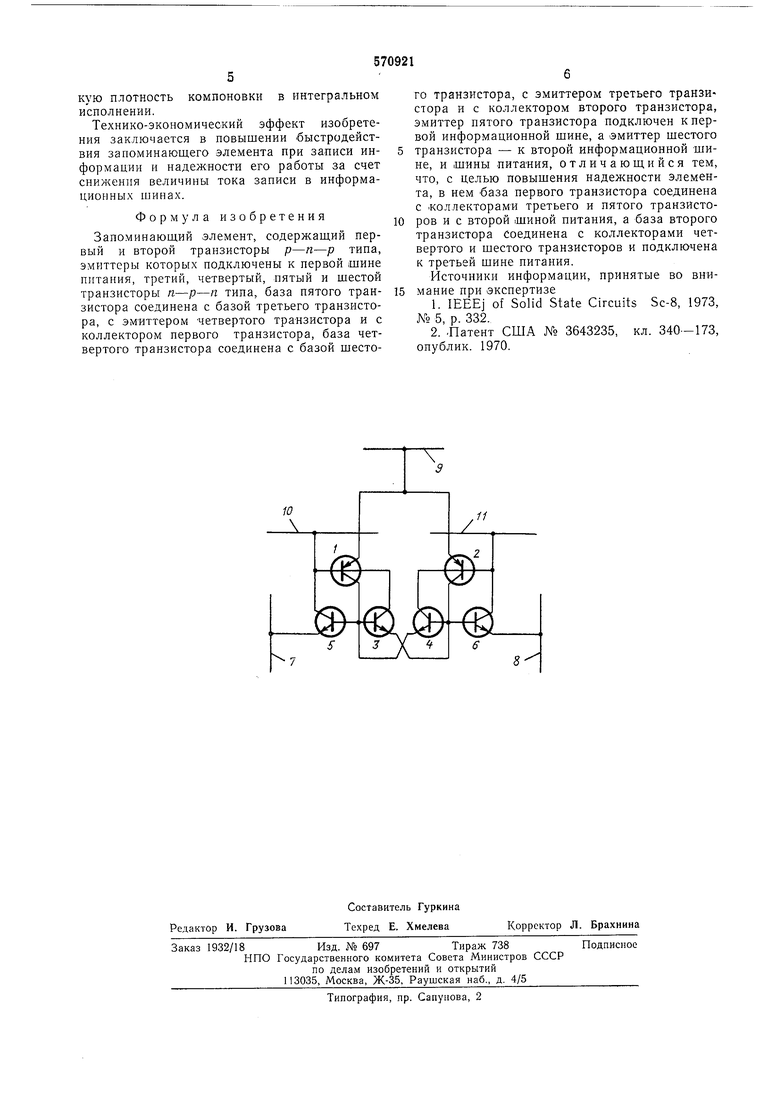

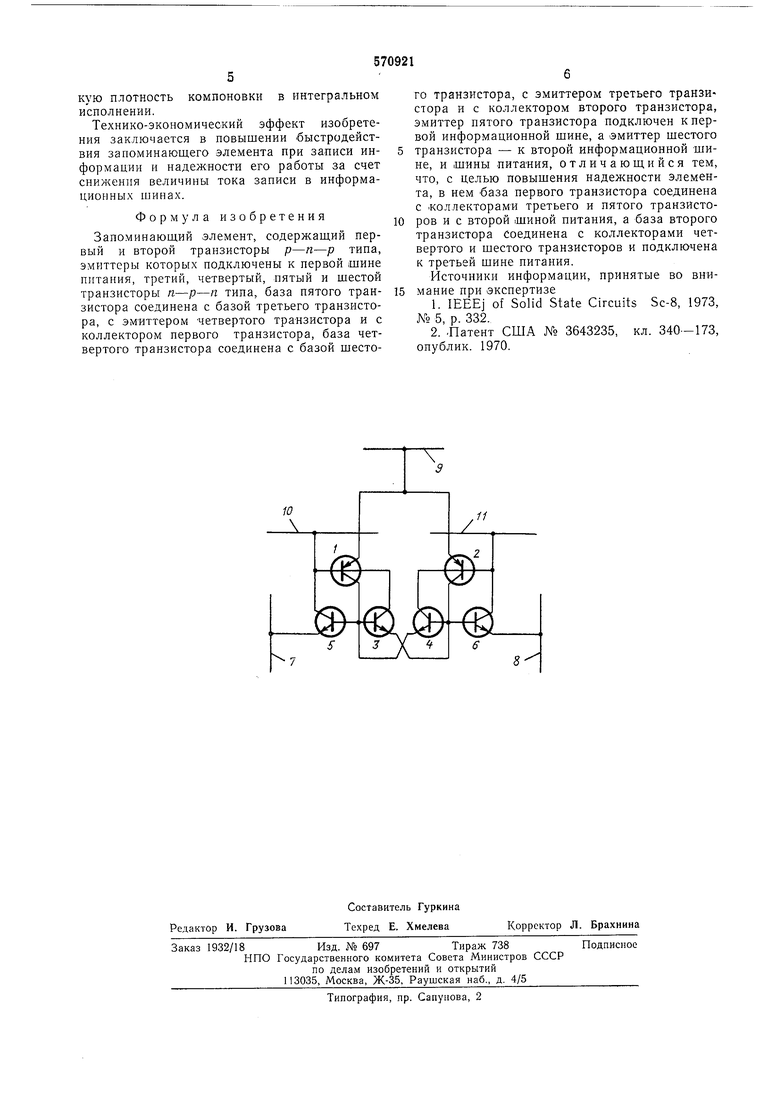

На чертеже представлена принципиальная электрическая схема предлагаемого запоминаюш,его элемента.

Она содер/кит транзисторы 1, 2р-л-р типа; транзисторы 3-6 п-р-п тина; информационные шины 7, 8; первую шину 9 питания (словарная шина); вторую 10 и третью II шины питания.

Предлагаемый запоминающий элемент работает следующим образом.

В режиме хранения информации потенциал на информационных шинах 7 и 8 поддерживают на уровне

ИHф.Ш /СЛ-Ш и Q,

где t/iiiKi). „г. - потенциал на информационных

шинах;

сл.ш. - потенциалы па словарной шине;

(УО - падение напряжения на открытом переходе база-эмиттер. При этом ток из словарной шины 9 протекает через эмиттерные переходы р-л-ртранзисторы 1 и 2 в шины 10 и 11 соответственно. Коллекторный ток р-л-р-транзисторов 1 и 2 через эмиттерные переходы л-р-лтранзнсторов 5 и 6 протекать в информационные шины 7 и 8 не может, так как для этого потенциал информационных шин должен быть не выше, чем

ИHф.Ш С-СЛ.Ш КН-о

где - напряжение коллектор - эмиттер насыщенного р-л-р-транзистора.

Коллекторный ток р-л-р-транзисторов 1 и 2 является базовым током л-р-л-транзисторов 3 и 4 соответственно, работающих в инверсном -включении.

Благодаря наличию перекрестных связей между транзисторами 3 и 4 и при условии идентичности л-р--л-транзисторов 1 и 2 базовые и коллекторные тока л-р-л-транзисторов 3 и 4 равны между собой, если инверсный коэффициент усиления транзисторов 3 и 4 и SiniB l, транзисторы 3 и 4 образуют бистабильную триггерную ячейку, в которой один из транзисторов открыт, например транзистор 3, а другой - транзистор 4-закрыт.

Па базе открытого транзистора 3 поддерживается высокий уровень, равный /сл.ш.- /кп, а на базе транзистора 4-низкий, равный

Ucn.ui 0

где LKH - напряжение коллектор-эмиттер насышенного л-р-л транзистора 3, в инверсном включении.

Таким образом, обеспечивается хранение ннформации.

При считывании информации потенциал на информационных шинах 7 и 8 устанавливают

Uc.l.ia- UQС/кн .Ш С -cл.Ш t-кн -o

Так как база транзистора 5 соединена с базой транзистора 3, то через эмиттерный переход транзистора 5 течет ток в информацнонную шину 7 и на ней устанавливается уровень

t-инф.ш -- -сл.ш - Ug.

в результате между информационными шинами 7 и 8 образуется разность потенциалов, которая и улавливается усилителем считывания.

Для записи информации в предлагаемый запоминающий элемент необходимо на одной из информационных шин, например на шине 7, оставить потенциал режима хранения или несколько повысить его, а на шине 8 понизить потенциал до уровня

.ш - сл.ш , аПри этом через эмиттерный переход л-р- л-транзистора 6 течет ток в ииформационную шину 8 и вызывает включение транзистора 6, коллекторный ток которого является базовым

током р-л-р-транзистора 2. Возрастание базового тока траизистора 2 ириводит к увеличению его коллекторного тока, который является и коллекторным током транзистора 3, в то время как базовый ток транзистора 3 остается неизменным на уровне режима хранения. В результате возрастания коллекторного тока транзистор 3 выходит из насыщения, перестает шунтировать базу транзистора 4 и последний включается.

Так как коэффициент усиления транзистора 3, работающего в инверсном режиме, мал (3-5), то для быстрого выхода его из насыщения достаточно, чтобы ток коллектора превысил ток базы в 10 раз.

При токе базы транзистора 3 на уровне 10 МК.4., достаточно развить коллекторный ток 100-200 мкА в информационную шину 8 необходимо пропустить такой же ток. Следовательно, не требуется развития больших токов в информационных шинах 7 и 8 во время записи, что с)щественно повышает быстродействие и надежность работы элемента.

Включение транзистора 4 приводит к шунтированию базы транзистора 3 и к его выклю-чению. В результате запоминающий элемент оказывается переведенным в другое состояние.

При необходимости изменить информацию на противоположную понижают потенциал на

информационной шине 7 по описанному принципу, и запоминающий элемент изменяет свое состояние.

Выполнение запоминающего инлсекционного элемента в соответствии с предлагаемойэлектрической схемой позволило получить высокую плотность компоновки в интегральном исполнении.

Технико-экономический эффект изобретения заключается в повышении быстродействия запоминающего элемента при записи информации и надежности его работы за счет снижения величины тока записи в информационных шинах.

Формула изобретения

Запоминающий элемент, содержащий первый и второй транзисторы р-л-р типа, эмиттеры которых подключены к первой шине питания, третий, четвертый, пятый и шестой транзисторы п-р-л типа, база пятого транзистора соединена с базой третьего транзистора, с эмиттером четвертого транзистора и с коллектором первого транзистора, база четвертого транзистора соединена с базой шестого транзистора, с эмиттером третьего транзистора и с коллектором второго транзистора, эмиттер пятого транзистора подключен к первой информационной шине, а эмиттер шестого

транзистора - к второй информационной шине, и шины питания, отличающийся тем, что, с целью повышения надежности элемента, в нем база первого транзистора соединена с Коллекторами третьего и пятого транзисторов и с второй шиной питания, а база второго транзистора Соединена с коллекторами четвертого и шестого транзисторов и подключена к третьей шине питания.

Источники информации, принятые во внимание при экспертизе

1.lEEEj of Solid State Circuits Sc-8, 1973, № 5, p. 332.

2..Патент США № 3643235, кл. 340-173, опублик. 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Инжекционный запоминающий элемент | 1974 |

|

SU526951A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1983 |

|

SU1171848A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

10

Авторы

Даты

1977-08-30—Публикация

1975-06-06—Подача