Изобретение относится к вычислительной технике, а именно к устройствам для обработки и хранения цифровой информации, и может быть исполь зовано для согласования информационных потоков устройств 5 работающих с разной скоростью обработки информации.

Целью изобретения является повьппе ние быстродействия устройства.

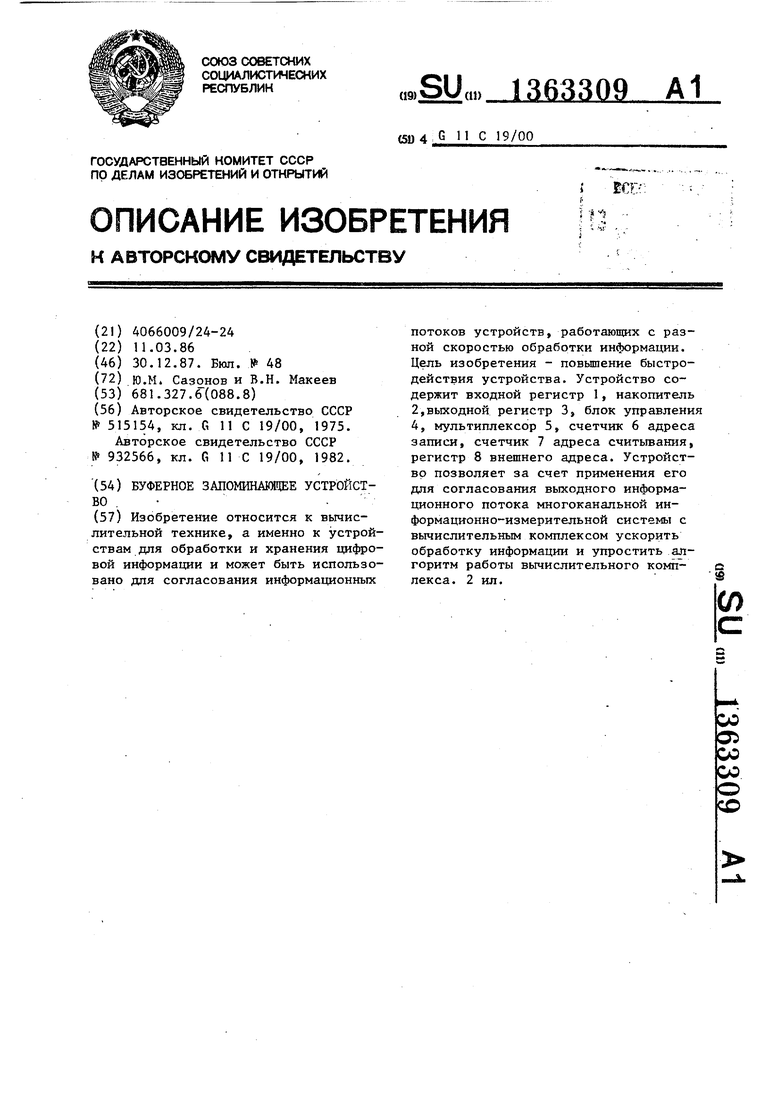

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема мультиплексора, вариант исполнения.

В состав буферного запоминающего устройства входит входной регистр 1, накопитель 2, выходной регистр 3, блок 4 управления, мультиплексор 5, счетчик 6 адреса записи, счетчик 7 адреса считывания, регистр 8 внешне- го адреса.

Устройство работает следующим образом.

При поступлении сигнала Запись блок 4 управления формирует импульсы обращения к накопителю 2, через мультиплексор 5 подключает выходы счетчика адреса записи 6 к адресным входам накопителя 2, и информация из входного регистра 1 записьшается в накопитель 2 по адресу, определяемому состоянием счетчика 6 адреса записи. При поступлении сигнала Считывание блок 4 управления формирует импульсы обращения к накопителю 2; если устройство-приемник информации устанавливает на входе Управление низкий потенциал, то блок 4 управления чере мультиплексор 5 подключает выходы счетчика 7 адреса считывания к адресным шинам накопителя 2 и в выходной регистр 3 считывается информация, хранившаяся в накопителе 2 по адресу определяемому состоянием счетчика 7 адреса считывания; если же устройство - приемник информации устанавливает на входе Управление высокий потенциал, то мультиплексор 5 подключает выходы регистра 8 внешнего адреса к адресным входам накопителя 2 и в выходной регистр 3 считьгоается информация, хранившаяся в накопителе 2 по адресу, определяемому состоянием триггеров регистра В внешнего адреса

Таким образом,использование изобретения позволяет существенно повысить быстродействие устройства. Применение устройства для согласования выходного информационного потока мно

гоканальной информационно-измерительной системы с вычислительным комплексом, используемым для обработки получаемой информации, позволяет ускорить обработку информации и упростить алгоритм работы вычислительного комплекса. Например, в одном из возможных вариантов осуп1ествление выборки из буферного запоминающего устройства сначала только одного или нескольких каналов, информация которых имеет первостепенное значение для проводимых измерений, позволяет быстро отыскивать наиболее важные или критические изменения получаемой по этому каналу или каналам информации и выборку остальных каналов производить в соответствии с получаемой конкретной информацией. В противном случае пришлось бы сначала считать весь массив информации из буферного запоминающего устройства и только после этого производить ее анализ.

Формула изобретения

30

25

Буферное .запоминающее устройство, содержащее накопитель, информационные входы которого подключены к выходам входного регистра, входы которого являются информационными входами уст- ройства, информационные выходы нако-

35 пителя соединены с вхЬдами выходного регистра, выходы которого являются информационными выходами устройства, блок управления, входы управления записью и считыванием которого явля40 ются соответственно входами разрешения записи и считывания устройства, первый, второй и третий выходы блока управления подключены соответственно к управляющему входу накопителя, вхо45 дам счетчиков адреса записи и адреса считывания, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены мультиплексор, регистр внешнего адре50 са, причем четвертый и пятый выходы блока управления подключены соответственно к первому и второму управляющим входам мультиплексора, третий управляющий вход которого является

55 управляющим входом устройства, выхо- ,ды счетчика адреса записи подключены к информационным входам первой группы мультиплексора, выходы счетчика адреса считывания подключены к информационнь1м входам второй группы мультиплексора, выходы которого подключены к адресным входам накопителя, информационные входы третьей группы

мультиплексора соединены с выходами регистра внешнего адреса, выходы которого являются адресными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1288757A1 |

| Запоминающее устройство | 1981 |

|

SU982085A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для регистрации,съема и обработки информации с пропорциональных камер | 1980 |

|

SU951967A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство | 1978 |

|

SU696871A1 |

| Буферное запоминающее устройство | 1974 |

|

SU515154A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-30—Публикация

1986-03-11—Подача