(54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

Изобретение относится к области электронной вычислительной техники и может быть использовано в аппаратуре контроля и настройки цифровых узлов ЭВМ.

Известно устройство для тестового контроля цифровых узлов, содержащее блок ввода данных, блок входных и эталонных выходных сигналов, коммутатор сигналов, блоки сравнения, индикации, управления, блок контролируемых выходов 1.

Основной недостаток этого устройства- сложность конструкции.

Наиболее близким техническим решением к данному изобретению является устройство для тестового контроля цифровых узлов, содержащее блок памяти, соединенный через блок записи информации с входами регистра теста, выходы которого соединены соответственно с первыми входами схем сравнения 2.

Это устройство обладает тем недостатком, что контакты проверяемого узла коммутируются вручную, вследствие чего на подготовительные операции уходит значительное количество времени, а участие человека в операции коммутации вносит, возможность погрешности при ее исполнении. Кроме того, необходимость иметь для каждого проверяемого узла таблицу коммутации при значительном количестве THпов узлов создает неудобства при эксплуатации устройства.

Для повышения производительности и надежности контроля в предлагаемое устройство введены блок управления и блоки распознавания входов и выходов, причем первый, второй и третий выходы блока управления соединены соответственно с первым и вторы.м входами блоков распознавания входов и выходов и с управляющим входом блока записи информации, первые выходы блоков распознавания входов и выходов соединены с входами и выходами контролируемых узлов и со вторыми входами соответствующих схем сравнения, вторые выходы блоков распознавания входов и выходов соединены с третьими входа.ми соответствующих схем сравнения, выходы которых соединены с входами блока управления, выходы регистра тестов соединены с третьими входами соответствующих блоков распознавания входов и выходов; кроме того, блок распознавания входов и выходов содержит делитель напряжения, узел дифференцирования, триггер, усилитель и реле, причем первый вход блока соединен с первым выводом делителя напряжения, второй вывод которого соединен с выходом блока и с первым контактом реле, третий вывод делителя напряжения соединен через узел дифференцирования с первым входом триггера, второй вход которого соединен со вторым входом блока, а выход - со вторым выходом блока и через усилитель с реле, третий вход блока соединен со вторым контактом реле.

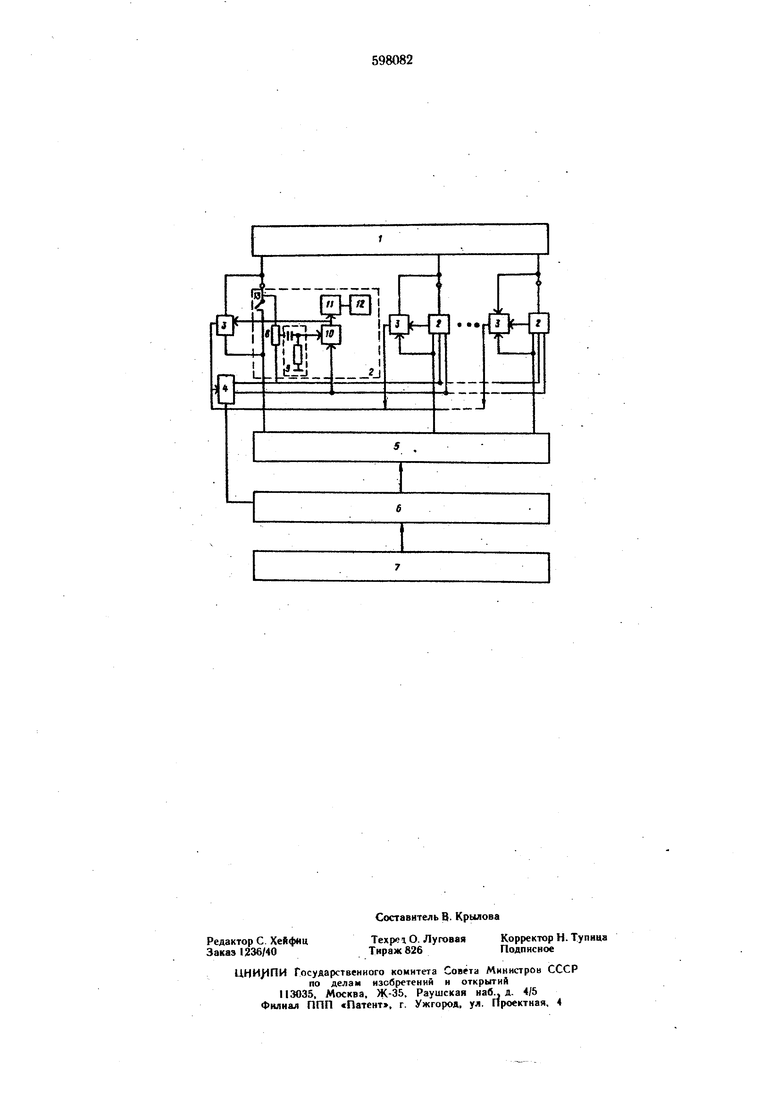

На чертеже приведена функциональная схема описываемого устройства для тестового контроля цифровых узлов }, содержащего блоки распознавания 2 входов и выходов, схемы сравнения 3, блок управления 4, регистр теста 5, блок записи 6 и блок памяти 7. Каждый блок распознавания входови выходов 2 содержит делитель напряжения 8, узел дифференцирования 9, триггер 10, усилитель il, обмотку реле 12, контакты реле 13.

Устройство работает следующим образом.

Контролируемый узел 1 имеет п контактов, каждый из котооыл может быть входным илн выходным. В блоке памяти 7 записаны тесты для его проверки. По младшим адресам блока памяти 7 записан код соответствия входов и выходов, по остальным адресам - тестовые слова, которые представляют собой совокупность «1 и «О, соответствующих входной комбинации и эталонной выходной реакции контролируемого узла 1. Проверка осуществляется путем сравнения выходной реакции эталонного узла, записанной в блоке памяти 7, с реакцией контролируемого узла.

Перед проверкой узла 1 с блока управления 4 на нулевые входы триггера Ш каждого блока распознавания 2 подается импульс сброса, который устанавливает их в нулевое состояние. Затем ira первый вывод делителя напряжения 8 каждого блока распознавания 2 с блока упраоления 4 поступает импульс, соответствующий логической единице, Если первый контакт контролируемого узла является входом, то на третьем выводе делителя напряжения 8 появляется единичный импульс, который через узел дифференцирования 9 поступает на единичный вход триггера 10 и устанавливает его в единичное . С выхода триггера 10 потенциал логической единицы поступает через усилитель 11 на обмотку реле 12, которое, срабатывая, подключает вход контролируемого узла 1 к соответствующему ему выходу регистра теста 5, р который по сигналу из блока управления 4 переписан нз блока памяти 7 код соответствия входов и выходов. Схемы сравнения 3 сравнивают этот код с информацией, поступающей с единичных выходов триггеров 10. В случае, если информация совпадает, блок записи 6 считывает из блока памяти 7 проверочное слово, заносит его в регистр теста 5, далее информация поступает в схему сравнения, где сравнивается с выходной информацией контролируемого узла I.

При несравнении хотя бы на одной из схем сравнения 3 нз блока управления 4 на блок записи б поступает запрещающий сигнал. Несовпадение информации фиксируется индикатором, которыА на чертеже не показан. При совпадении информации из блока памяти 7 считывается следующее проверочное слово и т. д., пока узел 1 не будет проверен по- ностью.

Выходное напряжение узла дифференцирования блока распознавзния входов и выходов

2 зависит QT входного, то есть от перепадов потенциалов на третьем выводе делителя напряжения 8, которые для выходных контактов контролируемого узла 1 вдвое меньще, чем для входных. Узел дифференцирования блока распознавания входов и выходов 2 настроен так, что когда ко второму выводу делителя напряжения 8 подключен выход контролируемого узла, на его выходе остается потенциал логическою нуля. Тем самым контакты контролируемого узла J, являющиеся выходными, не коммутируются с выходами регистра теста 5.

Устройство для тестового контроля цифровых узлов позволяет производить коммутацию контактов проверяемого узла автоматически, за время значительно меньщее, чем в прототипе.

Конструктивное выполнение блока распознавания входов и выходов позволяет при сравнении информации, полученной с единичных входов и выходов, обнаруживать неисправность входа или выхода, связанного непосредственно

с контактом проверяемого узла.

Формула изобретения

д распознавания входов и выходов, причем первый, второй и третий выходы блока управления соединены соответственно с первым и вторым входами блоков распознавания входов и выхоДоз и с управляющим входом блока записи информации, первые выходы блоков распознавания входов и выходов соединены с входами и выходами контролируемых узлов и со вторыми входами соответствующих схем сравнения, вторые выходы блоков распознавания входов и выходов соединены с третьими входами соот ветствующих схем сравнения, выходы которых

соединены с входами блока управления, выходы регистра тестов соединены с третьими входами соответствующих блоков распознавания входов и выходов.

контактом реле.

Источники информации, принятые Во внимание при экспертизе:

« 2. Авторское свидетельство СССР № 390526, кл. G 06 F 11/04, 1971.

Авторы

Даты

1978-03-15—Публикация

1975-02-10—Подача