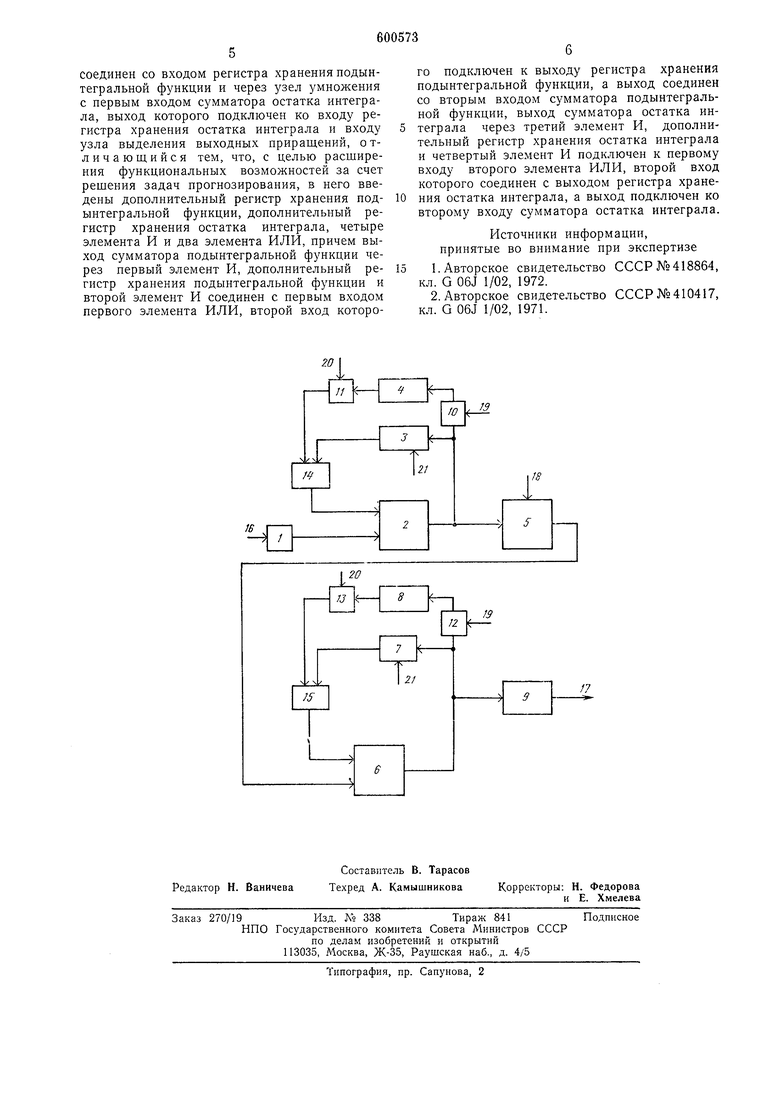

ния подынтегральной функции, дополнительный регистр 4 хранения подынтегральной функции, узел 5 умноження, сумматор 6 остатка интеграла, регистр 7 хранения остатка интеграла, дополнительный регистр 8 хранения остатка интеграла, узел 9 выделения выходных приращений, элементы И 10-13, элементы ИЛИ 14 и 15, шины связи 16--21 решаюндего блока.

Выход сумматора 1 входных приращений соединен со входом сумматора 2 подынтегральной функции, другой вход которого соединен с выходом элемента ИЛИ 14, входы которого соединены с выходами регистра 3 хранения подынтегральной функции и элемента И 11. Выход сумматора 2 подынтегральной функций соединен со входом регистра 3 хранения подынтегральной функции, второй вход которого соединен с щиной 21 стирания, входом элемента И 10 и входом узла 5 умножения, второй вход которого соединен с шиной 18 независимой переменной. Второй вход элемента И 10 соединен с шиной 19 потенциала записи, а выход - со входом дополнительного регистра 4 хранения подынтегральной функции, выход которого соединен с шиной 20 потенциала считывания.

Выход узла 5 умноження соединен со входом сумматора 6 остатка интеграла, второй вход которого соединен с выходом элемента 15 ИЛИ, входы которого соединены с выходамн регистра 7 хранения остатка интеграла н элемента И 13. Выход сумматора 6 остатка интеграла соединен со входом узла 9 выделения выходных приращений, входом регистра

7хранения остатка интеграла, второй вход которого соединен с шиной 21 стнрания, и входом элемента И 12, второй вход которого соединен с шиной 19 потенциала записи, а выход - со входом дополнительного регистра

8хранения остатка интеграла, выход которого соединен со входом элемента И 13, второй вход которого соединен с шиной 20 потенциала считывания.

Выход узла 9 выделения выходных приращений соединен с шиной 17 выхода решающего блока.

Рассмотрим работу решающего блока.

Приращения подынтегральной функции поступают по щине 16 на входы сумматора 1 входных приращений. Сумма приращений, полученных в сумматоре 1, поступает на вход сумматора 2 подынтегральной функции, на второй вход которого поступает информация из регистра 3 хранения подынтегральной функции, проходящая через элемент ИЛИ 14, с выхода сумматора 2 приращения подынтегральной функции ноступают в регистр 3 н на вход узла 5 умножения. Элемент И 10 закрыт. В узле 5 умножения образуется произведение значения подынтегральной функции на приращение независимой переменной, поступающей по шине 18, т. е. получается приращение интеграла, которое поступает на

вход сумматора 6 остатка интеграла. В сумматоре 6 происходит сложение полученно10 приращения интеграла с остатком интеграла, который хранится в регистре 7. Значение интеграла с выхода сумматора 6 поступает в регистр 7 хранения остатка интеграла и в узел 9 выделения выходных приращений, где происходит выделение приращений интеграла на щину 17 выхода решающего блока.

Если в решающем блоке, работающем в реальном масштабе времени, входная информация обрабатывается за время цикла т, которое определяется моментами ностунления входных величин, то в нредлагаемом решающем блоке эта информация будет обрабаты 2

ваться за время , где Г - время

/С Т

нрогнозирования. Через нромежуток времени TI после начала очередного цикла по шине 19

подается потенциал записи. Элементы И 10 н 12 открываются, и вычисленные значения подынтегральной функции и остатка интеграла, соответствующие значениям этих величин к началу следуюшего цикла в реальном масштабе времени, записываются в дополнительные регистры 4 и 8 соответственно. Оставшийся промежуток времени т-TI до окончания цикла решающий блок работает как прогнозирующее устройство, моделируя процесс в ускоренном масштабе времени.

По нриходу следующей входной величины по шине 20 подается потенциал считывания, а но шине 21-потенциал стирания. Прогнозируемая информация в регистрах 3 и 7 стирается. Элементы И И и 13 открываются, и хранимая в дополнительных регистрах 4 и 8 информация проходит через элементы ИЛИ 14 и 15 соответственно на суммирование. После считывания информации из регистров 4 и

8 потенциал считывания убирается, и весь процесс повторяется снова.

Построение специализированных цифровых интегрирующих машин, предназначенных для

моделирования задач в реальном и ускоренном масштабе времени, на основе предлагаемого решающего блока работающую одновременно по двум каналам - каналу обработки информации в реальном масштабе времени и каналу прогнозирования, позволит вдвое сократить расход оборудования по сравнению с машинами, построенными на основе известных решающих блоков.

Формула изобретения

Решающий блок цифровой интегрирующей структуры, содержащий сумматор входных приращений, сумматор подынтегральной функции, регистр хранения подынтегральной

функции, узел умножения, сумматор остатка интеграла, регистр хранения остатка интеграла н узел выделения выходных нриращений, причем выход сумматора входных приращений соединен с первым входом сумматора подынтегральной функции, выход которого

соединен со входом регистра хранения подынтегральной функции и через узел умножения с нервым входом сумматора остатка интеграла, выход которого подключен ко входу регистра хранения остатка интеграла и входу узла выделения выходных приращений, отличающийся тем, что, с целью расщирения функциональных возможностей за счет рещения задач прогнозирования, в него введены дополнительный регистр хранения подынтегральной функции, дополнительный регистр хранения остатка интеграла, четыре элемента И и два элемента ИЛИ, причем выход сумматора подынтегральной функции через первый элемент И, дополнительный регистр хранения подынтегральной функции и второй элемент И соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу регистра хранения подынтегральной функции, а выход соединен со вторым входом сумматора подынтегральной функции, выход сумматора остатка интеграла через третий элемент И, дополнительный регистр хранения остатка интеграла и четвертый элемент И подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом регистра хранения остатка интеграла, а выход подключен ко второму входу сумматора остатка интеграла.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №418864, кл. G 06J 1/02, 1972.

2.Авторское свидетельство СССР №410417, кл. G 06J 1/02, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU650085A2 |

| Цифровой интегратор | 1979 |

|

SU805362A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Решаюший блок цифровой интегрирующей структуры | 1977 |

|

SU646354A1 |

20

JB

J3

Авторы

Даты

1978-03-30—Публикация

1976-01-12—Подача