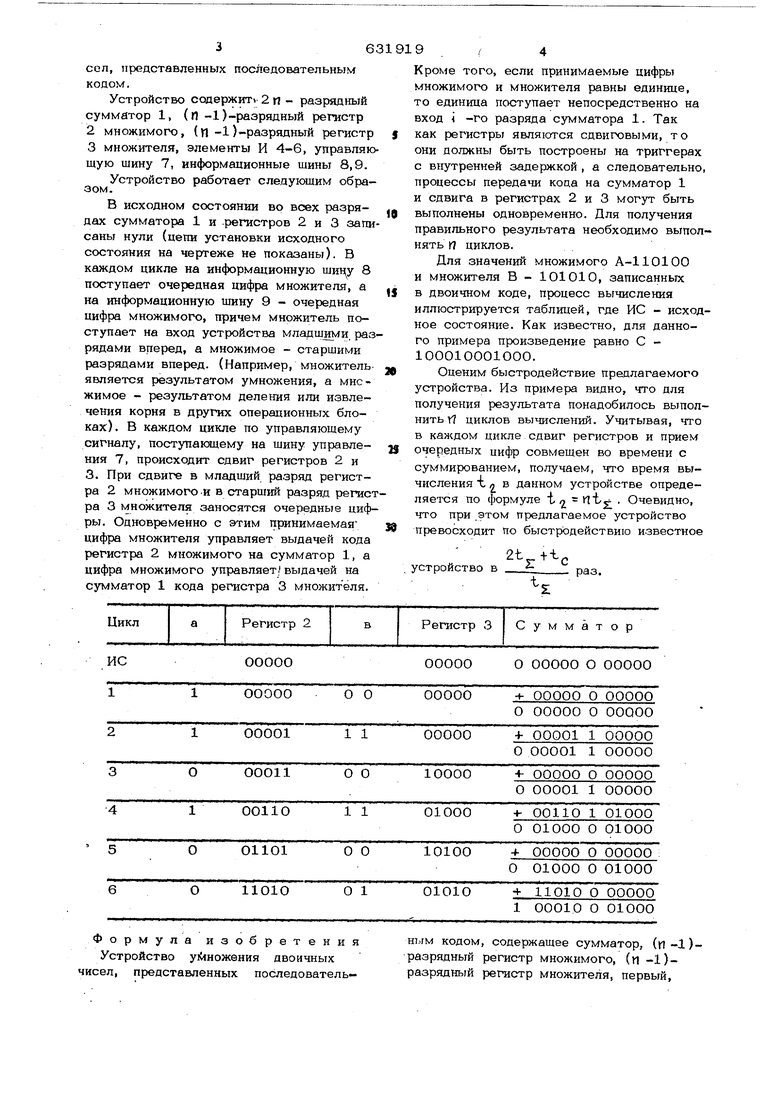

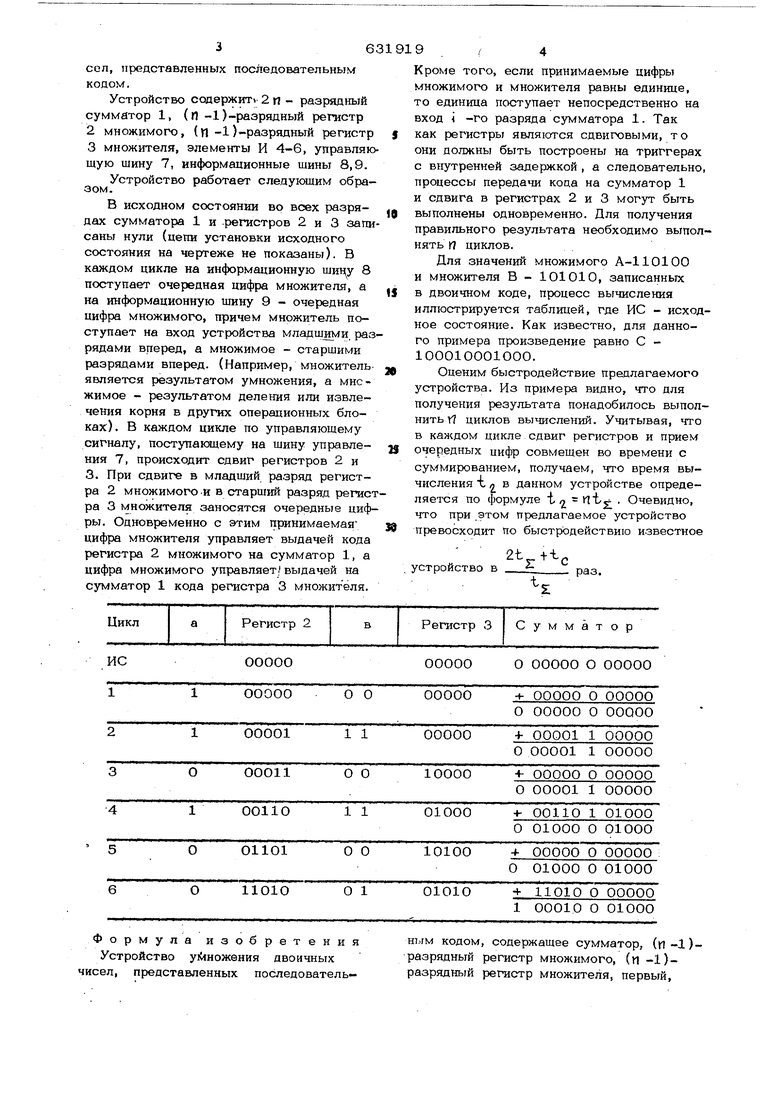

сеп, представленных последовательным кодом. Устройство содержит - 2 Г7 - разрждный сумматор 1, (п -1)-разрядный регистр 2множимого, (п-1 )-разр$здный регистр 3множителя, элементы И 4-6, управляю щую шину 7, информационные шины 8,9. Устройство работает следующим обраВ исходном состоянии во всех разрядах сумматора 1 и .регистров 2 и 3 запи саны нули (цепи установки исходного состояния на чертеже не показаны). В каждом цикле на информационную 8 поступает очередная цифра множителя, а на информационную шину 9 - очередная цифра множимого, причем множитель поступает на вход устройства младшими, раз рядами вперед, а множимое - старшими разрядами вперед. (Например, множитель является результатом умножения, а мнсжимое - результатом деления или извлечения корня в других операционных блоках). В каждом цикле по управляющему сигналу, поступаклцему на шину управления 7, происходит сдвиг регистров 2 и 3. При сдвиге в младший разряд регистра 2 множимого И в старший разряд регис ра 3 множителя заносятся очередные циф ры. Одновременно с этим принимаемая цифра множителя управляет выдачей кода 6 9I4 Кроме того, если принимаемые цифры множимого и множителя равны единице, то единица поступает непосредственно на вход 4 -го разряда сумматора 1. Так как регистры являются сдвиговыми, то они должны быть построены на триггерах с внутренней задержкой , а следовательно, процессы передачи коца на сумматор 1 и сдвига в регистрах 2 и 3 могут быть выполнены одновременно. Для получения правильного результата необходимо выполнять YI циклов. Для значений множимого А-110100 и множителя В - 101010, записанных в двоичном коде, процесс вычисления иллюстрируется таблицей, где ИС - исходное состояние. Как известно, для данного примера произведение равно С 100010001ООО. Оценим быстродействие преалагаемого устройства. Из примера видно, что для получения результата понадобилось выполнить т7 циклов вычислений. Учитывая, что в каждом цикле сдвиг регистров и прием очередных цифр совмещен во времени с суммированием, получаем, что время вычисления Ь л в данном устройстве определяется по формуле t 2 Очевидно, что при этом предлагаемое устройство превосходит по быстродействию известное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

Формула изобретения

Устройство у1иножвния двоичных чисел, представленных последовательным кодом, содержащее сумматор, (и-1)разрядный регистр множимого, (п -1)разрядный регистр множителя, первый. второй и третий элементы И, первые вхо ды которых соединены с управляющей ши ной устройства, второй вход первого элемента И соединен с первой информационной шиной, а выход - с разрядными входами регистра множимого, выход -го (( 1-П -1) разряда которого соецинен со входом (п41)-го разряда сумматора, второй вход третьего элемента И соединен со второй информационной шиной, а выход - с разрядными входами регистра множителя, входы сдвига регистров множимого и множителя соединены с управляющей шиной устройства, о т л и ч а. ющ е е с я тем, что, с целью повышения быстродействия, сумматор дополнительно содержит И-1 младших разрядов, второй 63 6 и третий входы второго элемента И соединены соответственно с первой и вторсй информационными шинами, а выход - с Ц -м разрядом сумматора, выход первого элемента И соединен с ( h -1) -м разрядом регистра множителя, выход го разряда которого соединен со входом -го разряда сумматора, выход третьего элемента И соеаинен со входом 1-го разряда репютра множимого. Источники информашш, принятые во нимание при экспертизе: 1,Карцев М. А. Арифметика цифровых машин. Наука, 1969, с. 459. 2.Авторское свидетельство СССР 451079, кл. ( ОС Р 7/39, 1974.

Авторы

Даты

1978-11-05—Публикация

1975-05-22—Подача