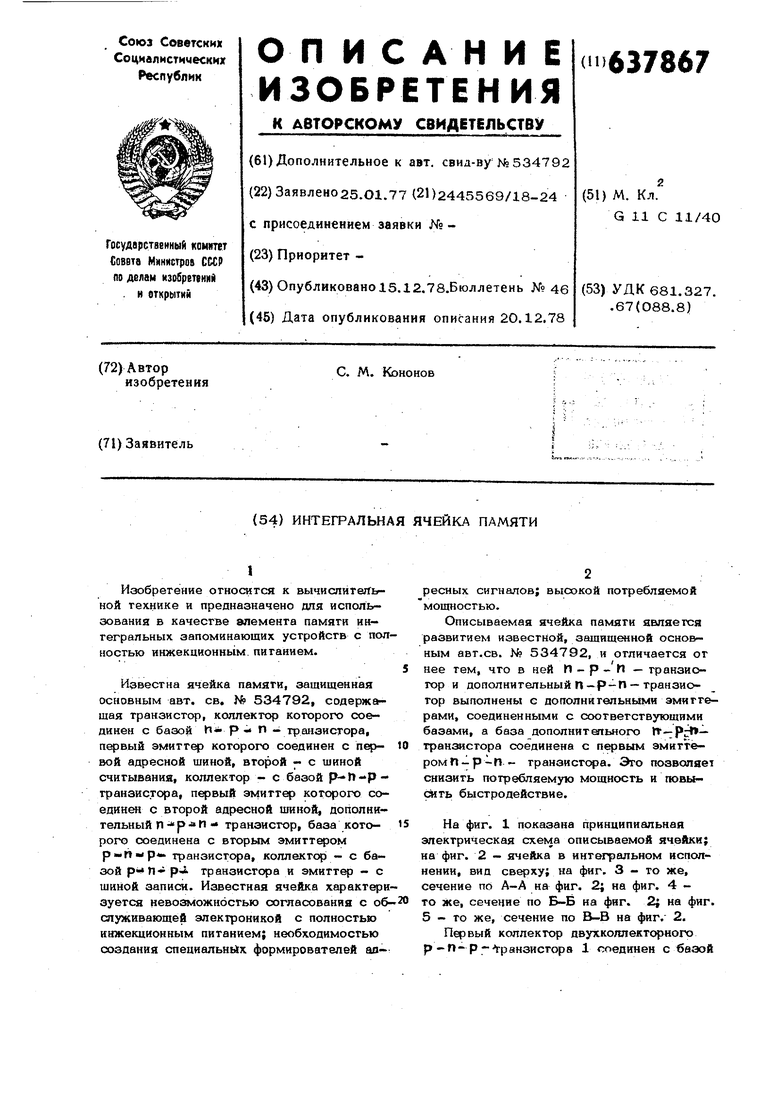

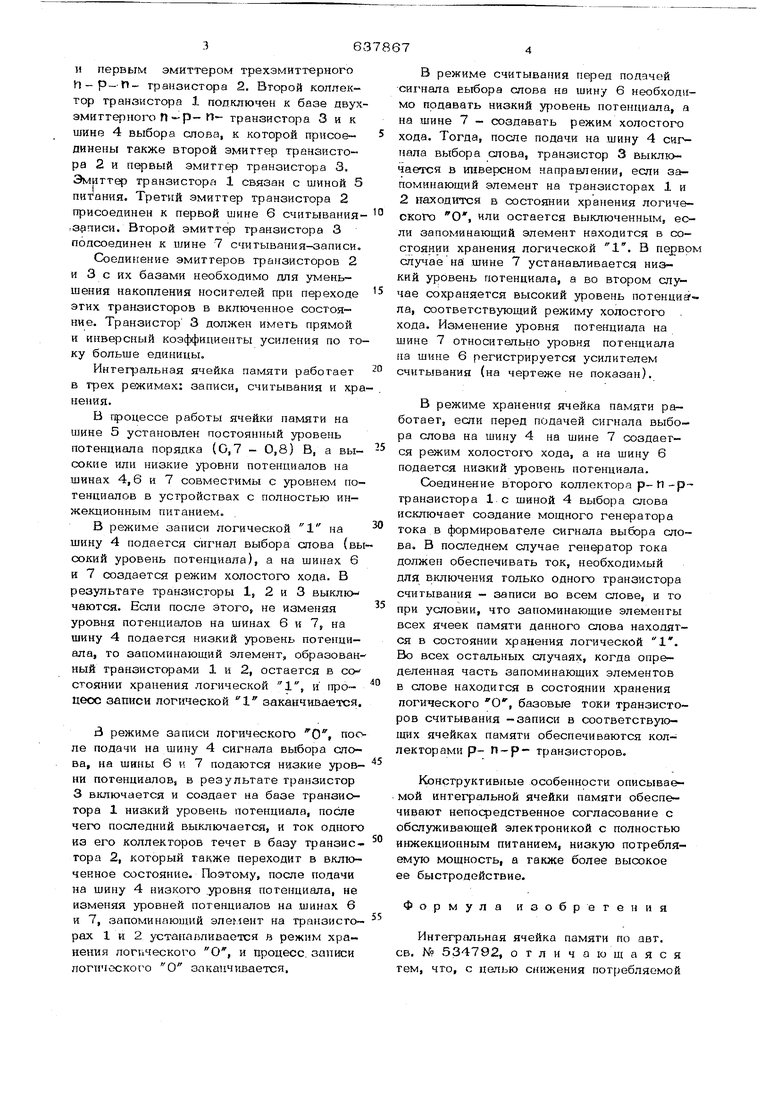

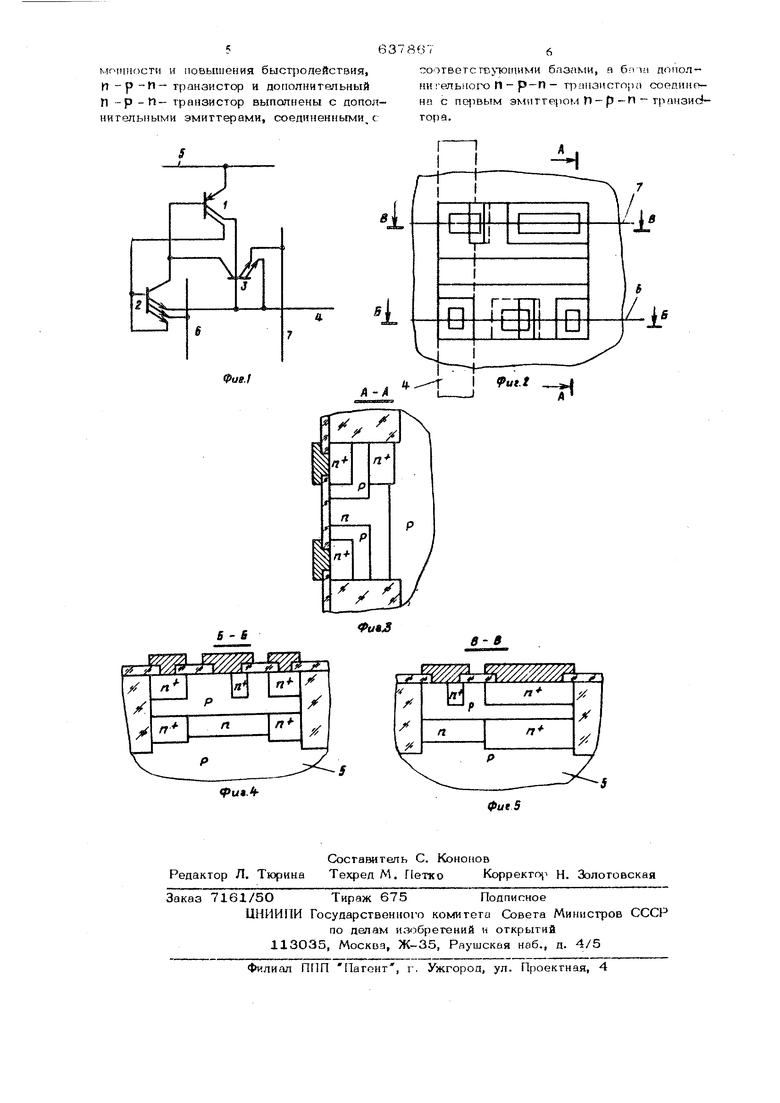

Изобретение огносится к вычисяйтетГьгной технике и предназначено для использования в качестве элемента памяти интегральных запоминающих устройств с пол ностью инжекционным питанием. Известна ячейка памяти, защищенная основным авт. св. № 534792, содержащая транзистор, коллектор которого соединен с базой П- Р - П - транзистора, первый эмиттер которого соединен с первой адресной шиной, второй - с шиной считывания, коллектор - с базой p-rt-pтранзистора, первый эмиттер которого соединен с второй адресной шиной, дополнительный п И транзистор, база которого соединена с вторым эмитт ом ршПхро транзистора, коллектор - с базой p-«h Р- транзистора и эмиттер - с шиной записи. Известная ячейка характер зуется невозможностью согласования с об служивающей электроникой с полностью инжекционным питанием; необходимостью создания специальных формирователей авресных сигналов; высокой потребляемой мощностью. Описываемая ячейка памяти является развитием известной, защищенной основным авт.св. № 534792, и отличается от нее тем, что в ней П - р -п - транзистор и дополнительный П - р-П -транзистор выполнены с дополнительными эмиттерами, соединенными с соответствующими базами, а база дополнититьного тран 1стора соединена с первым эмиттером Л - р -П - транзистора. Это позволяет снизить потребляемую мощность и повысить быстродействие. На фиг. 1 показана принципиальная электрическая схема описываемой ячейки; на фиг. 2 - ячейка в интегральном исполнении, вид сверху; на фиг. 3 - то же, сечение по А-А на фиг. 2; на фиг. 4 то же, сечение по Б-Б на фиг. 2; на фиг. 5 - то же, сечение по В-В на фиг. 2. Первый коллектор двухколлект шого р-П-р транзистора 1 соединен с базой и первым эмиттером трехэмиттерного .n гранзисгора 2, Второй коллектор гранзисгора 1 подключв к базе двухsMHrrepHoixi П - Р-п- транзисгора 3 и к шине 4 выбора слова, к которой прнсоединены также второй эмигтер гранаисгора 2 и первый эмигтер транзистора 3. Эмиттер транзистора 1 связан с шиной 5 питания. Третий эмиттер транзисгора 2 присоединен к первой шине 6 считывания13аписи. Вгорой эмиггер транзисгора 3 подсоединен к шине 7 считывания-записи. Соединение эмиттеров транзисторов 2 и 3 с их базами необходимо для уменьшения накопления носителей при переходе этих транзисторов в включенное состояние. Транзистор 3 должен имегь прямой и инверсный коэффициенты усиления по току больше единицы. Интегральная ячейка па1у1яти работает в грех режимах: записи, считывания и хра нения. В процессе работы ячейки памяти на шине 5 установлен постояннрлй уровень потенциала порядка (0,7 - 0,8) В, а вы- сокие или низкие уровни потенциалов на шинах 4,6 и 7 совместимы с уровнем потенциалов в устройствах с полностью ин- жекционным питанием. В режиме записи логической 1 на шину 4 подается сигнал выбора слова (вы сокий уровень потенциала), а на шинах 6 и 7 создается режим холостого хода. В результате транзисторы 1, 2 и 3 выклк чаются. Если после этого, не изменяя уровня потенциалов на шинах 6 и 7, на шину 4 подается низкий уровень потенциала, го запоминаюший элемент, образован ный транзисторами 1 и 2, остается в состоянии хранения логической 1, и процесс записи логической 1 заканчивается. В режиме записи логического О, поо ле подачи на шину 4 сигнала выбора слова, на шины 6 и 7 подаются низкие уровни потенциалов, в результате гранзисгор 3 включаегся и создает на базе транаиогора 1 низкий уровень потенциала, после чего последний выключается, и ток одного из его коллекторов течет в базу транзисгора 2, который также переходит в включенное состояние. Поэтому, после подачи на шину 4 низкого .уровня потенциала, не изменяя уровней потенциалов на шинах 6 и 7, запоминающий элемент на транзисторах 1 и 2 устанавливается в режим хра нения логического О, и процесс, записи логического О заканчивается. В режиме считывания перед подачей сигнала выбора слова на шину 6 необходимо подавать низкий уровень потенциала, а на шине 7 - создавать режим холостого хода. Тогда, после подачи на шину 4 сигнала выбора слова, транзистор 3 выключается в шшерсном направлении, если запоминаюший элемент на транзисторах 1 и 2 находитхзя в состоянии хранения логического О, или остается выключенным, если запоминающий элемент находится в состоянии хранения логической 1. В нервом случае ни .шине 7 устанавливается низкий уровень потенциала, а во втором случае сохраняется высокий уровень потенциала, соотвегсгвующий режиму холосгого . хода. Изменение уровня потенциала на .шине 7 относительно уровня потенциала на шине 6 регистрируется усилителем считывания (на чертеже не показан). В режиме хранения ячейка памяти работает, если перед подачей сигнала выбора слова на шину 4 на шине 7 создается режим холостогю хода, а на шину 6 подается низкий уровень потенциала. Оэединение второго коллектора р-И -ртраг{зистора 1.с шиной 4 выбора слова исключает создание мощного генератора тока в формирователе сигнала выбора слова, Б последнем случае генератор тока должен обеспечивать ток, необходимый для включения голько одного транзистора считывания - записи во всем слове, и то при условии, что запоминающие элементы всех ячеек памяти данного слова находятся в состоянии хранения логической 1. Во всех остальных случаях, когда определенная часть запоминающих элементов в слове находится в состоянии хранения логического , базовые токи транзисторов счигывания -записи в соответствующих ячейках памяти обеспечиваются коллекторами р- П-р- транзисторов. Конструктивные особенности описываемой интегральной ячейки памяти обеспечивают непосредственное согласование с обслуживающей электроникой с полностью инжекционным питанием, низкую потребляемую мощность, а также более высокое ее быстродействие. Формула изобретения Интегральная ячейка памяти по авт. св. № 534792, отличающаяся тем, что, с целью снижения потребляемой

мощности и повышения быстролействня, И -р -И- гранзисгор и пополнительный П -р -И- транзистор выполнены с пополнительными эмиттерами, соединенными, с

cooтвoтcгD omи и базами, а бп ia пополни -елько:х) (1 - р-П - транзистор;) соепине- на с эмиттером П - р-П - трпизис - тора.

/U

1

Г

E3f-fl

Фа8.1

I Put.t aJ

А-А Jл1

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный запоминающий элемент | 1976 |

|

SU615541A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

Авторы

Даты

1978-12-15—Публикация

1977-01-25—Подача