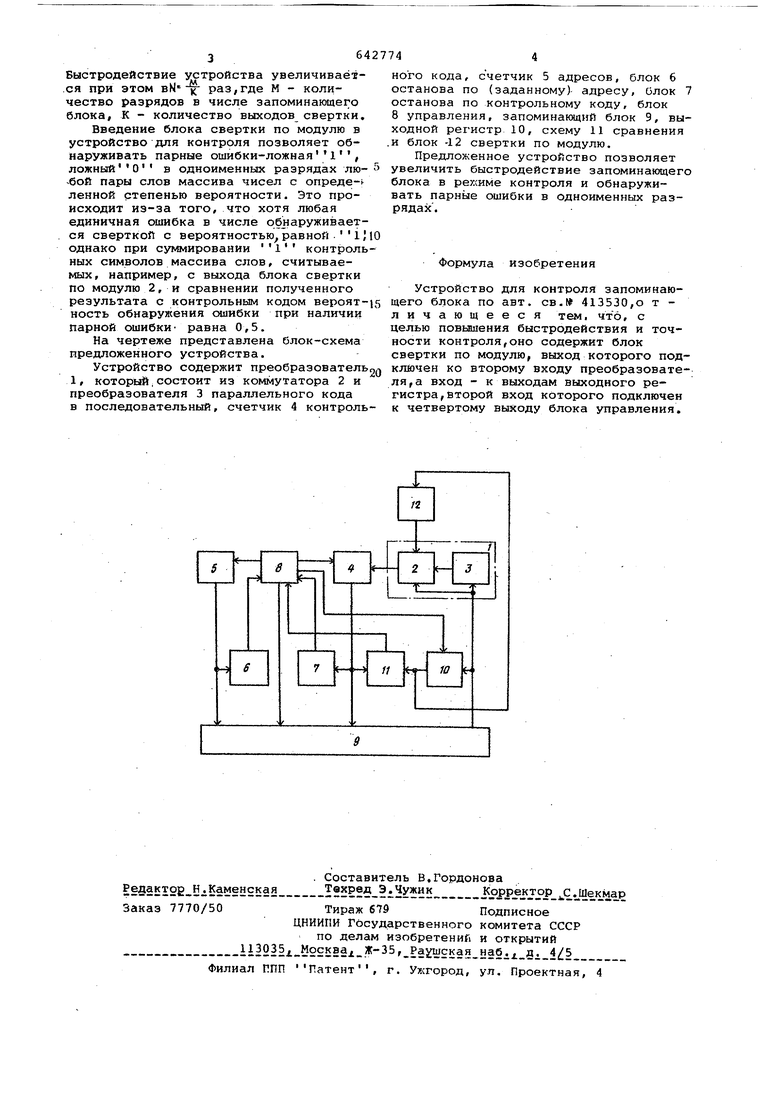

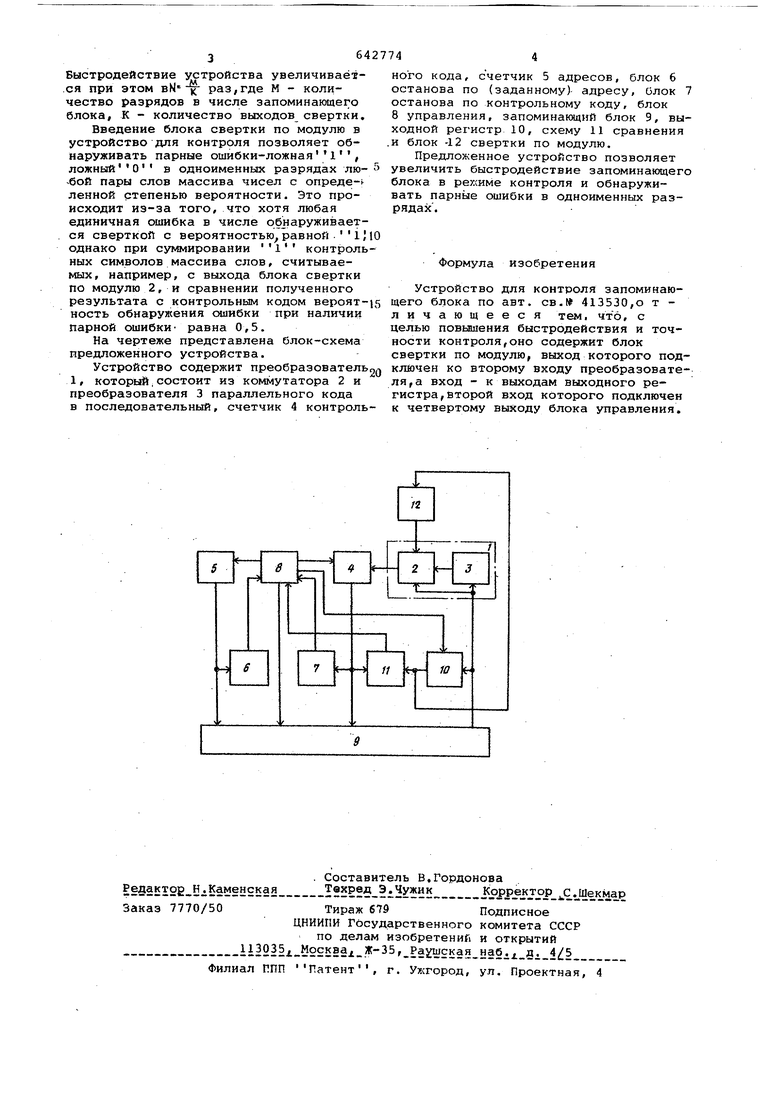

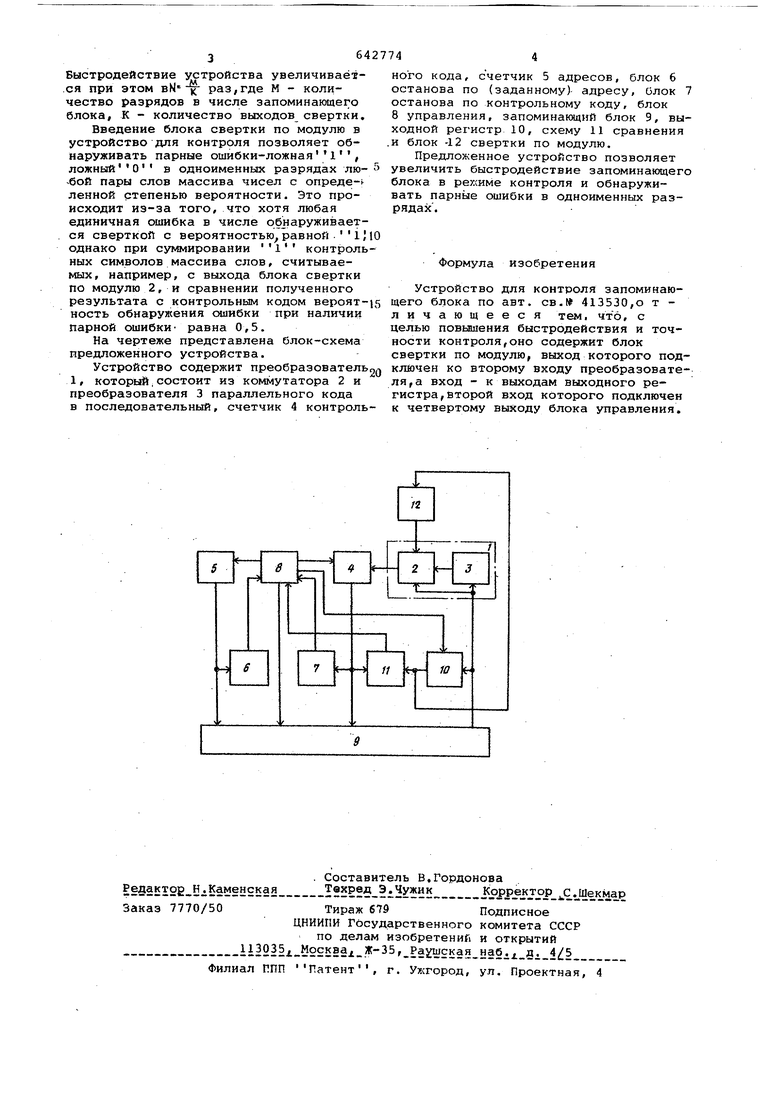

Изобретение относится к области вычислительной техники. По основному авт.св,№413530 извес но устройство для контроля запоминаю щих блоков, содерхгащее выходной регистр, вход которого подключен к выходу запоминающего блока, а выход к одному входу схемы сравнения, счетчик адресов, разрядные выходы которого подсоединены к блоку останова по адресу и запоминающему блоку, а выхо к блоку управления, преобразователь, вход которого подключен к выходу запо минающего блока, счетчик контрольног кода, один из входов которого подсое динен к выходу преобразователя, друго к блоку управления, а выход - к друго му входу схемы сравнения, к запоминающему блоку и к выходу блока останова по контрольному коду, выход которого подключен к блоку управления. Это устройство позволяет осуществлять поразрядный контроль по модулю 2 и по контрольной сумме определенного массива чисел, считываемых с запоминающего .блока. Известное устройство имеет следующие недостатки:-малое быстродействие при проверке контрольного массива чисел в режиме-подсчета суммарного числа единиц всех разрядов этого массива из-за преобразования параллельного кода в последовательный, пркконтроле запоминающего блока не обнаруживаются парные ошибки в одноименных разрядах ни поразрядным контролем по МОДУЛЮ 2, ни подсчетом единиц массива чисел. Цель изобретения - увеличение быстродействия и повышение точности контроля. С этой целью предлагаемое устройство содержит блок свертки по модулю, выход которого подключен ко второму V входу преобразователя, а вход - к выходам выходного регистра, второй вход которого подключен к четвертому выходу блока управления. Введение блока свертки по модулю позволяет вместо последовательной разряд за разрядом передачи информации с преобразователя на счетный вход счетчика контрольного кода параллельно свернуть код чидла выходного регистра и просчитать все выхода свертки и сравнить получившееся в счетчике контрольного кода число с числом, записанным в блоке останова по контрольиому коду, и тем самым опрелелить правильность работы запоминающего блока. Быстродействие устройства увеличиваёт.ся при этом BN- раз,где М - количество разрядов в числе запоминающего блока, К - количество выходов свертки. Введение блока свертки по модулю в устройство для контроля позволяет обнаруживать парные ошибки-ложная , ложный О в одноимеиных разрядах лю-бой пары слов массива чисел с опреде-f ленной степенью вероятности. Это происходит из-за того, что хотя любая единичная ошибка в числе обнаруживается сверткой с вероятностью равной 1J 1 контроль однако при суммировании , считываеных символов массива слов мых, например, с выхода блока свертки по модулю 2, и сравнении полученного результата с контрольным кодом верояТность обнаружения ошибки при наличии парной ошибки равна 0,5. На чертеже представлена блок-схема предложенного устройства. Устройство содержит преобразователь 1, который,состоит из коммутатора 2 и преобразователя 3 параллельного кода в последовательный, счетчик 4 контроль ного кода, счетчик 5 адресов, блок 6 останова по (заданному) адресу, блок 7 останова по контрольному коду, блок 8 управления, запоминающий блок 9, выходной регистр 10, схему 11 сравнения и блок -12 свертки по модулю. Предложенное устройство позволяет увеличить быстродействие запоминающего блока в ре):(иМе контроля и обнаруживать парные ошибки в одноименных разрядах. Формула изобретения Устройство для контроля запоминающего блока по авт. св.№ 413530,о т личающееся тем, чт6, с целью повышения быстродействия и точности контроля,оно содержит блок свертки по модулю, выход которого подклйчен ко второму входу преобразователя,а вход - к выходам выходного регистра,второй вход которого подключен к четвертому выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1977 |

|

SU714503A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942164A1 |

| Устройство для контроля памяти | 1977 |

|

SU705526A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU877621A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841061A1 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU390578A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

Авторы

Даты

1979-01-15—Публикация

1977-07-08—Подача