(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для контроля памяти | 1977 |

|

SU714503A1 |

| ПРИСТАВКА К ЦИФРОВЫМ ВЫЧИСЛИТЕЛЬНЫМ МАШИНАМ | 1968 |

|

SU212628A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

I

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля памяти, содержащее блок памяти, блок управления, блок сравнения и блок формиро-вания кодов 1.

Недостатками этого устройства являются малая скорость работы и невысокая надежность.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство для контроля памяти, содержащее счетчик адреса, первый блок останова, счетчик контрольного кода, вход которого подключен к выходу коммутатора, а выход - к входу второго блока останова, одному из выходов устройства и первому входу блока сравнения, второй вход которого соединен с выходом выходного регистра, преобразователь параллельного кода в последовательный, вход которого подключен к входу выходного регистра и одному из входов устройства, а выход - к входу коммутатора, блок управления 2,

Однако это устройство не позволяет проверить все возможные комбинации смен состояний ячеек памяти .и выявить все переходные процессы и взаимодействия адресных формирователей блоков памяти, что сужает область применения устройства.

Целью настоящего изобретения является расширение области применения устройства за счет повышения эффективности и полноты контроля.

Поставленная цель достигается тем, что устройство содержит дополнительные счетчик, регистр и блок сравнения, причем входы дополнительных блока сравнения и регистра подключены к выходам счетчика адреса и дополнительного счетчика, вход которого соединен с одним из выходов блока управления, выход дополнительного блока сравнения подключен к одному из входов блока управления:, а выход дополнительного регистра соединен с входом первого блока останова и другим выходом устройства.

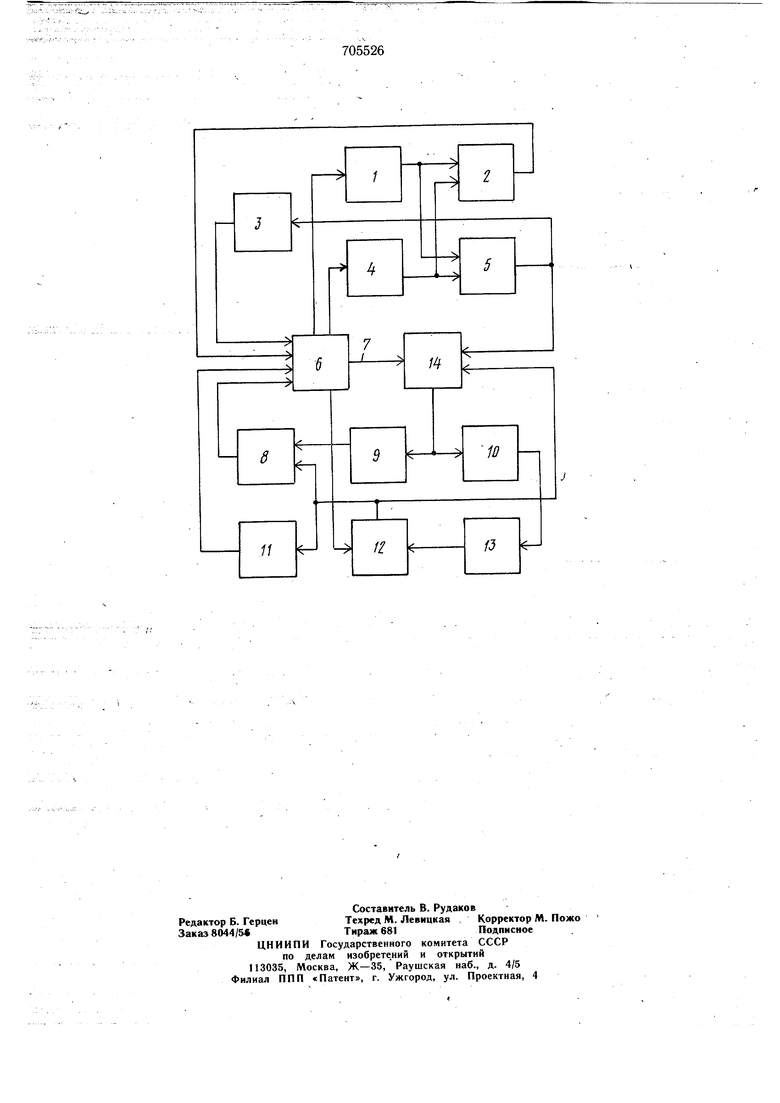

На чертеже представлена блок-схема устройства для контроля памяти.

Устройство содержит счетчик 1 адреса, дополнительный блок 2 сравнечгия, первый блок 3 останова, дополнительный счетчик 4, дополнительный р;егистр 5, блок б управления с выходом 7, блок 8 сравнения, выходной регистр 9, преобразователь 10 параллельного кода в последовательный, второй блок 11 останова, счетчик 12 контрольного кода и коммутатора 13. Входы и выходы устройства подключены к проверяемому блоку 14 памяти. Входы блока 2 и регистра 5 подключены к выходам счетчика 1, вход которого соединен с одним из выходов блока 6. Выход блока 2 подключен к одному из входов блока 6, а выход регистра 5 соединен с входом блока 3 и одним из выходов устройства. Устройство работает следующим образом. Перед началом работы в счетчике 1 устанавливают начальный адрес, а в блоке 3 останова - конечный адрес проверяемого массива ячеек памяти. В счетчик 12 заносят начальный, а в блок 11 - конечный код массива чисел, используемых для записи в проверяемые ячейки памяти. Блок 6 управления хранит программу с набором команд, определяющих порядок проверки блока 14 памяти по определенному алгоритму, и уг1равляет работой всех блоков устройства. Для проверки возможности обращения к оперативному блоку памяти по командам блока 6 управления, счетчик 1, суммируя единицы, формирует адреса проверяе.мых ячеек памяти, а счетчик 12 - проверочные коды; Далее происходит запись информации из счетчика 12 по адресу, переданному из счетчика 1 в регистр 5, считывание записанной информации в регистр 9 и сравнение содержимого регистра 9 и счетчика 12. При несовпадении записанной и считанной информации Характеристики выявленного брака считывают из регистров 5 и 9 и счетчика 12. Потом формируют другое проверочное число и повторяют цикл Запись-считывание-сравнение, переходят на проверку следующего адреса. Такая последовательность операций повторяется для всего массива проверяемых ячеек памяти. Для проверки оперативного блока памяти на полное функционирование, правильность адресации и чувствительность по току используют все возможные комбинации изменений состояний ячеек памяти. При этом использование этих ко.мбинаций в режиме Запись- считывание позволяет проверить время восстановления записи, а в режиме Считывание-считывание, - время выборки. При проверке всех возможных комбинаций смен состояний ячеек памяти в режиме Считывание-считывание команды проверяющей программы блока б управления, последовательно суммируя единицу в счетчик 1 адреса и передавая данный адрес в регистр 5, производят запись нулей из счет. чика 12 во все ячейки блока памяти, устанавливают в нулевое состояние счетчики 1 и 4 и в единичное состояние счетчик 1-2. При совпадении содержимого счетчика I с содержимым счетчика 4 по сигналу блока 2 сравнения блок 6 увеличивает содержимое счетчика 4 на единицу. Передают адрес из счетчика 1 в регистр 5 и производят запись в данную ячейку блока памяти единицы. Далее передают код из счетчика 4 в регистр 5 и производят считывание информации из первой ячейки памяти, передают код из счетчика 1 в регистр 5 и производят считывание информации из нулевой ячейки памяти, увеличивая одновременно содержимое счетчика 4 на единицу. Описанную процедуру повторяют для второй и нулевой ячеек памяти. Третьей и нулевой и т. д. до тех пор, пока не будет произведена проверка каждой такой пары «единиц и «нулей. После этого единицы записывают в первую ячейку памяти и повторяют все комбинации с первой ячейкой памяти. Данная процедура проверки повторяется для всех ячеек памяти. Затем проверяют запись и считывание нулей на фоне единиц, При проверке всех адресных переходов в режиме Запись-считывание после записи во все ячейки блока памяти нулей, по первому адресу, переданному в регистр 5 из счетчика 4, записывают единицы и производят считывание информации с нулевого адреса переданного в регистр 5 из счетчика 1. Затем по первому адресу записывают нули и считывают информацию с нулевого адреса, прибавляя одновременно в счетчик 4 единицу. Эта последовательность повторяется для второго и нулевого адреса и т. д. пока все адресные переходы относительно первого адреса не будут проверены. Далее процедура повторяется относительно первого адреса и т. д. до последнего. Описанная процедура проводится также с инверсной информацией. При этом счетчик 1 формирует адрес проверяемой ячейки памяти, счетчик 4 - адрес фоновой ячейки памяти, а блок сравнения 8 сигнализирует о совпадении кода счетчика 1 с кодом счетчика 4. При несовпадении записанной и считанной информации по сигналу блока 8 сравнения происходит прекращение проверки. При этом счетчик 1 указывает адрес проверяемой ячейки памяти, счетчик 4 - адрес фоновой ячейки, счетчик 12 - код, записываемый в проверяемую ячейку, а регистр 9 - код, считан 1ый с ячейки. После считывания характеристик неисправности устройство проверяет следующие ячейки памяти. Возможны многократное чтение информации из данной ячейки памяти с целью проверки сохран-. ности записанной информации, а также повторная запись и считывание информации

по неисправному адресу («долбление бракованной ячейки памяти).

При контроле постоянного блока памяти коммутатор-13 подключает к выходу преобразователя 10 вход счетчика 12 контрольного кода. В счетчик 1 адреса заносят начальный адрес, в блок 3 останова - конечный адрес проверяемого массива ячеек памяти, а в блок 11 останова - контрольную сумму единиц всех разрядов считываемой информации. По командам блока б управления происходит передача адреса проверяемой ячейки памяти из счетчика 1 в регистр 5, считывание информации из данной ячейки памяти и изменение адреса на единицу в счетчике 1.

В процессе считывания информации из проверяемого массива ячеек памяти регистр 9 подсчитывает поразрядную сумму по модулю два, а счетчик 12 - сумму единиц всех разрядов считанной информации. Прекращение проверки осуществляется по сигналам блока 3 останова или блока 11 останова. В первом случае разница между содержимым блока 11 останова и содержимым счетчика 12 контрольного кода показывает общее число ощибок из-за неправильного чтения единиц в разных разрядах проверяемого массива ячеек памяти. Во втором случае разница между содержимым счетчика 12 контрольного кода и табличным значением контрольного кода адреса, на котором прекратилилась проверка, указывает количество ощибок из-за неправильного чтения нулей в разных разрядах. Разряды; в которых произощло неправильное чтение информации, определяют, сравнивая содержимое выходного регистра 9 с табличным значением поразрядной контрольной суммы по модулю два считанной информации. Количество ощибок в каждом разряде определяют путем подсоединения к входу счетчика 12 выхода определенного разряда с помощью коммутатора 13, а в блок 11 заносят контрольный код проверяемого разряда. .Время выборки проверяют путем последовательного чтения из ячеек памяти с различной (по возможности - противоположной) информацией, адреса которых находятся в счетчике 1 адреса и дополнительном счетчике 4.

Предложенное устройство позволяет использовать все возможные, комбинации изменений состояний ячеек. Используя все адресные переходы, блок памяти проверяют на полное функционирование, правильность адресации и чувствительность по току. При этом проверка работы блока в режиме Запись-считывание позволяет проконтролировать время восстановления записи, а в режиме 3 Считывание-считывание - время выборки.

X Возможность проверки указанных характеристик блока памяти позволяет повысить эффективность и полноту контроля памяти.

Формула изобретения

5

Устройство для контроля памяти, содержащее счетчик адреса, первый блок останова, счетчик контрольного кода, вход которого подключен к выходу коммутатора, а

0 выход- к входу второго блока останова, одному из выходов устройства к первому входу блока сравнения, второй вход которого соединен с выходом выходного регистра, преобразователь параллельного кода в последовательный, вход которого подключен

5 к входу выходного регистра и одному из входов устройства, а выход - к входу коммутатора , и блок управления, отличающееся тем, что, с целью расширения области применения устройства за счет повыщения

0 эффективности и полноты контроля памяти, оно содержит дополнительные счетчик , регистр и блок сравнения, причем входы дополнительных блока сравнения и регистра подключены к выходам счетчика адреса и дополнительного счетчика, вход которого сое5динен с одним из выходов блока управления, выход дополнительного блока сравнения подключен к одному из входов, блока управления, а выход дополнительного регистра соединен с входом первого блока останова и

0 другим выходом устройства.

Источники информации,

принятые во внимание при экспертизе

5

№ 413530, кл. G 11 С 29/00, 1972 (прототип).

Авторы

Даты

1979-12-25—Публикация

1977-09-02—Подача