/Ч-1

ный сумматор составлен из

-2 одноIg2

разрядных двоичных с шматоров и нолусумматоров. .

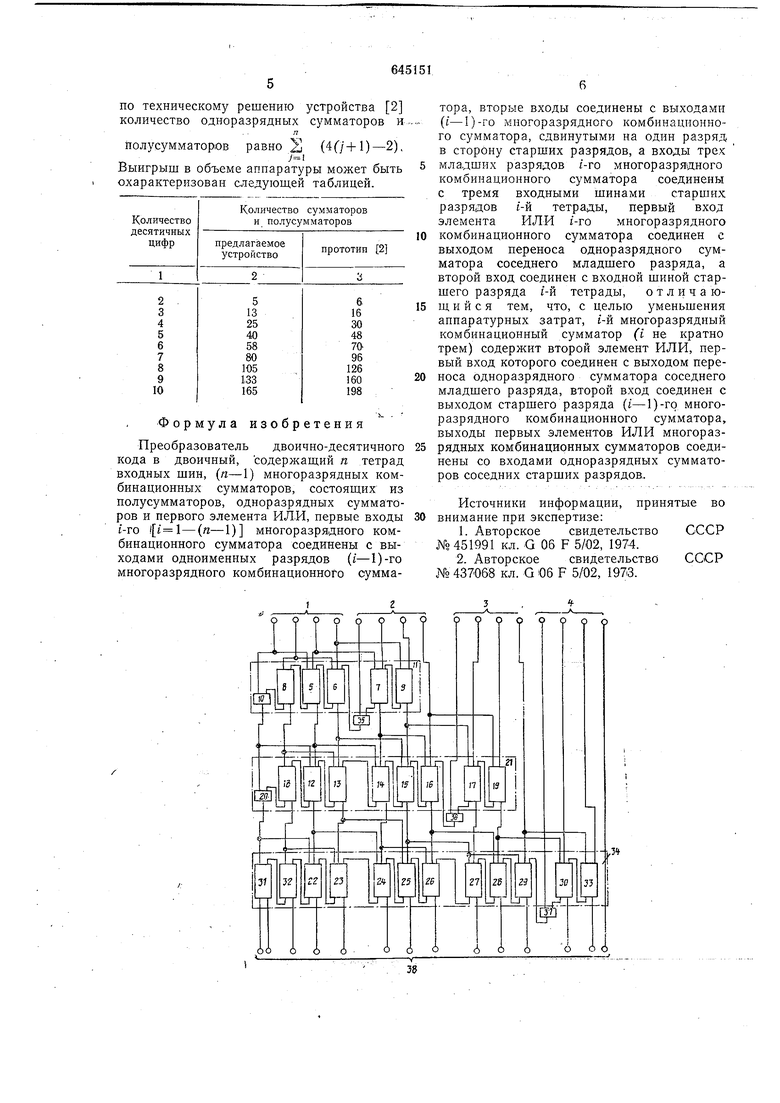

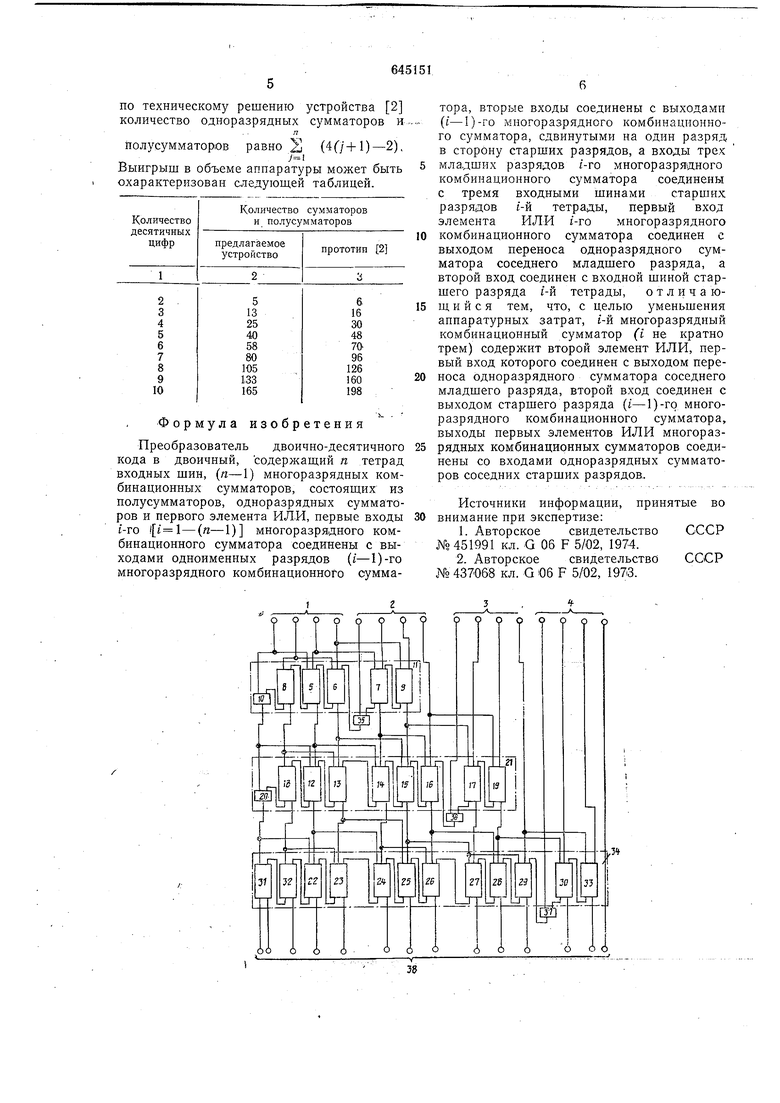

Сущность изобретения поясняется чертежом, на котором изображен преобразоваель и разрядных двоично-десятичных кодов для .- : :.:.-,,

Устройство содержит тетрады входных ин У-4, двоичные одноразрядные, суммаоры 5-7, полусумматоры 8-9 и элемент ИЛИ :10, которые составляют многоразрядный комбинационный сумматор Л; двоичные одноразрядные сумматоры 12-17, полусумматоры 1/5-1 9 и элемент. ИЛИ 20, коорые составляют многоразрядный комбинационный сумматор 21; двоичные одноразрядные сумматоры 22-30, полусумматоры 31-5«3, которые составляют многоразрядный комбинационный сумматор 34, элементы .ИЛИ 35-37, а также выходные полюса 38.- - - ,.;....--.-v,-..-:-,,r- ,-:.- :

Первый, второй, третий, четвертый входные полюса тетрады / (счет ведется слева направо) подключены соответствённо к элементам 10 и 5, 8 н 6, 5 и 7, 6 и 9 многоразрядного комбинационного сумматора,//.

Первые входные полюса тетрад 2, 3, 4 подсоединены соответственно к одному вхоу элементов ИЛИ 35, 3-6, 37, другие входы которых подсоеДинень соответственно к выХодам одноразрядных сумматоров / f7, 30, а выходы схем ИЛИ подключены соответственно к входам элементов 6, 16, 29. Второй/ и третий разряды тетрад 2, 3, 4 подсоединеHbj; соответственно к элементам 7 и Я /7 и 19, 30 и 33. (Каждый i-тый выход многоразрядных комбинационных сумматоров //, 21 подключены соответственно к /-тому и (t-2)-му входам комбинационных сумматоров 21, 34. Выходы сумматора 34 подсоединены к выходным шинам 38 устройства.

Старшие разряды мн огоразрЯДньи комбинационных сумматоров // и 2/ выполнены в виде элементов ИЛИ.

Устройство работает следующим образом. На тетрадь i/-4 входных полюсов поаётся совокупность единичных и нулевых сигналов - код числа, например, 10011001100Н001.

На входы двоичных одноразрядных сумматороб и полусумматоров 5-9 и элемент ИЛИ 10, составляющих многоразрядный комбинационный сумматор ,// через тетрады входных полюсов I/ и 2 поступает код rOQliOOl. На сумматоре // происходит сложение Bicex кодов:

1)кода, поступающего через входные полюса тетрады ,2; ,

2)кода, поступающего через входные полюса тетрады / и сдвинутого относительно предыдущего на один разряд влево;

3)кода, поступающего через входные гголюса тетрады / и сдвинутого относйгтёльно предыдущего на два разряда влево

-f 1001 1001 1001

llOOOIl

На выходе сумматора /,/ появляется код 1100011. Этот код и код 1001, поданный на входные полюса тетрады 3, поступают на входы одноразрядных сумматоров и полусумматоров ,/i5-i/.9 и элемент ИЛИ 20, составляющих многоразрядный сумматор 21. На этом сумматоре происходит суммирование трех кодов:

1)кода, поступающего через входные щины тетрады 3;,

2)кода, пбётупающего с выхода сумматора /I/ и сдвинутого на один разряд влево относительно предыдущего;

3)кода, поступающего с выхода сумматора // и сдвинутого на два разряда относительно предыдущего.

+1001

ПОООМ 1100011

lllllOOlM

На выходе сумматора 311 появляется код lllllOOllil. На выходы двоичных сумматоров и полусумматоров 22-33, составляющих многоразрядный сумматор 34 поступает через входные полюса тетрады 4 код 1001 и с выхода сумматора 21 код llMliOOlU. На сумматоре 34 происходит

сложение трех кодов:

1) кода, поступающего через входные шины тетрады 4;

2) кода, поступающего с выхода сумматора 2il и сдвинутого относительно предыдущего на один разряд влево;

3) кода, поступающего с выхода сумматора 21 и сдвинутого относительно предыдущего на два разряда влево :. + 1001

1111100111

11,11100111

10011 юшЖГГ

На вь1ходе сумматора 34 появляется код 100.1 llOOOOl111, который является двоичным

эквивалентом двоично-десятичного кода (1001,10.01.1001.1001) 10. Таким образом, предлагаемое устройство реализует преобразование двоично-десятичного числа в двоичное.

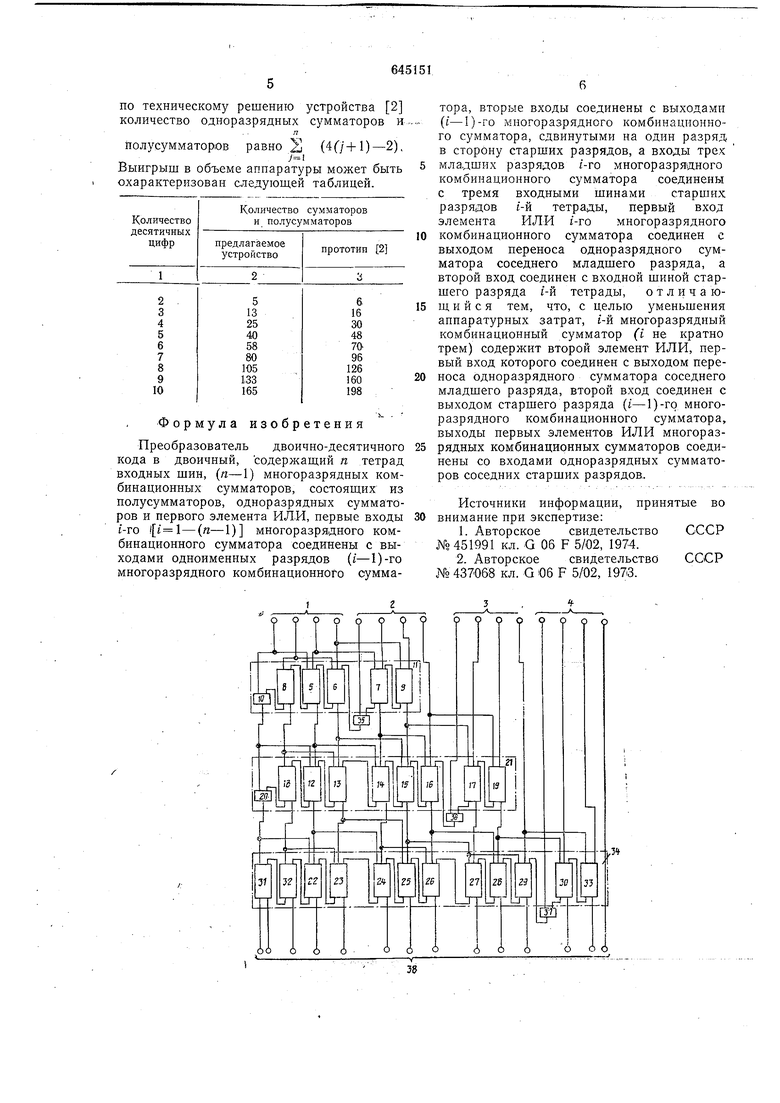

В предлагаемом устройстве количество одноразрядных сумматоров и полусумматоров, составляющих параллельные многоразя-1 /

y/FLfi

-2

Ulg2

рядные сумматоры равно

где / - номер многоразрядного комбинационного сумматора, п - число двоично-десятичнь1х разрядов, а (i& ближайшее целое, но такое, что , У наиболее близкого

Авторы

Даты

1979-01-30—Публикация

1977-02-14—Подача