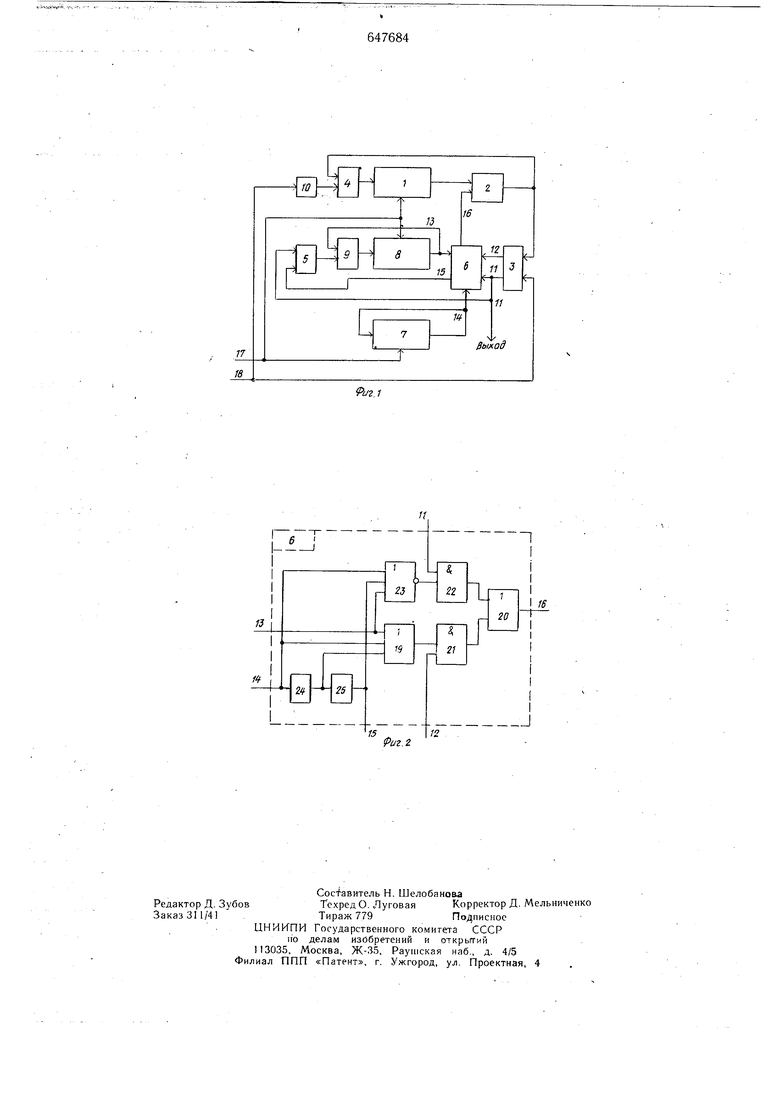

гательного регистра и с единичным входом старшего разряда вспомогательного регистра, второй выход блока формирования цифры соединен со вторым входом сумматора, выход которого подключен ко второму входу первого элемента И и ко входу триггера, а также тем, что блок формирования цифры содержит: первый и второй элементы ИЛИ, первый и второй элементы И, элемент ИЛ И-НЕ, первый и второй элементы задер-жки,. первый вход первого элемента ИЛИ подключен к первому входу элемента ИЛИ-НЕ и ктретьему входу блока формирования цифры, четвертый вход блока формирования цифры подключен ко вторым входам первого элемента ИЛИ и элемента ИЛИ-НЕ, через первый элемент задержки - к третьему входу первого элемента ИЛИ и через первый и второй элементы задержки - к третьему входу элемента ИЛИ-НЕ и к первому выходу блока формированияцифры, третий вход блока формирования цифры подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента .И, первый вход которого соединен с выходом элемента , а второй вход - с первым входом блока формирования цифры, выход второго элемента ИЛИ является вторым выходом блока формирования цифры. На фиг. I представлена схема устройства; на фиг. 2 - возможный вариант реализации,блока формирования цифры. Схема устройства содержит: регистр oneранда I, сумматор 2, триггер 3, первый и второй элементы И 4, 5, блок 6 формирования цифры, вспомогательный регистр 7, регистр коррекции 8, элемент ИЛИ 9, элемент НЕ 10, первый, второй, третий и четвертый входы соответственно П, 12, 13, 14 блока формирования цифры, первый и второй выходы 15 и 16 блока формирования цифры, первый и второй тактирующие входы 17 и 18 устройства. Схема блока формирования цифры (фиг. 2) содержит: первый и второй элементы ИЛИ 19, 20, первый и второй элементы И 21, 22, элемент ИЛИ-НЕ 23, первый и второй элементы задержки 24, 25 соответственно. .Регистр I имеет (п + 5) разрядов, регистр 7- (п + 3) разрядов и регистр 8-(п-f 4) разрядов, где п - разрядность операнда. В исходном состоянии в регистр 1 записан операнд, в регистре 7 - единиц а записана в третьем . слетва разряде, в регистре 8 - все нули, триггер 3 находится д нулевом состоянии. На входах 12, 13, 14 существует нулевой сигнал, а на входе 11 - единичньш сигнал. Поэтому на В1ыходе 15 блока формирования цифры будет присутствовать нулевой сигнал, а на выходе 16 - «1. образом, на выходе переноса сумматора будет сформирован единичный сигнал, а на выходе суммы - сигнал, идентичный младшей цифре регистра операнда. Будем считать, что в каждом i-м такте (i 1,2..., п -f 4) каждого цикла на шине 17 появляется единичный тактирующий сигнал, а в (п + 4)-м такте каждого цикла на шине 18 появляется единичный тактирующий сигнал. Цикл работы устройства состоит из п + 4 тактов. Рассмотрим работу устройства в i-м такте произвольного цикла (i , 2..., п + 4). На тактирующей щине 7 появляется единичный сигнал, который проходит на цепи сдвига вправо на один разряд регистров 1, 7 и 8. В освободившийся старший разряд регистра 1 через элемент И 4 записывается цифра, полученная на выходе суммы сумматора 2 (это возможно ввиду отсутствия единичного сигнала на шине 18 и, следовательно, наличия его на выходе элемента НЕ 10). В старший разряд регистра 7 записывается цифра, бывшая в младшем разряде этого регистра в предыдущем такте. Если двумя тактами ранее в младшем разряде регистра 7 находилась единица, то формирователь 6 формирует единичный сигнал на шине 15. Если в этом же такте триггер 3 находится в нулевом состоянии, то на выходе элемента И 5 и элемента ИЛИ 9 появляется единичный сигнал и в следующем такте в старший разряд регистра 8 записывается единица. Во всех остальных случа.ях в старший разряд регистра 8 записывается цифра, бывшая в предыдущем такте в младшем разряде этого регистра. Если триггер 3 находится в нулевом состоянии (т.е. на шине II присутствует единичный сигнал), то на.втором выходе формирователя 6 единичный сигнал появится только в случае отсутствия единичного сигнала на шинах 13, 14 и 15 (отсутствия единиц в младших разрядах регистра 8 в данном такте ирегистра 7 в этом такте и двумя тактами ранее). Если же триггер 3 находится в-единичном состоянии (на шине 12 установлен ,. ., единичный сигнал), то единичный сигнал на выходе 16 появится в следующих случаях: либо в младшем разряде регистра 8 записана единица (на шине 13 имеется едиг ничный .сигнал), либо в младшем разряде регистра 7 единица находилась в прошлом такте или находится в этом такте (что соответствует единичному сигналу на шине 14). На входы сумматора 2 поступают сигналы с блока 6 с цепи переноса сумматора, а также сигнал из регистра 1, cootBeTCTByющий значению цифры из его младшего разряда. В (п + 4)-м такте каждого цикла на тактирующей 1.иине 18 появляется единичный сигнал, который поступает на вход элемента НЕ 10 и на синхронизирующий

вход триггера 3. На выходе э.пемента 10 единичный сигнал исчезает и в старший разряд регистра I занисывается ноль в следующем такте. Триггер 3 изменяет свое состояние в соответствии с сигналом на выходе суммы сумматора 2. Кроме этого в первом цикле одновременно с появлением сигнала на шине 18 осуществляется сброс в нуль регистра 8. Результат появляется на выходной шине, связанной . с нулевым выходом триггера 3, последовательно со старших разрядов.

Очередная цифра результата формируется в конце каждого цикла в его (п + 4)-м такте.

Рассмотрим цифровой пример. Пусть необходимо вычислить квадратный корень из 9 (1001)а6. Результат будет равен 3 (0011)9Ь

Предложенное устройство является устройством последовательного действия и применение в нем регистров в интегральном исполнении на основе МДП-структур позволяет значительно снизить стоимость, уменьшить габариты устройства и повысить его надежность.

формула изобретения

1. Устройство для извлечения квадратного корня, соДержаше е регистр операнда, вспомогательный регистр, сумматор, первый вход которого подключен к единичному выходу младшего разряда регистра операнда, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр коррекции, блок формирования цифры, триггер, первый и второй элементы И, элементы ИЛИ и НЕ, первый тактирующий вход устройства подключен к первым входам регистра операнда, вспомогательного регистра и регистра коррекции, второй тактирующий вход устройств.а подключен к синхронизирующему входу триггера и ко входу элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого подключен к единичному входу старшего разряда регистра операнда, первый вход элемента ИЛИ соединен с единичным выходом младшего разряда регистра коррекции,, единичный вход старшего рязряда которого подключен

к выходу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым выходом блока формирования цифры, а его второй вход подключен к нулевому выходу триггера, первому входу блока формирования цифры и выходу устройства, единичный выход триггера подключен ко второму входу блока формирования цифры, третий вход которого подключен к выходу регистра коррекции, а четвертый вход соединен с единичным выходом младшего разряда вспомогательного регистра и с единичным входом старшего разряда вспомогательного регистра, второй выход блока формирования цифры соединен со вторым входом сумматора, выход которого подключен ко втором у входупервого элемента И и ко входу триггера. 2. Устройство по п., 1, отличающееся тем, что блок формирования цифры содержит первый и второй элементы ИЛИ, первый и

второй элементы И, элемент ИЛИ-НЕ, первый и второй элементы задержки, первый вход первого элемента ИЛИ подключен к первому входу элемента ИЛИ-НЕ и к третьему входу блока формирования циф5 рьт, четвертый вход блока формирования цифры подключен ко вторым входам первого элемента ИЛИ и элемента ИЛИ--НЕ, через первый элемент задержки - к третьему входу первого элемента ИЛИ и через первый и второй элементы задержки - к третье0му входу элемента ИЛИ--НЕ и к первому выходу блока формирования цифры, второй вход блока формирования цифры подключен к первому входу первого элемента И, второй вход которого подключен к выхо5 ДУ первого элемента ИЛИ, а выход - к первому входу второго, элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом элемента ИЛИ-НЕ, а второй вход - с первым входом блока формирования циф.ры, выход второго элемента ИЛИ является вторым выходом блока формирования цифры.

Источники информации, принятые во внимание при экспертизе

1.Авторское-свидетельство СССР № 435522, кл. G 06 F 7/38, 1972.

2.Патент Японии № 50-7900, кл. 97{7)Е32, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для алгебраического сложения чисел | 1976 |

|

SU638959A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

Авторы

Даты

1979-02-15—Публикация

1977-01-10—Подача