1

Изобретение относится к цифровой вычислительной технике.

Известны накапливающие сумматоры, содержащие в каждом разряде счетный триггер и логические элементы для получения сигнала переноса 1, 2. Эти устройства не имеют достаточного быстродействия и надел ности выработки в каждом разряде сигнала переноса. Наиболее близким к изобретению является накапливающий сумматор с запоминанием переноса, содержащий в каждом разряде счетный триггер и триггер для запоминания переноса 3. Однако и он имеет низкое быстродействие. Целью изобретения является повыщение быстродействия. В описываемом накапливающем сумматоре с запоминанием переноса, содерлсащем в каждом разряде счётный триггер, триггер переноса и элемент И-ИЛИ-НЕ, первая группа входов которого подключена ко входу данного разряда сумматора и управляющей щине записи, вторая группа входов т-к единичному выходу триггера переноса предыдущего разряда и управляющей щине разрешения переноса, а выход элемента И-ИЛИ-НЕ подключен к счетному входу счетного триггера данного разряда сумматора, это достигается тем, что в нем триггеры переноса выполнены на двух элементах И-ИЛИ-

НЕ и каждый четный разряд сумматора содержит элемент НЕ, причем выход первого элемента И-ИЛИ-НЕ триггера переноса каждого разряда сумматора соединен с

единичным выходом этого триггера и пер-, вым входом первой группы входов второго элемента И-ИЛИ-НЕ этого же триггера, второй вход первой группы входов которого соединен с управляющей шиной сброса,

первый вход второго элемента И-ИЛИ- НЕ триггера переноса подключен к единичному выходу счетного триггера этого же разряда сумматора, а выход второго, элемента И-ИЛИ-НЕ триггера переноса

подключен к первым входам первой и второй групп входов первого элемента И- ИЛИ-НЕ триггера переноса, второй вход первой группы входов первого элемента И-ИЛИ-НЕ триггера переноса каждого

нечетного разряда подключен к единичному/ выходу триггера переноса предыдущего разряда, а второй вход первой группы входов первого элемента И-ИЛИ-НЕ триггера переноса каждого четного разряда

подключен через элемент НЕ ко входу данного разряда сумматора, вторые входы второй группы входов второго элемента И- ИЛИ-НЕ триггера переноса-каждого нечетного и четного разрядов сумматора подключены соответственно ко входу данного разряда сумматора и единичному выходу триггера переноса предыдущего разряда, второй вход второй группы входов первого элемента И-ИЛИ-НЕ триггера переноса каждого разряда подключен к нулевому выходу счетного триггера того же разряда.

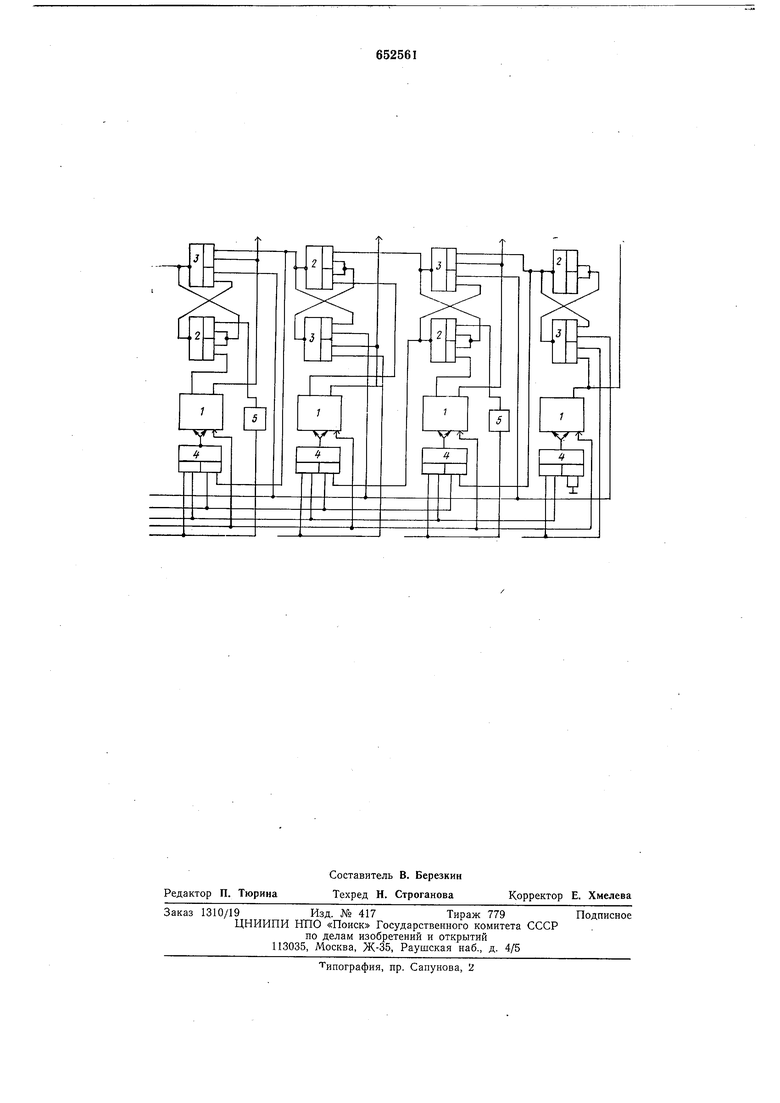

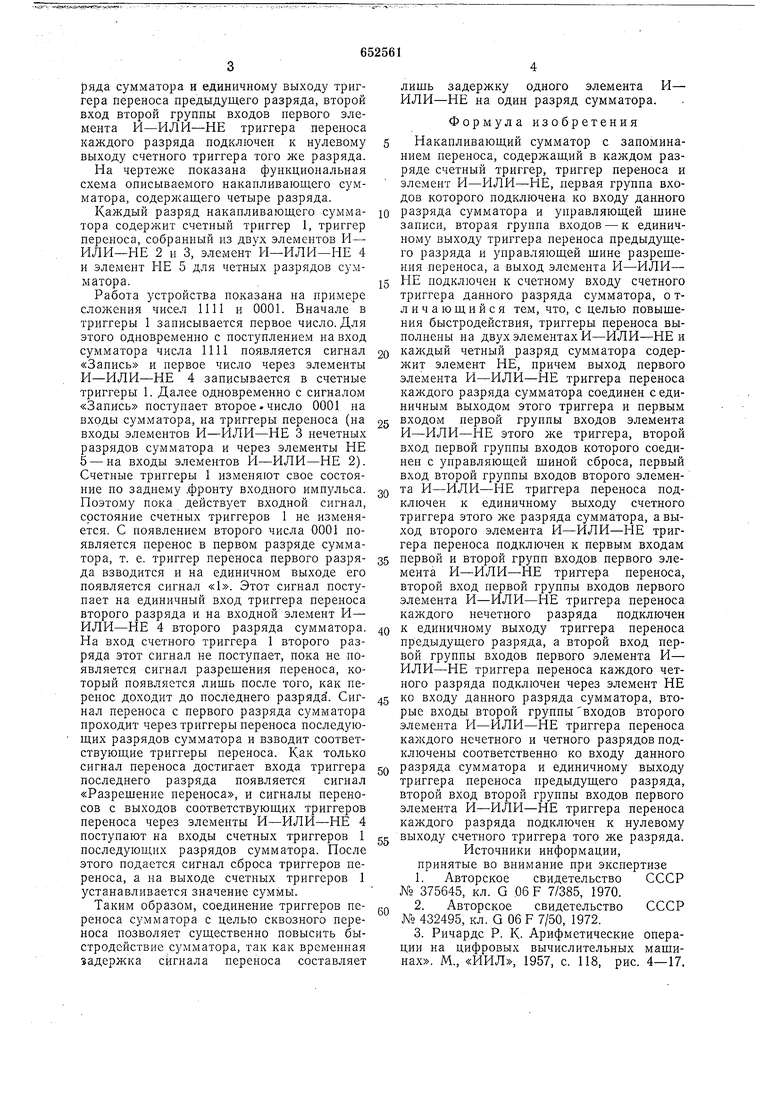

На чертеже показана функциональная схема описываемого накапливающего сумматора, содержащего четыре разряда.

Каждый разряд накапливающего сумматора содержит счетный триггер 1, триггер переноса, собранный из двух элементов И- ИЛИ-НЕ 2 и 3, элемент И-ИЛИ-НЕ 4 и элемент НЕ 5 для четных разрядов сумматора.

Работа устройства показана на примере сложения чисел 1111 и 0001. Вначале в триггеры 1 записывается первое число. Для этого одновременно с поступлением на вход сумматора числа 1111 появляется сигнал «Запись и первое число через элементы И-ИЛИ-НЕ 4 записывается в счетные триггеры 1. Далее одновременно с сигналом «Запись поступает второе-число 0001 па входы сумматора, на триггеры переноса (на входы элементов И-ИЛИ-НЕ 3 нечетных разрядов сумматора и через элементы НЕ 5 - на входы элементов И-ИЛИ-НЕ 2). Счетные триггеры 1 изменяют свое состояние по заднему .фропту входпого импзльса. Поэтому пока действует входной сигнал, состояние счетных триггеров 1 не изменяется. С появлением второго числа 0001 появляется перенос в первом разряде сумматора, т. е. триггер переноса первого разряда взводится и на единичном выходе его появляется сигнал «1. Этот сигнал поступает на единичный вход триггера переноса второго разряда и на входной элемент И- ИЛИ-НЕ 4 второго разряда сумматора. На вход счетного триггера 1 второго разряда этот сигнал не поступает, пока не появляется сигнал разрешения переноса, который появляется лишь после того, как перенос доходит до последнего разряда . Сигнал переноса с первого разряда сумматора проходит через триггеры переноса последующих разрядов сумматора и взводит соответствующие триггеры переноса. Как только сигнал переноса достигает входа триггера последнего разряда появляется сигнал «Разрешение переноса, и сигналы переносов с выходов соответствующих триггеров переноса через элементы И-ИЛИ--НЕ 4 поступают на входы счетных триггеров 1 последующих разрядов сумматора. Носле этого подается сигнал сброса триггеров переноса, а на выходе счетных триггеров 1 устанавливается значение суммы.

Таким образом, соединение триггеров переноса сумматора с целью сквозного переноса позволяет существенно повысить быстродействие сумматора, так как временная задержка сигнала переноса составляет

лишь задержку одного элемента И- ИЛИ-НЕ на один разряд сумматора.

Формула изобретения

Накапливающий сумматор с запоминанием переноса, содержащий в каждом разряде счетный триггер, триггер переноса и элемент И-ИЛИ-НЕ, первая группа входов которого подключена ко входу данного

разряда сумматора и уиравляющей щине записи, вторая группа входов - к единичному выходу триггера переноса предыдущего разряда и управляющей шине разрешения переноса, а выход элемента И-ИЛИ-

НЕ подключен к счетному входу счетного триггера данного разряда сумматора, о тличающийся тем, что, с целью повышения быстродействия, триггеры переноса выполнены на двух элементах И-ИЛИ-НЕ и

каждый четный разряд сумматора содержит элемент НЕ, причем выход первого элемента И-ИЛИ-НЕ триггера переноса каждого разряда сумматора соединен с единичным выходом этого триггера и первым

входом первой группы входов элемента И-ИЛИ-НЕ этого же триггера, второй вход первой группы входов которого соединен с управляющей шиной сброса, первый вход второй группы входов второго элемента И-ИЛИ-НЕ триггера переноса подключен к единичному выходу счетного триггера этого же разряда сумматора, а выход второго элемента И-ИЛИ-НЕ триггера нереноса подключен к первым входам

первой и второй групп входов первого элемента И-ИЛИ-НЕ триггера переноса, второй вход первой группы входов первого элемента И-ИЛИ-НЕ триггера переноса каждого нечетного разряда подключен

к единичному выходу триггера переноса предыдущего разряда, а второй вход первой группы входов первого элемента И- ИЛИ-НЕ триггера переноса каждого четного разряда подключен через элемент НЕ

ко входу данного разряда сумматора, вторые входы второй группы входов второго элемента И-ИЛИ-НЕ триггера переноса каждого нечетного и четного разрядов подключены соответственно ко входу данного

разряда сумматора и единичному выходу триггера переноса предыдущего разряда, второй вход второй группы входов первого элемента И-ИЛИ-НЕ триггера переноса каждого разряда подключен к нулевому

выходу счетного триггера того же разряда.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 375645, кл. G 06 F 7/385, 1970.

2. Авторское свидетельство СССР № 432495, кл. G 06 F 7/50, 1972.

3. Ричарде Р. К. Арифметические операции на цифровых вычислительных машинах. М., «ИИЛ, 1957, с. 118, рис. 4-17,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1971 |

|

SU647686A1 |

| Параллельный накапливающий сумматор | 1978 |

|

SU744568A2 |

| Параллельный накапливающий сумматор | 1975 |

|

SU581470A1 |

| Накапливающий сумматор с запоминанием переноса | 1978 |

|

SU943710A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Накапливающий сумматор | 1976 |

|

SU691850A1 |

| Устройство для умножения | 1980 |

|

SU974369A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

Авторы

Даты

1979-03-15—Публикация

1976-10-04—Подача