1

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ различного назначения.

Современные микросхемы памяти (МП), используемые для построения полупроводниковых ЗУ, представляют собой БИС с высокой степенью интеграции, производство которых связано с большими технологическими трудностями, что приводит к появлению дефектных запоминающих ячеек и снижает процент выхода годных микросхем.

Эффективным путем повышения выхода годных МП является обеспечение необходимой ремонтопригодности изготавливаемых микросхем, т.е. такая их организация, которая позволяла бы устранить наиболее часто встречающиеся неисправности в МП в ходе изготовления.

Известны программируемые постоянные запоминающие устройства, которые содержат накопитель, адресные и числовые фор.мирователи, различные дешифраторы 1.

Наиболее близким к данному изобретению является устройство, содержащее адресный формирователь, выходы которого подключены к соответствующим входам дешифратора числа, а выходы дещифратора числа подключены соответственно ко входам числовых формирователей, выходы которых подключены к соответствующим входам накопителя, выходы накопителя соединены со входами разрядного дешифратора, выходы которого подключены к соответствующим входам усилителей считывания 2.

Недостатком известных устройств является невозможность устранения неисправностей МП в ходе изготовления, т.е. низкая надежность устройства.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что предлагаемое устройство содержит коммутатор и дополнительные числовые формирователи, входы которых подключены к соответствующим выходам дещифратора числа, а выходы - ко входам коммутатора, выходы коммутатора подключены ко входам разрядного дешифратора.

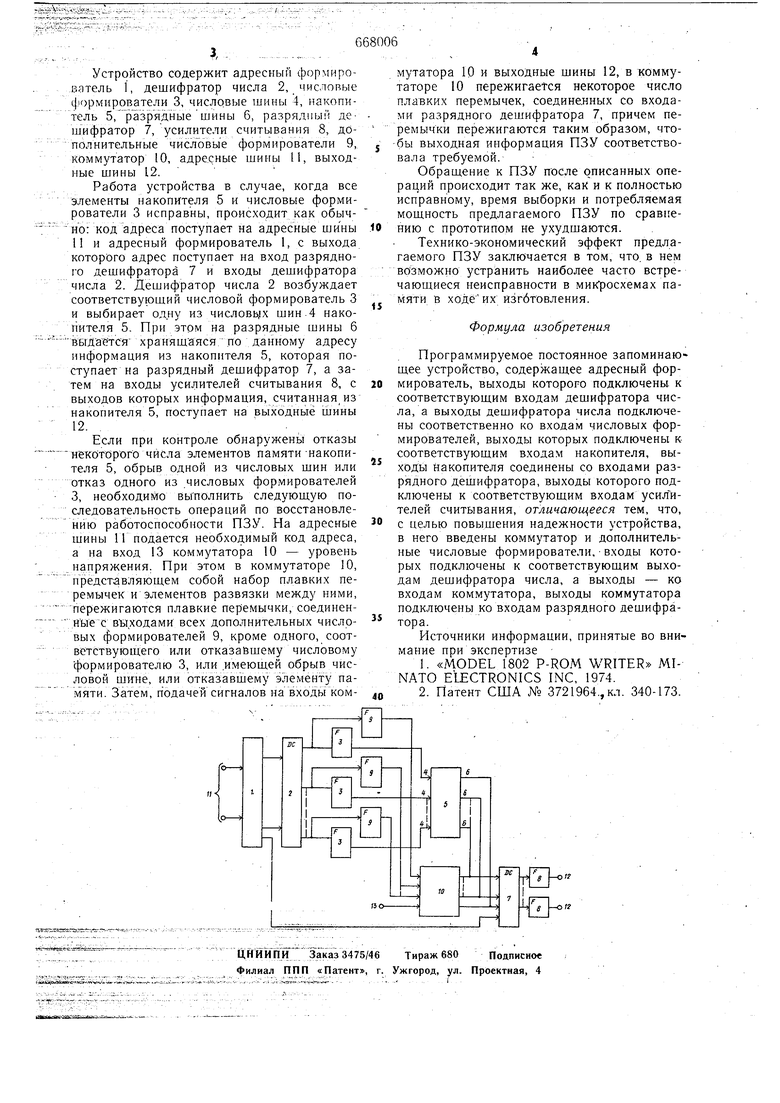

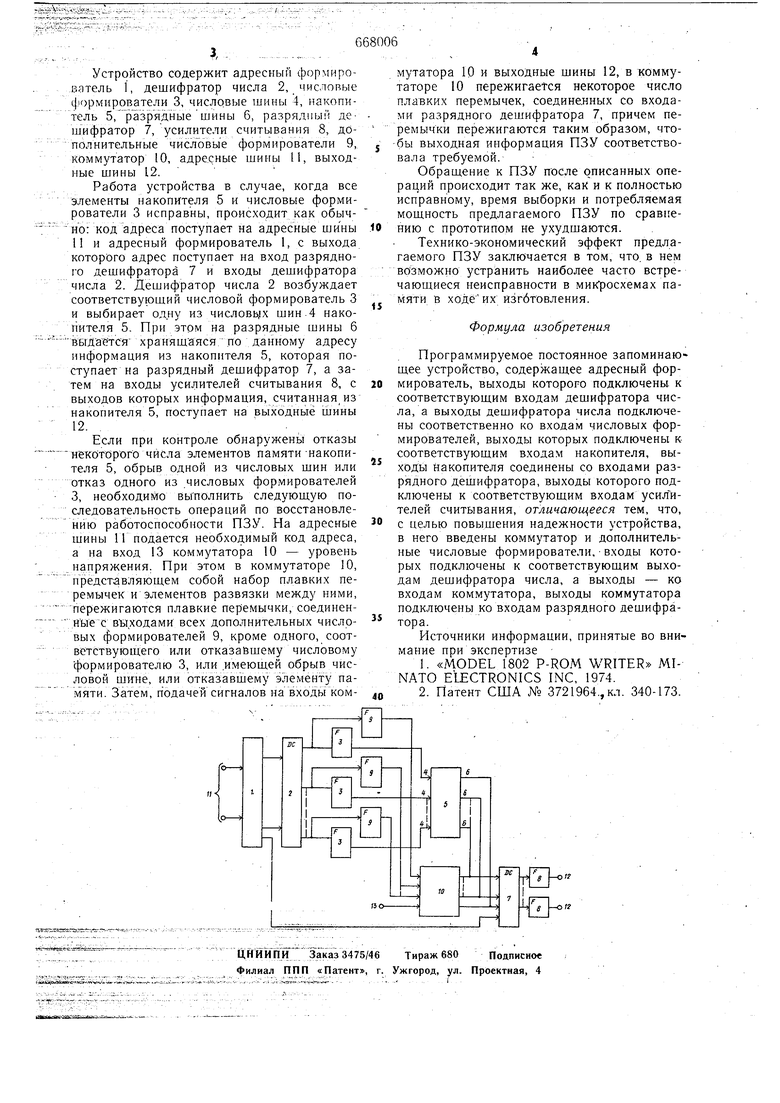

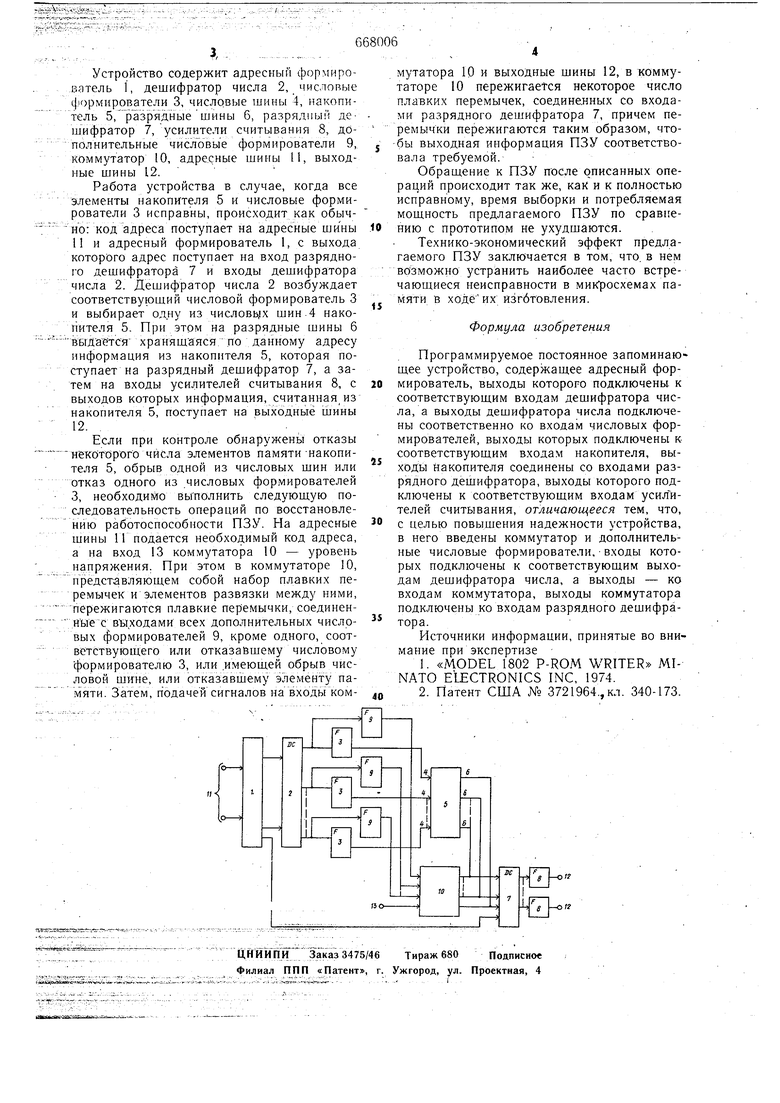

На чертеже приведена блок-схема предлагаемого программируемого запоминающего устройства .

Устройство содержит адресный формирователь 1, дешифратор числа 2, числовые ((.юрмнрователи 3, числовые шины 4, накопитель 5, разрядныешины 6, разрядпыГ дешифратор 7, усилители считывания 8, дополнительные числовые формирователи 9, коммутатор 10, адресные шины 11, выходные шины 12.

Работа устройства в случае, когда все элементы накопителя 5 и числовые формирователи 3 исправны, происходит как обыч но: код адреса поступает на адресные шины 11 и адресный формирователь 1, с выхода которого адрес поступает на вход разрядного дешифратора 7 и входы дешифратора числа 2. Дешифратор числа 2 возбуждает соответствующий числовой формирователь 3 и выбирает одну из числовьд шин 4 накопителя 5. При этом на разрядные шины 6

йыдается храняшаяся; по данному адресу информация из накопителя 5, которая поступает на разрядный дешифратор 7, а затем на входы усилителей считывания 8, с выходов которых информация, считанная из накопителя 5, поступает на выходные илины 12. .

Если при контроле обнаружень отказы

некоторого чйс,ла элементов памяти-накопителя 5, обрыв одной из числовых шин или отказ одного из числовых фор.мирователей 3, необходимо выполнить следуюшую последовательность операций по восстановлению работоспособности ПЗУ. На адресные шины 11 подается необходимый код адреса, а на вход 13 коммутатора 10 - уровень напряжения. При этом в коммутаторе 10, представляюшем собой набор плавких перемычек и элементов развязки между ними, пережигаются плавкие перемычки, соединенные с выходами всех дополнительных числовых формирователей 9, кроме одного, соотвстствуюш,его или отказавшему числовому формирователю 3, или .имеюш,ей обрыв числовой шине, или отказавшему элементу памяти. Затем, подачей сигналов на входы коммутатора 10 и выходные шины 12, в коммутаторе 10 пepeжигaetcя некоторое число плавких перемычек, соединенных со входами разрядного дешифратора 7, причем перемычки пережигаются таким образом, чтобы выходная информация ПЗУ соответствовала требуемой.

Обращение к ПЗУ после описанных операций происходит так же, как и к полностью исправному, время выборки и потребляемая мощность предлагаемого ПЗУ по сравнению с прототипом не ухудшаются.

Технико-экономический эффект предлагаемого ПЗУ заключается в том, что. в нем возможно устранить наиболее часто встречающиеся неисправности в микросхемах памяти в ходе их изгбтовления.

Формула изобретения

Программируемое постоянное запоминающее устройство, содержащее адресный формирователь, выходы которого подключены к соответствующим входам дешифратора числа, а выходы дешифратора числа подключены соответственно ко входам числовых формирователей, выходы которых подключены к соответствующим входам накопителя, выходы накопителя соединены со входами разрядного дещифратора, выходы которого подключены к соответствующим входам усилителей считывания, отличающееся тем, что, с целью повышения надежности устройства, в него введены коммутатор и дополнительные числовые формирователи, входы которых подключены к соответствующим выходам дешифратора числа, а выходы - ко входам коммутатора, выходы коммутатора подключены ко входам разрядного дешифратора.

Источники информации, принятые во внимание при экспертизе

1.«MODEL 1802 P-ROM WRITER MINATO EUECTRONICS INC, 1974.

2.Патент США № 3721964., кл. 340-173.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1439684A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU641503A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746731A1 |

Авторы

Даты

1979-06-15—Публикация

1976-09-13—Подача