(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ НА 10 Изобретение относится к области вычислител ной техники и предназначено для деления на десять последовательности входных импульсов. Известны делители частоты, каждый разряд которых содержит триггеры памяти, коммутационные триггеры и схемы И-НЕ 1,2,31. Первые два из известных устройств содержат большое количество оборудования и Характери зуются низкой надежностью Третье из известных устройств является более совершенным и содержит четыре триггера Памяти, три коммутаилонных триггера, и четыре схемы И-НЕ, причем единичный выход первого триггера памяти соединен с единичным входом второго кетлмутационного триг гера, нулевой выход которого соединен с еди-. ничным входом триггера памяти, а единичный выход соединен с нулевым входом первого коммутационного триггера, нулевой выход первого коммутационного триггера соединен с входом первой схемы И-НЕ, а ед1шичный выход соединен с нулевыми входами первого и третьего триггеров памяти, с нулевым входом второго коммутационного триггера и с входами первой и второй схем И-НЕ, выход первой схемы И-НЕ соединен с нулевыми входами первого коммутационного триггера и первого триггера памяти, с единичным входом второго триггера памяти и с входом третьей схемы И-НЕ, выход которой соединен с единичными входами йторого и третьего триггеров памяти и с нулевым входом второго коммутационного триггера, кулевой выход второго триггера памяти также соединен с нулевым входом второго коммутационного триггера, а единичный выход соединен с входом третьей схемы И-НЕ, нулевой выход третьего триггера памяти соединен с нулевым входом второго триггера памяти и с входами первой и второй схем И-НЕ, выход второй схемы И-НЕ соединен с единичным входом первого коммутационного триггера 3. Однако известное устройство выполнено на большом количестве схем И-НЕ и, следовательно, надежность его невысокая. Цель изобретения - повышение надежности устройства в работе. Для этого в делитель частоты импульсов на 10, содержащий триггеры памяти, коммутационые триггеры и элементы И-НЕ,введен дополительный элемент И-НЕ, выход которого оединен с единичным входом первого коммуаШбнногб триггера, при этомнулевой выход ретьего коммутационного триггера подклюен к первому входу дополнителыюго элеента И-НЕ, а единичный выход - к нулевым входам первого коммутацио1шого триггера, первого и третьего триггеров памяти, четвертому входу первого элемента И-НЕ, к третьему входу второго элемента И-НЕ и к нулевому входу четвертого триггера памяти, нулевой выход которого соядинён с нулевым входсзм третьего коммутационного триггера, единичный выход первого .коммуташюнного триггера подключен к единичным входам третьего коммутационного триггера и четвертого триггера памяти и ко второму входу дополнительного элемента И-НЕ, нулевой выход nepBoio коммутационного триггера - к единичному входу третьего коммутационного триггера, а выход второго элемента И-НЕ соединен с единичным входом третьего коммутационного триггера, причем единичный вход первого коммутационного триггера, нулевой вход второго коммутационного триггера, единичный вход третьего коммутационного триггера, пятый вход первого элемента И-НЕ и третий вход третьего элемента И-НЕ подключены к входной шине.

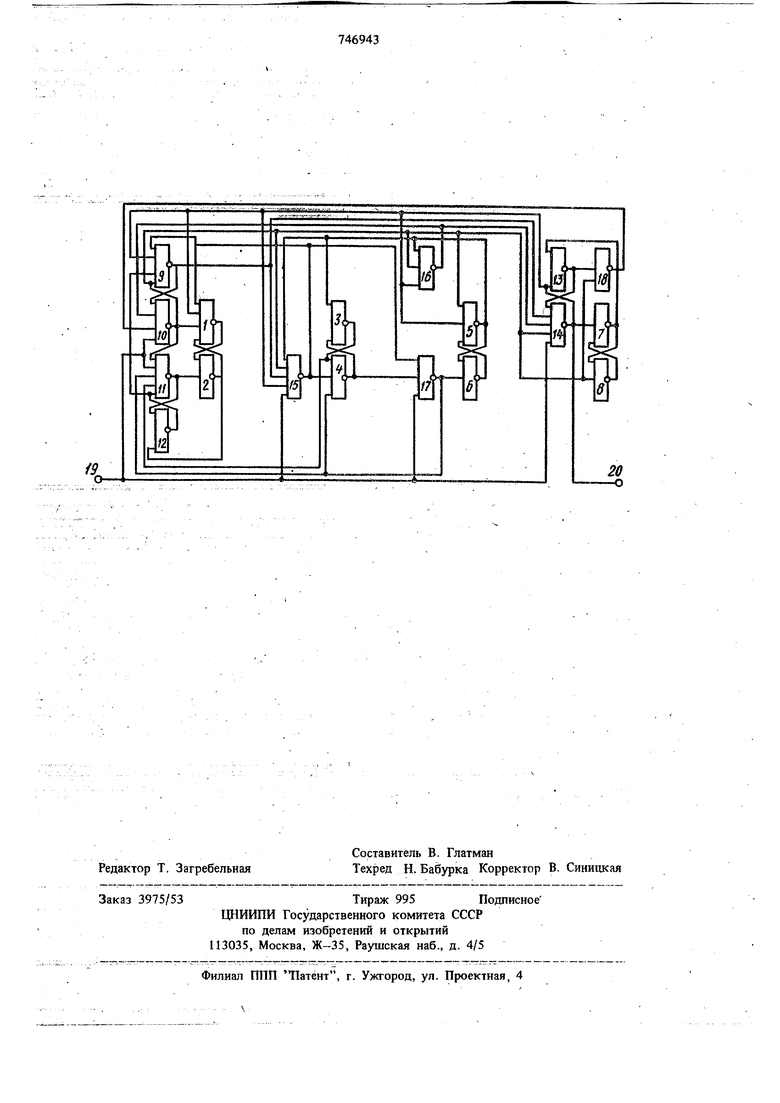

На чертеже представлена структурная электрическая схема делителя. частоты импульсов на 10.

Устройство содержит элементы И-НЕ 1-8, попарно образующие первый, второй, третий и четвертый триггеры памяти, элементы И-НЕ 9-14, попарно образующие первый, второй третий коммутационные триггеры, элементы И-НЕ 15-18, шину 19 входных импульсов, шину 20 выходных импульсов.

Устройство работает следующим образом. В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а входаой сигнал, поступаюидай на шину 19, отсутствует (равен логическому нулю). В этом случае на выходах элементов И-НЕ 1, 3, 5, 7, 10, И, 12, 14, 15, 17, 18будет сигнал, равный логической единице, на вЫхЬдах остальньтх элементов И-НЕ будет сигнал, р авный логическому нулю. С приходом первого входного импульса открывается элемент И-НЕ И, и на его выходе появляется сигнал, равный логическому нулю, который устанавливает первый триггер памяти в единичное состояние. Наличие связи с выхода элемента И-НЕ 11 на вход элемента И-НЕ 12 препятствует появлению на выходе элемента И-НЕ 12 сигнала, равного логическому нулю в момент действия входного импульса. После окончания действия входного импульеа на выходе элемента И-НЕ 12 появляется сигнал, равный логическому нулю, а на выходе элемента И-НЕ 9 - сигнал, равный логической единице. Поэтому с приходом второго входного импульса

логический нуль появляется на выходе элемента И-НЕ 15, который устанавливает второй триггер памяти в единичное состояние, а первый триггер памяти - в нулевое состояние. Наличие связей с выхода элемента И-НЕ 15 на

входы элементов И-НЕ 9 и 17 препятствует появлению на выходах этих элементов сигнала, равного логическому нулю, в момент действия входного импульса. После окончания действия второго входного импульса на выходе элемента

И-НЕ 9 появляется сигнал, равный логическому нулю, поэтому с приходом третьего входного импульса логический нуль появляется на выходе элемента И-НЕ 17, устанавливая третий триггер памяти в единичное состояние. Сигнал,

равный логическому нулю, с нулевого выхода третьего триггера памяти (элемент И-НЕ 5) устанавливает в нулевое состояние второй триггер памяти. Наличие связей с выхода элемента И-НЕ 17 на входы элементов И-НЕ 4, 11

препятствует появлению на выходах этих элементов логического нуля в момент действия входного сигнала. С приходом четвертого входного импульса открывается элемент И-НЕ 11, устанавливая первый триггер памяти в ециничное состояние. После окончания действия входного импульса подготовленным к срабатыванию оказывается элемент И-НЕ 10, поскольку на выходах элементов И-НЕ 9, 16 логическая единица. Следовательно, с приходом

пятого входного импульса на выходе элемента И-НЕ 10 появляется сигнал, равный логическому нулю, который устанавливает Первый и третий триггеры памяти в нулевое состояние, а четвертый триггер памяти - в единичное состояние. Аналогично с приходом шестого входного импульса первый триггер памяти устанавливается в единичное состояние, с приходом седьмого входного импульса второй триггер памяти устанавливается в единичное состояние,

а первый триггер памяти - в нулевое состояние. С приходом восьмого входного импульса третий триггер памяти устанавливается в единичное состояние, а второй триггер памяти - в нулевое состояние. С приходом девятого входного импульса первый триггер памяти снова устанавливается в единичное состояние. После окончания действия входного импульса подготовленным к срабатыванию оказывается элемент И-НЕ 14, поэтому с приходом десятого импульса на выходе элемента И-НЕ 14 появляется сигнал, равный логическому нулю, который поступает на шину 20 возвращает схему в исходное состояние, устанавливая триггеры памяти в нулевое состояние.

Таким образом, в делителе осуществляется 1 следутошая последовательность смены Чостояний.

На десять входных импульсов схема выдает один выходной импульс, т.е. осуществляется деление на 0.

Формула изобретения

Делитель частоты импульсов на 10, содержаишй триггеры памяти, коммутационные триггеры и элементы И-НЕ, причем нулевой выход первого коммутационного триггера соединен с первым входом первого элемента И-НЕ, а одиночный выход - с нулевыми входами первого триггера памяти, второго и третьего коммутационных триггеров и с первым входом 30

второго элемента И-НЕ, единичный выход второго коммутационного триггера подключен к нулевому входу первого коммутационного триггера, а нулевой выход - к единичному входу первого триггера памяти, единичный

выход которого соединен с единичным входом второго коммутационного триггера, нулевой выход второго триггера памяти подключен к нулевому входу второго коммутационного триггера, а единичный выход - к первому

входу третьего элемента И-НЕ, нулевой выход третьего триггера памяти соединен со вторым входом второго элемента И-НЕ, с нулевым входом второго триггера памяти и с третьим входом первого элемента И-НЕ, выход которого подключен к нулевым входам первого коммутационного триггера и триггера памяти, к единичному входу второго триггера памяти и к вторрму входу третьего элемента И-НЕ, выход второго элемента И-НЕ соединен с единйчнь1М входом первого коммута5 1ШОННОГО триггера, а выход третьего элемента И-НЕ - с нулевым входом второго коммутационного триггера и с единичными входами второго и третьего триггеров памяти, отличающийся тем, что, с целью повыше0 ния надежности устройства в работе, в него введен дополнительный элемент И-НЕ, выход которого соединен с единичным входом первого коммутационного триггера, при этом нулевой выход третьего коммутационного

5 триггера подключен к первому входу дополнительного элемента И-НЕ, а единМный г

выход - к нулевым входам первого коммутационного триггера,первого и третьего триггеров памяти, к четвертому входу первого 0 элемента И-НЕ, к третьему входу второго элемента И-НЕ и к нулевому входу четвертого трштера памяти, нулевой выход которого соединен с нулевым входом третьего коммутационного триггера, един1тный выход первого коммутационного триггера подключен к единичным входам третьего коммутационного триггера и четвертого триггера памяти и к второму входу дополнительного элемента И-НЕ, нулевой выход первого коммутационго коммутационного триггера, а выход второго элемента И-НЕ соединен с единичным входом третьего коммутационного триггера, причем единичный вход первого коммутационного трштера, нулевой вход второго коммутационного триггера, единичный вход третьего коммутационного триггера, пятый вход первого элемента И-НЕ и третий вход третьего элемента И-НЕ подключень к входной шине.

Источники информации, принятые во внимание при экспертиве

1.Авторское свидетельство СССР № 382241, кл. Н 03 К 23/02, 1970.

2.Авторское свидетельство СССР № 506131, кл. Н 03 К 23/02, 1974.

3.Авторское свидетельство СССР № 558405, кл. Н 03.К 23/02, 1976 (прототип). ного триггера - к единичному входу третье

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на девять | 1977 |

|

SU687603A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU873417A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты | 1979 |

|

SU845291A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

Авторы

Даты

1980-07-23—Публикация

1978-01-18—Подача