Изобретение огносигся к области KOHT роля цифровых электронных устройств и Может быть использовано для тестовотЧэ испытания цифровых устройств с малыми объемами тестов. Известны устройства для контроля микроэлектронных схем, содержащие запоминающие блоки, блоки записи, регист ры тестов и блоки сравнения, посредство которых в испытуемую схему вводятся контрольные сигналы и осуществляется анализ ее реакций l - Недостаток известных устройств со- - стоит в сложности их конструкции. Наиболее бл данному посущности технического решения является устройство для контооля электрических блоков, содержащее генератор импульсов соединенный выходом со входом счетчика узел индикации, регистр отт ликов, подключенный выходами к соответствующим входам первого коммутатора, группа вьтхрдов которого соединена с первой группо входов схемы сравнения, соединенной втр рой группой {входов с группой выходов контролируемого блока, регистр входных комбинаций.тестовых сигналов, соединенный выходами с соответствующими входами второго коммутатора, группа выходов которого п6да:лючен(а к группе входов контролируемого блока, адресные входы первогЬ и второго коммутаторов соединены с соответствующими выходами счетчика 2 . Недостатком этого устройства является сложность конструкции. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что в устройство введены элементИЛИ и переключатель режимов, причем управляющий вход генератора импульсов соединен с выходом элемента ИЛИ, первый вход которого соединен через переключатель режимов с выходом узла индикации, а второй вход - с управляющим выходом счетчика и входом узла индикации, информационные входы которого соедине370

соответстйующими выходами схемы сра&нения, а адресные входы - с соответствующими выходами счетчика

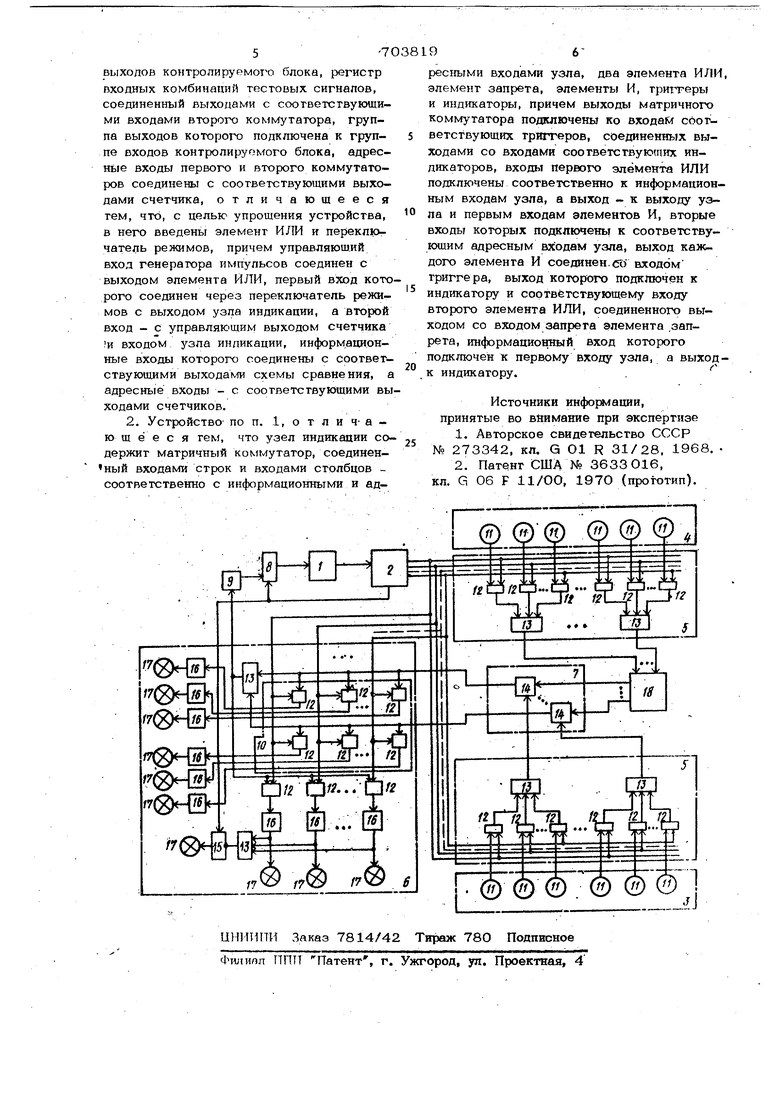

КрЬме того, узел индикации содержит матричный коммутатор, соединенный входам строк и входами столбцов соответственно с информационными и адресными входами узла, два элемента ИЛИ, элемент запрета, элемент И, триггеры и индикаторы, причем выходы матричного коммутатора подключены ко входам соответствующих триггеров, соединенных выходами со входами соответствующих индикаторов, входы первого элемента ИЛИ подключены соответственно к информационным входам узла, а выход - к выходу уз-па и пербым Ъхбдймэлементов И, вторые входы которых подключены к соот етствующим адресным входам узла, вьрсод каждого элемента И соединен .со входом триггера, выход которого подключен к индикатору и соответствующему входу второго элемента ИЛИ, соединеннохчэ выходом со входом запрета элемента запрета, информационный вход которого подключен к первому входу узпа, а выход - к индикатору. Схема устройства представглена на чертеже.

Устройство содержит генератор 1 импульсов, счетчик 2, регистр 3 откликов, регистр 4 входных комбинаций тестовых сигналов, коммутаторы 5, узел 6 индикации, схему 7 сравнения, элемент ИЛИ 8, переключатель 9 режимов, матричный коммутатор 10, ячейки 11 фотоприемной матрицы, элементы И 12,.элементы ИЛИ 13, элементы 14 антисовпадений, элемент 15 запрета, триггеры 16, индикаторы 17 и контролируемый блок 18.

Устройство работает следующим образом..

Устройство, считывающее информацию с перфокарты, на которой закодированы входные:комбинации теста и соответствуюшие им коды реакций контролируемого блока 18, работает в двух режимах: отбраковка и испытание. В.первом ре-жиме цепь н& элемент КЛИ 8, проходящая через переключатель 9, замкнута, во втором -разомкнута. При использовании фотосчятывающего устройства возбуждают{Ся ячейки 11, которые образуют рёгистры 3 и 4.

Импульсами генератора 1 счетчик 2 переключается, выдавая на коммутаторы 5 адрес, в результате чего на контролируемый блок 18 и схему 7 сравнения

9:4

синхронно подаются соответственно контрольные сигналы теста и оишдаемо реакции блока. Выходные сигналы блока 1 8 поступают на элементы 14 схемы 7 сравнения, на которых присутствуют эталонные сигналы. Если хотя бы один элемент 14 антисовпадений возбудится, что означает неправильность реакции контролируемого блока 18, на соответствующем выходе матричного коммутатора 10 появится сигнал, который переключит подключенный к этому входу триггер 16 и возбудит индикатор 17. При этом возбудивщийся индикатор 17 точно отобразит номер тестовой комбинации и номер выхода блока 18, на котором наблюдается неверна1Я-реакция.

.Если на всех тестовых комбинациях реакдаи блока 1 8 совпали с эталонными, то на последнем шаге счетчика 2 блокируется генератор 1(сигналом через элемент ИЛИ 8) и выключается индикатор 1 7, подключенный через элемент 15 запрета.

Различие в режимах работы состоит в том, что в режиме отбраковка происходит блокировка генератора 1 при первом отклонении (возбуждается один из элементов 14) по сигналу с элемента ИЛИ 13 узла 6 индикации, собирающего все выходные сигналы схемы 7. При этом процесс контроля прерывается.

В режиме испытание режим контроля не прерывается, и после завершения проверки возбужденные индикаторы указывают номера тестовых комбинаций, на которых ошибался контролируемый блок 18, и номера выходов, где наблюдались ошибки по каждой тестовой комбинации.

Таким образом, простая конструкция устройства позволяет оперативно контролировать ци4ровые блоки с небольшими объемами проверок и анализировать возможные неисправности блока.

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее генератор импульсов, соединенный выходом со входом счетчика, узел индикации, регистр.откликов, подключенный выходами к соответствующим входам первого коммутатора, группа выходов которого соединена с первс й группой входов схемы сравнения, 5рдиМненной второй группой входов с труппой

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля параллельных микропроцессорных интерфейсов | 1982 |

|

SU1040489A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

Авторы

Даты

1979-12-15—Публикация

1977-03-02—Подача