со

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дистанционного управления топливораздаточными колонками | 1982 |

|

SU1067472A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков постоянной памяти. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство дополнительно введены формирователь сигнала Строб, блок инверторов, блок триггеров, элемент ИЛИ и соответствующие связи. Устройство также содержит блок задания адреса, первый счетчик, второй счетчик, первый коммутатор, блок управления, третий счетчик, второй коммутатор, блок логического анализа.4 ил.

Ч

с

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков постоянной памяти.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для контроля блоков постоянной памяти, содержащее блок логического анализа, входы которого подключены соответственно к первому выходу блока управления и первому входу устройства, а выход - ко входу блока управления, второй выход блока управления подключен ко второму выходу устройства, первый счетчик, входы которого подключены к соответствующим выходам блока задания адреса, и блок индикации, второй счетчик, первый вход которого подключен к выходу переноса первого счетчика, а другие входы второго счетчика подключены к соответствующим выходам блока задания адреса, первый коммутатор, входы которого подключены к соответствующим выходам счетчиков, а выходы - ко входам блока индикации и выходам устройства, второй коммутатор, выход которого подключен к первому входу первого счетчика, третий счетчик, первый выход которого подключен к первому входу второго коммутатора, а второй выход - к управляющему входу первого коммутатора, один вход - к выходу блока управления и ко второму входу второго коммутатора, другие входы третьего счетчика и вторые входы первого и второго счетчиков подключены к соответствующим выходам блока управления.

Недостатком этого устройства является ограниченная область применения, т.к. оно не позволяет контролировать увеличение времени выборки информации из блоков постоянной памяти при порядке адресов, отличном от естественного порядка их смены.

Цель изобретения - расширение области применения устройства.

vi ч ел ел

N) Ю

Поставленная цель достигается тем, что в устройство, содержащее блок логического анализа, вход синхронизации которого подключен к первому выходу блока управления, входы блока логического анализа являются информационными входами устройства, а выход блока логического анализа подключен к первому входу блока управления, второй выход которого является вторым выходом устройства, первый счетчик, входы которого подключены к соответствующим выходам блока задания адреса, блок индикации, второй счетчик, первый вход которого подключен к выходу переноса первого счетчика, а другие входы второго счетчика подключены к соответствующим выходам блока задания адреса, первый коммутатор, входы которого подключены к соответствующим выходам счетчиков, а выходы первого коммутатора соединены с входами блока индикации и являются первым выходом устройства, второй коммутатор, выход которого подключен к первому входу первого счетчика, третий счетчик, выход которого подключен к первому входу второго коммутатора и управляющему входу первого коммутатора, один вход третьего счетчика подключен к третьему выходу блока управления и ко второму входу второго коммутатора, другие входы третьего счетчика и вторые входы первого и второго счетчиков подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью расширения области применения ус- тройстаа за счет контроля времени выборки заданного значения, в него введены формирователь сигнала Строб, блок инверторов, блок триггеров и элемент ИЛИ, причем вход формирователя сигнала Строб подключен ко второму выходу блокаг управления, а выход соединен с информационными входами блока триггеров, входы синхронизации которых подключены к соответствующим выходам блока инверторов, входы которого соединены с информационными входами устройства, третьими выходами которого являются прямые выходы блока триггеров, инверсные выходы которого соединены со входами элемента ИЛИ, выход которого подключен ко второму входу блока управления.

Предложенное техническое решение соответствует критерию существенные отличи, т.к. свойство расширения области применений устройства, обусловленное введением а форму изобретения отличительных признаков, не Достигалось ранее известными техническими решениями.

Положительный эффект при осуществлении изобретения достигается тем, что при

проверке блоков постоянной памяти путем попарного считывания адресов, обеспечивающего все возможные сочетания следова- . ния адресов в реальных условиях работы и на

5 максимальной рабочей частоте, Контролируется не только отсутствие искажения информации, но и превышение времени выборки заданного значения.

При этом, обеспечивается получение

оперативной информации о виде неисправности (искажение информации или брак времени выборки) и возможность установки и регулировки зоны контроля времени выборки.

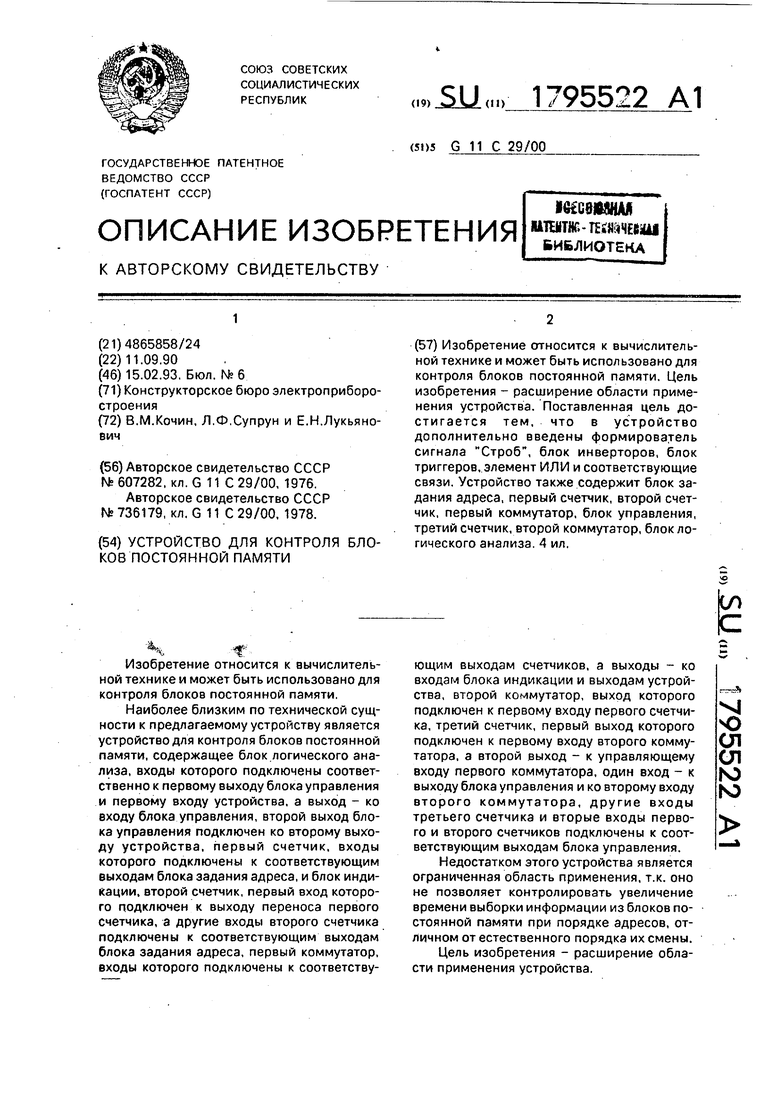

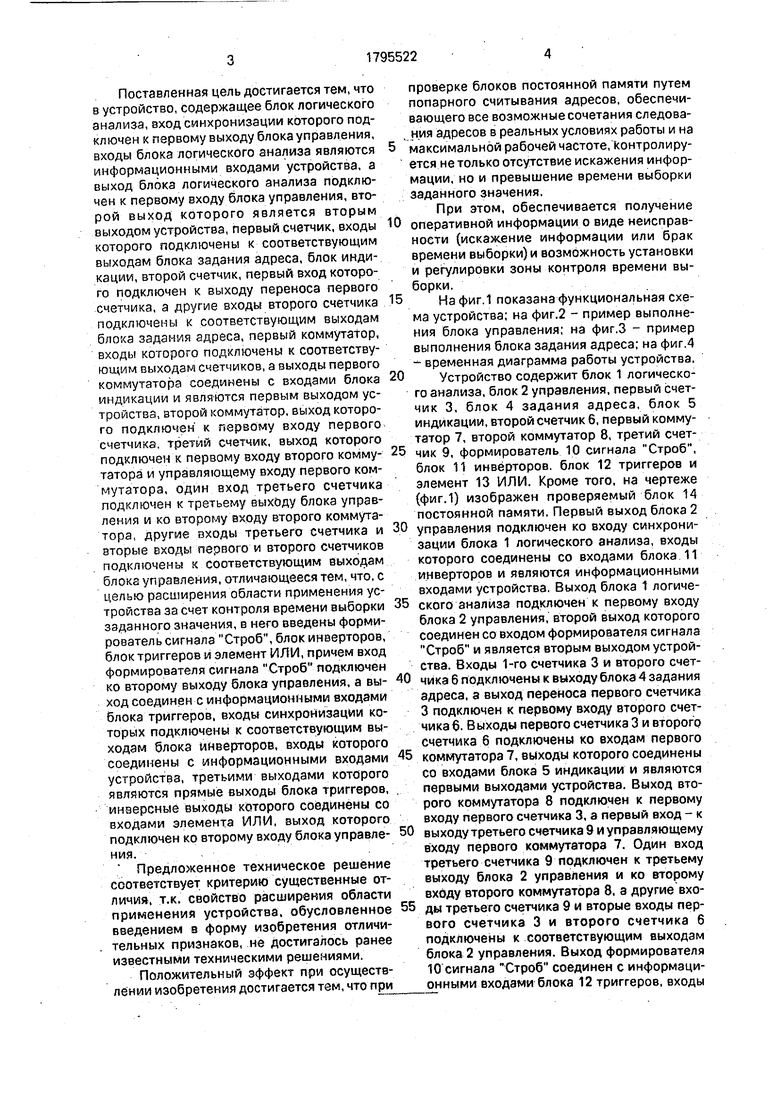

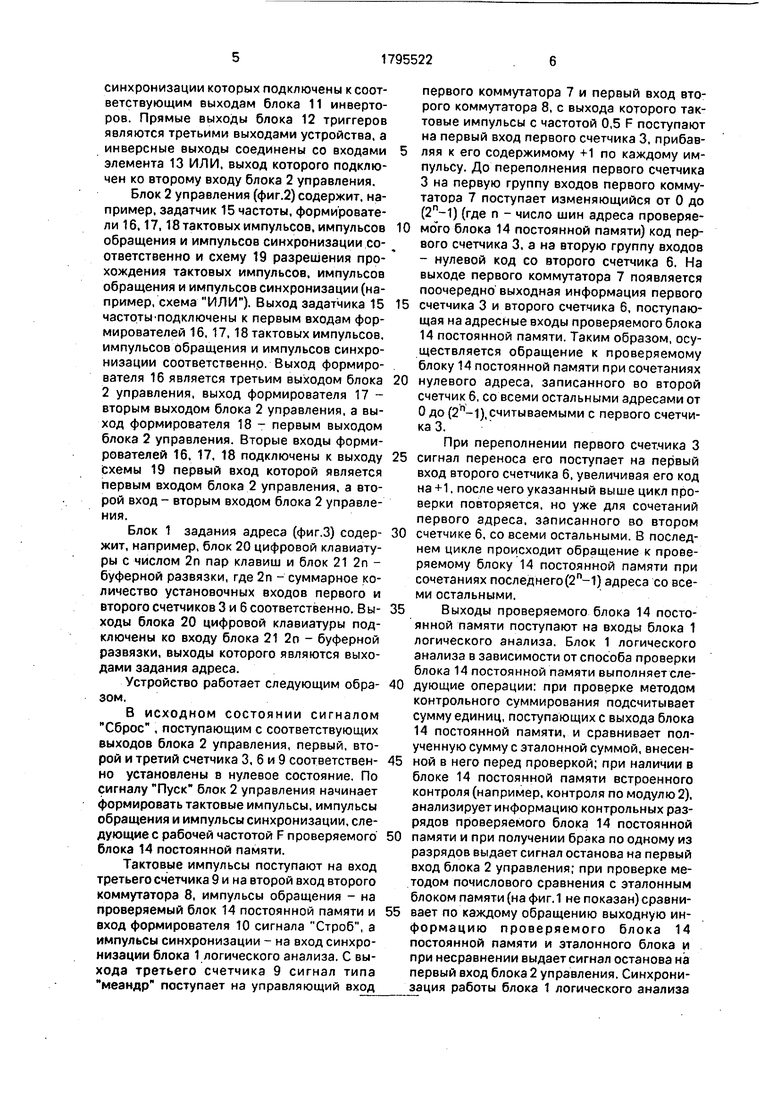

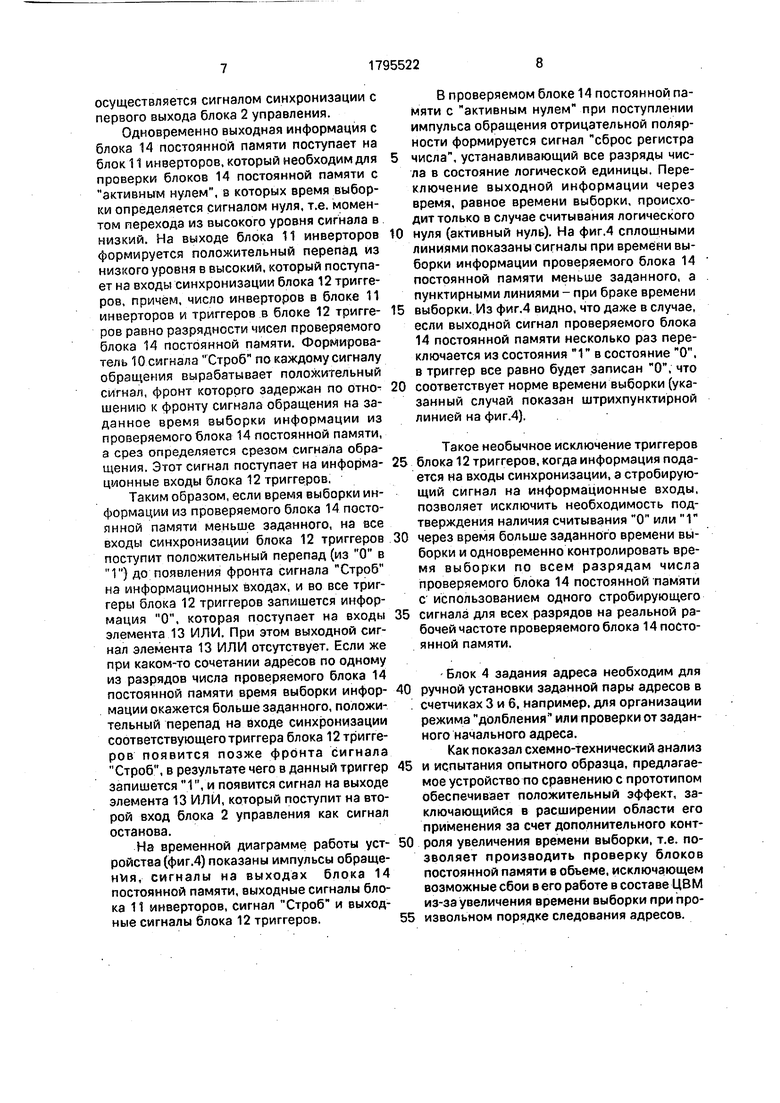

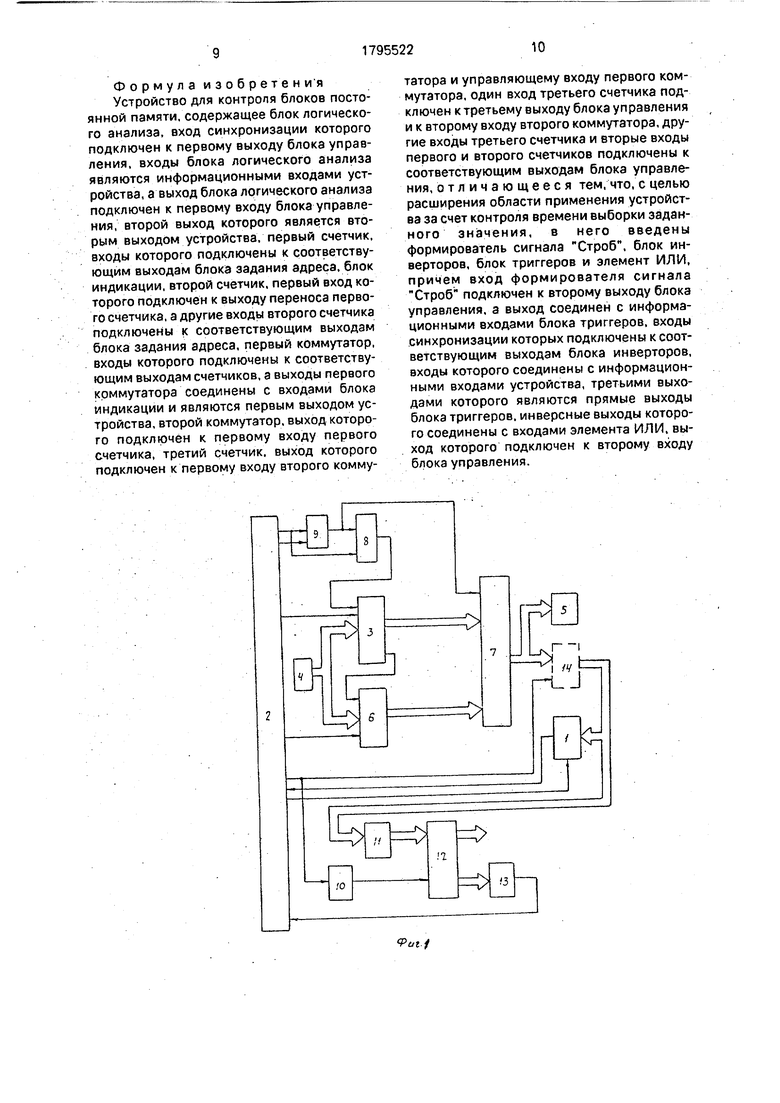

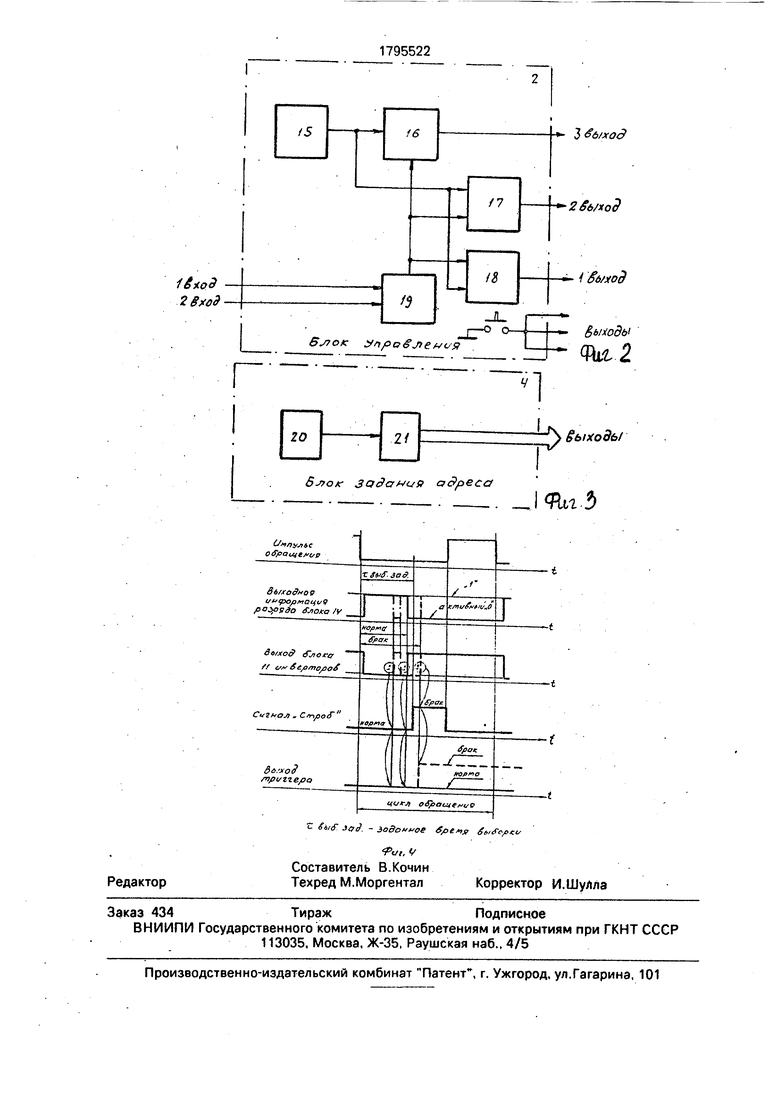

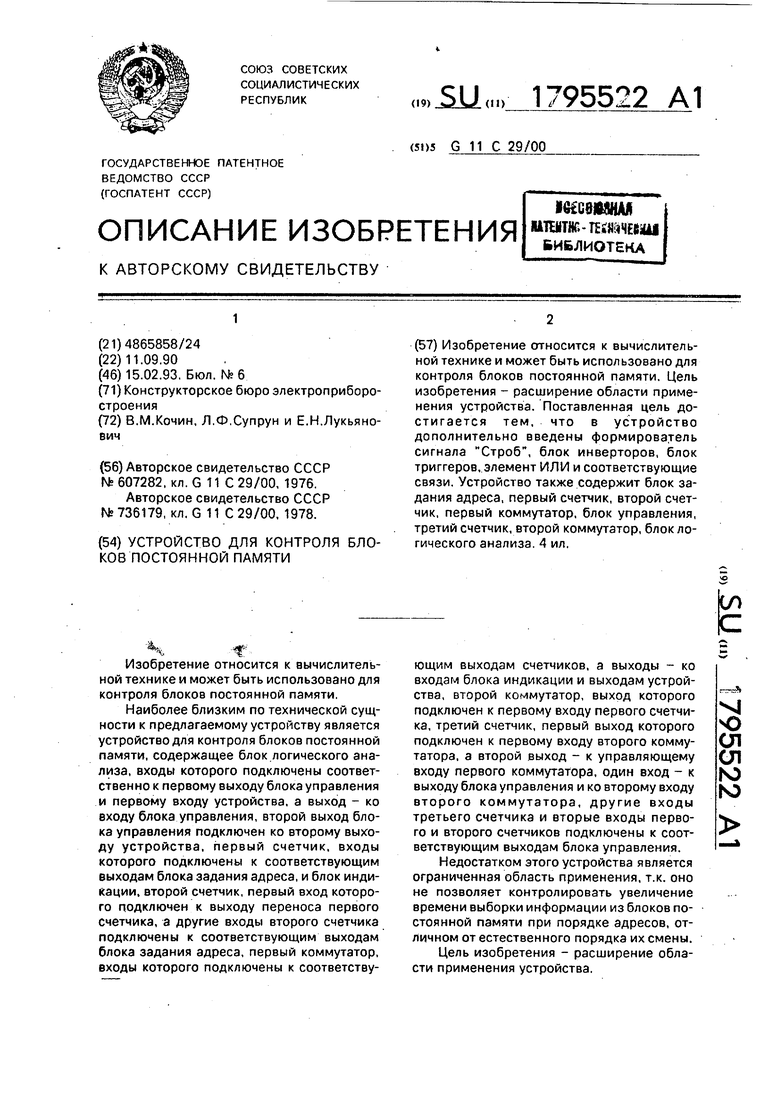

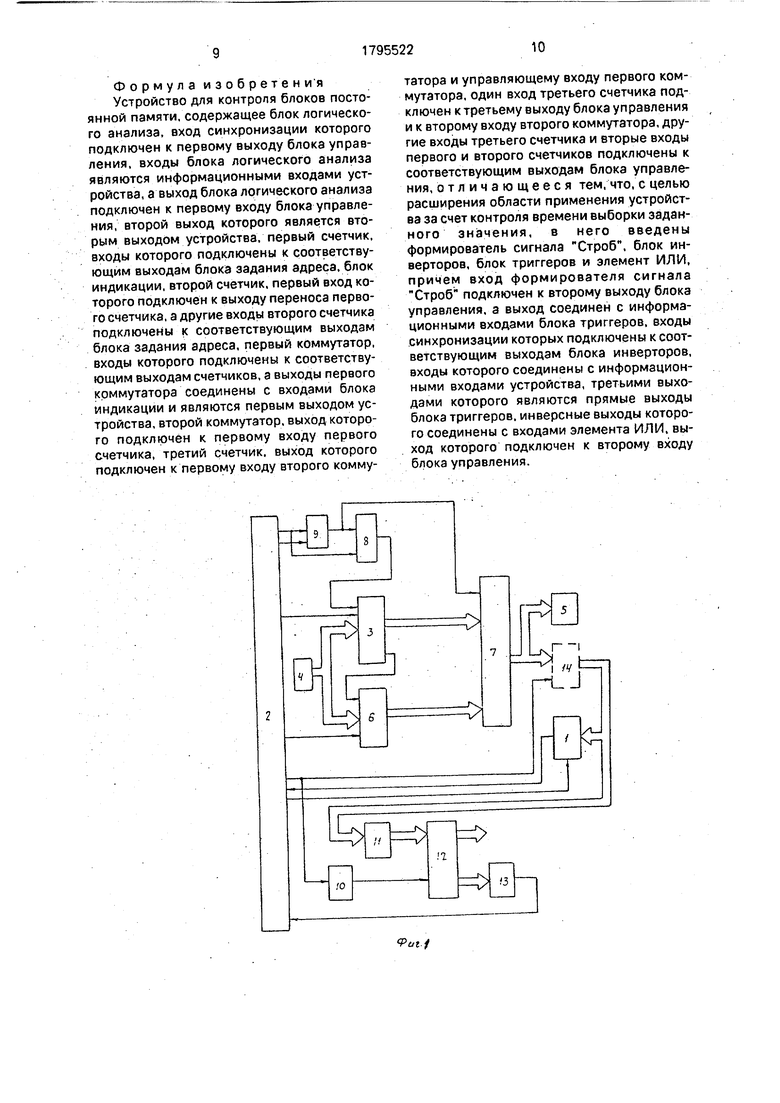

5 На фиг.1 показана функциональная схема устройства; на фиг.2 - пример выполнения блока управления; на фиг.З - пример выполнения блока задания адреса; на фиг.4 - временная диаграмма работы устройства.

0 Устройство содержит блок 1 логического анализа, блок 2 управления, первый счетчик 3, блок 4 задания адреса, блок 5 индикации, второй счетчик 6, первый коммутатор 7, второй коммутатор 8, третий счет5 чик 9, формирователь 10 сигнала Строб, блок 11 инверторов, блок 12 триггеров и элемент 13 ИЛИ. Кроме того, на чертеже (фиг.1) изображен проверяемый блок 14 постоянной памяти. Первый выход блока 2

.0 управления подключен ко входу синхронизации блока 1 логического анализа, входы которого соединены со входами блока 11 инверторов и являются информационными входами устройства. Выход блока 1 логиче5 ского анализа подключен к первому входу блока 2 управления, второй выход которого соединен со входом формирователя сигнала Строб и является вторым выходом устройства. Входы 1-го счетчика 3 и второго счет0 чика 6 подключены к выходу блока 4 задания адреса, а выход переноса первого счетчика 3 подключен к первому входу второго счетчика §. Выходы первого счетчика 3 и второго счетчика б подключены ко входам первого

5 коммутатора 7, выходы которого соединены со входами блока 5 индикации и являются первыми выходами устройства. Выход второго коммутатора 8 подключен к первому входу первого счетчика 3, а первый вход - к

0 выходу третьего счетчика 9 и управляющему входу первого коммутатора 7. Один вход третьего счетчика 9 подключен к третьему выходу блока 2 управления и ко второму входу второго коммутатора 8, а другие вхо5 ды третьего счетчика 9 и вторые входы первого счетчика 3 и второго счетчика 6 подключены к соответствующим выходам блока 2 управления. Выход формирователя 10 сигнала Строб соединен с информзци онными входами блока 12 триггеров, входы

синхронизации которых подключены к соответствующим выходам блока 11 инверторов. Прямые выходы блока 12 триггеров являются третьими выходами устройства, а инверсные выходы соединены со входами элемента 13 ИЛИ, выход которого подключен ко второму входу блока 2 управления.

Блок 2 управления (фиг.2) содержит, например, задатчик 15 частоты, формирователи 16,17,18 тактовых импульсов, импульсов обращения и импульсов синхронизации соответственно и схему 19 разрешения прохождения тактовых импульсов, импульсов обращения и импульсов синхронизации (например, схема ИЛИ). Выход задатчика 15 частоты подключены к первым входам формирователей 16, 17,18 тактовых импульсов, импульсов обращения и импульсов синхронизации соответственно. Выход формирователя 16 является третьим выходом блока 2 управления, выход формирователя 17 - вторым выходом блока 2 управления, а выход формирователя 18 - первым выходом блока 2 управления. Вторые входы формирователей 16, 17, 18 подключены к выходу Схемы 19 первый вход которой является первым входом блока 2 управления, а второй вход - вторым входом блока 2 управления.

Блок 1 задания адреса (фиг.З) содержит, например, блок 20 цифровой клавиатуры с числом 2п пар клавиш и блок 21 2п - буферной развязки, где 2п - суммарное количество установочных входов первого и второго счетчиков 3 и 6 соответственно. Выходы блока 20 цифровой клавиатуры подключены ко входу блока 21 2о - буферной развязки, выходы которого являются выходами задания адреса.

Устройство работает следующим образом.

В исходном состоянии сигналом Сброс, поступающим с соответствующих выходов блока 2 управления, первый, второй и третий счетчика 3, 6 и 9 соответственно установлены в нулевое состояние. По сигналу Пуск блок 2 управления начинает формировать тактовые импульсы, импульсы обращения и импульсы синхронизации, следующие с рабочей частотой F проверяемого блока 14 постоянной памяти.

Тактовые импульсы поступают на вход третьего счетчика 9 и на второй вход второго коммутатора 8, импульсы обращения - на проверяемый блок 14 постоянной памяти и вход формирователя 10 сигнала Строб, а импульсы синхронизации - на вход синхронизации блока 1 логического анализа. С выхода третьего счетчика 9 сигнал типа меандр поступает на управляющий вход

первого коммутатора 7 и первый вход второго коммутатора 8, с выхода которого тактовые импульсы с частотой 0,5 F поступают на первый вход первого счетчика 3, прибав- 5 ляя к его содержимому +1 по каждому импульсу. До переполнения первого счетчика 3 на первую группу входов первого коммутатора 7 поступает изменяющийся от 0 до (2п-1) (где п - число шин адреса проверяе0 мого блока 14 постоянной памяти) код первого счетчика 3, а на вторую группу входов - нулевой код со второго счетчика 6. На выходе первого коммутатора 7 появляется поочередно выходная информация первого

5 счетчика 3 и второго счетчика 6, поступающая на адресные входы проверяемого блока 14 постоянной памяти. Таким образом, осуществляется обращение к проверяемому блоку 14 постоянной памяти при сочетаниях

0 нулевого адреса, записанного во второй счетчик 6, со всеми остальными адресами от О до (2п-1), считываемыми с первого счетчика 3.

При переполнении первого счетчика 3

5 сигнал переноса его поступает на первый вход второго счетчика 6, увеличивая его код на +1, после чего указанный выше цикл проверки повторяется, но уже для сочетаний первого адреса, записанного во втором

0 счетчике 6, со всеми остальными. В последнем цикле происходит обращение к проверяемому блоку 14 постоянной памяти при сочетаниях последнего() адреса со всеми остальными.

5 Выходы проверяемого блока 14 постоянной памяти поступают на входы блока 1 логического анализа. Блок 1 логического анализа в зависимости от способа проверки блока 14 постоянной памяти выполняетсле0 дующие операции: при проверке методом контрольного суммирования подсчитывает сумму единиц, поступающих с выхода блока 14 постоянной памяти, и сравнивает полученную сумму с эталонной суммой, внесен5 ной в него перед проверкой; при наличии в блоке 14 постоянной памяти встроенного контроля (например, контроля по модулю 2), анализирует информацию контрольных разрядов проверяемого блока 14 постоянной

0 памяти и при получении брака по одному из разрядов выдает сигнал останова на первый вход блока 2 управления; при проверке методом почислового сравнения с эталонным блоком памяти (на фиг. 1 не показан) сравни5 вает по каждому обращению выходную информацию проверяемого блока 14 постоянной памяти и эталонного блока и при несравнении выдает сигнал останова на первый вход блока 2 управления. Синхронизация работы блока 1 логического анализа

осуществляется сигналом синхронизации с первого выхода блока 2 управления.

Одновременно выходная информация с блока 14 постоянной памяти поступает на блок 11 инверторов, который необходим для проверки блоков 14 постоянной памяти с активным нулем, в которых время выборки определяется сигналом нуля, т.е. моментом перехода из высокого уровня сигнала в низкий. На выходе блока 11 инверторов формируется положительный перепад из низкого уровня в высокий, который поступает на входы синхронизации блока 12 триггеров, причём, число инверторов в блоке 11 инверторов и триггеров в блоке 12 триггеров равно разрядности чисел проверяемого блока 14 постоянной памяти. Формирователь 10 сигнала Строб по каждому сигналу обращения вырабатывает положительный сигнал, фронт которого задержан по отношению к фронту сигнала обращения на заданное время выборки информации из проверяемого блока 14 постоянной памяти, а срез определяется срезом сигнала обращения. Этот сигнал поступает на информационные входы блока 12 триггеров,

Таким образом, если время выборки информации из проверяемого блока 14 постоянной памяти меньше заданного, на все входы синхронизации блока 12 триггеров поступит положительный перепад (из О в 1) до появления фронта сигнала Строб на информационных входах, и во все триггеры блока 12 триггеров запишется информация О, которая поступает на входы элемента 13 ИЛИ. При этом выходной сигнал элемента 13 ИЛИ отсутствует. Если же при каком-то сочетании адресов по одному из разрядов числа проверяемого блока 14 постоянной памяти время выборки информации окажется больше заданного, положительный перепад на входе синхронизации соответствующего триггера блока 12 триггеров появится позже фронта сигнала Строб, в результате чего в данный триггер запишется 1, и появится сигнал на выходе элемента 13 ИЛИ, который поступит на второй вход блока 2 управления как сигнал останова.

На временной диаграмме работы устройства (фиг.4) показаны импульсы обращена я, сигналы на выходах блока 14 постоянной памяти, выходные сигналы блока 11 инверторов, сигнал Строб и выходные сигналы блока 12 триггеров.

В проверяемом блоке 14 постоянной памяти с активным нулем при поступлении импульса обращения отрицательной полярности формируется сигнал сброс регистра

числа, устанавливающий все разряды числа в состояние логической единицы. Переключение выходной информации через время, равное времени выборки, происходит только в случае считывания логического

нуля (активный нуль). На фиг.4 сплошными линиями показаны сигналы при времени выборки информации проверяемого блока 14 постоянной памяти меньше заданного, а пунктирными линиями - при браке времени

выборки. Из фиг.4 видно, что даже в случае, если выходной сигнал проверяемого блока 14 постоянной памяти несколько раз переключается из состояния 1 в состояние О. в триггер все равно будет записан О, что

соответствует норме времени выборки (указанный случай показан штрихпунктирной линией на фиг.4).

Такое необычное исключение триггеров блока 12 триггеров, когда информация подается на входы синхронизации, а стробирую- щий сигнал на информационные входы, позволяет исключить необходимость подтверждения наличия считывания О или 1 через время больше заданного времени выборки и одновременно контролировать время выборки по всем разрядам числа проверяемого блока 14 постоянной памяти с использованием одного стробирующего сигнала для всех разрядов на реальной рабочей частоте проверяемого блока 14 постоянной памяти.

- Блок 4 задания адреса необходим для

ручной установки заданной пары адресов в счетчиках 3 и б, например, для организации режима долбления или проверки от заданного начального адреса.

Как показал схемно-технический анализ

и испытания опытного образца, предлагаемое устройство по сравнению с прототипом обеспечивает положительный эффект, заключающийся в расширении области его применения за счет дополнительного контроля увеличения времени выборки, т.е. позволяет производить проверку блоков постоянной памяти в объеме, исключающем возможные сбои в его работе в составе ЦВМ из-за увеличения времени выборки при произвольном порядке следования адресов.

Формула изобретений Устройство для контроля блоков постоянной памяти, содержащее блок логического анализа, вход синхронизации которого подключен к первому выходу блока управления, входы блока логического анализа являются информационными входами устройства, а выход блока логического анализа подключен к первому входу блока управления, второй выход которого является вторым выходом устройства, первый счетчик, входы которого подключены к соответствующим выходам блока задания адреса, блок индикации, второй счетчик, первый вход которого подключен к выходу переноса первого счетчика, а другие входы второго счетчика подключены к соответствующим выходам блока задания адреса, первый коммутатор, входы которого подключены к соответствующим выходам счетчиков, а выходы первого коммутатора соединены с входами блока индикации и являются первым выходом устройства, второй коммутатор, выход которого подключён к первому входу первого счетчика, третий счетчик, выход которого подключен к первому входу второго коммутатора и управляющему входу первого коммутатора, один вход третьего счетчика подключен к третьему выходу блока управления и к второму входу второго коммутатора, другие входы третьего счетчика и вторые входы первого и второго счетчиков подключены к соответствующим выходам блока управления, отличающееся тем, что, с целью расширения области применения устройства за счет контроля времени выборки заданного значения, в него введены формирователь сигнала Строб, блок инверторов, блок триггеров и элемент ИЛИ, причем вход формирователя сигнала Строб подключен к второму выходу блока управления, а выход соединен с информационными входами блока триггеров, входы синхронизации которых подключены к соответствующим выходам блока инверторов, входы которого соединены с информационными входами устройства, третьими выходами которого являются прямые выходы блока триггеров, инверсные выходы которого соединены с входами элемента ИЛИ, выход которого подключен к второму входу блока управления.

5-70Л- Зсздания адреса

Ј ftif j#j. - эо8он ое

Редактор

fiti, V

Составитель В.Комин Техред М.Моргентал

Л

. .3

Корректор И.Шулла

| Устройство для контроля постоянных блоков памяти | 1976 |

|

SU607282A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля постоянных блоков памяти | 1978 |

|

SU736179A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-02-15—Публикация

1990-09-11—Подача