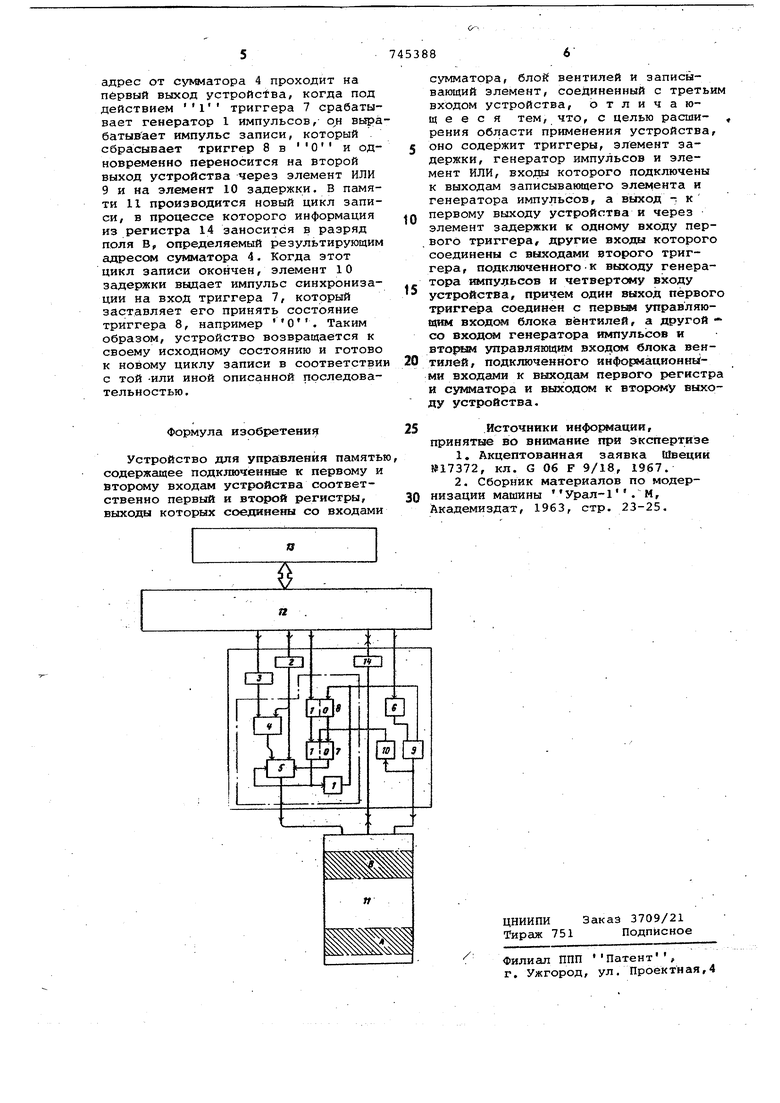

Изобретение относится к обласзти автоматики и вычислительной техники и предназначено для использования, например, в елекоммутационных системах, управляемых процессором-, где необходимо осуществлять перемещение данных из одного участка (поля) памяти в другой без нарушения функцио нирования системы в реальном масшта бе времени. Известно устройство для управления памятью 1, где при оперировании с новыми данными, сопровождаемом перемещением в памяти ранее записан ных данных, необходимо переходить на специальную программу двойной записи, что создает дополнительную нагрузку процессору и сужает область его применения. Наиболее близким к изобретению техническим решением является устройство для управления памятью 2, содержащее подключенные к первому и второму входам устройства соот ветственно первый и второй регистры выходы которых соединены со входами сумматора, блок вентилей и записывающий элемент, соединенный с третьи входом устройства. Оно не обладает .расширенной областью применения из-за йеобходимости осуществлять прерывание выполнения основной программы. . Цель изобретения - расширение области применения устройства. Для этого оно содержит триггеры, элемент задержки, генератор импульсов и элемент ИЛИ, входы которого подключены к выходам записывающего элемента и генератора импульсов, а выход ,- к первому выходу устройства и через элемент задержки к одному входу первого триггера, другие входы которого соединены с выходами второго триггера, подключенного к выходу генератора импульсов и четвертому входу устройства, причем один выход первого триггера соединен с первым управляющим входом блока вентилей, а другой - со входом геИератора импульсов и вторым управляющим входом блока вентилей, подключенного информационными входами к выходам первого регистра и сумматора и выходом к второму выходу устройства. На Ч1вртеже показана функциональная схема устройства. Она содержит генератор 1 импульсов, первый 2 и второй 3 .(адресный дополнительный) регистры, сумматор 4, блок 5 вентилей, записывающий элемент б, первый 7 и второй 8 триг геры, элемент ИЛИ 9, элемент 10 задержки, управляемую память 11 дан нЬк, процессор 12, телекоммутатор 13, информационный регистр 14. Аи В - соответственно первое и второе поля памяти данных. Устройство работает следующим образом. Переключательные элементы S теле коммутаторе 13 сканируются в соответствии с программой управления (хранящейся в соответствующем устройстве запоминания программы), при чем данные, касающиеся этих элементов, сохраняются в присвоенных информационных разрядах в памяти 11 данньзх.. Изменения в телекоммутаторе 13 или изменение вида работы систем требуют перемещения данных, в памяти данных, например, из первого поля А в новый разряд второго поля В. Это перемещение выполняется с помощью программы с низким приоритетом, постоянно прерываясь програм мами с высокими прйоритетшли. Совокупность вновь выданныхэлементов и дополнительный ащресный регистр 3 дают возможность записывать одни и те же данные как в первоначальный, так и в новый разряды, если программа выдает ксманду, обращенную к перемещаемому разряду данных. Для упрощения чертежа опущены элементы и связи между ними, относящиеся к считыванию команд програм мы процессором 12, из устройства за поминания программы. Устройство управления памятью по лучает адресную информацию от процессора 12 по первому входу в регистр 2, данные передаются в информационный регистр 14, а команда записи поступает с третьего входа на запйсывайщий элемент б. Кроме того устройство получает указание по четвертому входу всякий раз, когда -команда записи обращается к адресно позиции, связанной с разрядом запом нающего устройства, например в поле А, который находится в состоянии перемещения. Это означает, что дан йаё7°занесенные в регистр 14, долж ны . быть -записаны как в адресн позиций,та и в соЬ вет6твующую позицию другого разряда памяти 11, например в поле А. Эта позиция ТШкЖйЙзУёУЙя при помоаШ адресной разностной информации, которая бша перенесена из процессора 12 в регистр 3. Разностн/ я адресная информация записывается в регистре 3 в начале процесса перемещения, и она указывает величину, которую следует добавить к адазесу, определягацему нуж 84 ную ПОЗИЦИЮ в разряде памяти 11 (в поле А), чтобы образовать адрес соответствующей позиции в разряде поля В. Триггер 8 с двумя устойчивыми состояниями запоминает индикатор, полученный по четвертому входу устройства, а триггер 7 с двумя устойчивыми состояниями считывает и отрабатывает указанный индикатор. Сумматор 4 выдает результирующий адрес посредством сложения адресной разнос.ти, записанной в регистре 3, с адресом, хранящимся в регистре 2, блок 5 вентилей, в соответствии с управляющими указаниями от первого триггера 7, пропускает либо адрес, записанный в адресном регистре 2, либо результирующий адрес, полученный сумматором 4 на первый выход устройства. Генератор 1 вырабатывает импульсы записи, В обычном случае, когда не требуется производить операции дополнительной записи, оба триггера находятся в состоянии О и индикация на четвертом входе отсутствует, когда на третий вход поступает команда записи. При этом записывающий элемент 6 вырабатывает импульс записи, который проходит через элемент ИЛИ 9, на второй выход уст- ройства и на элемент 10 задержки. По импульсу записи памятью 11 считывается информация из регистра 14. и записывается в позицию, указанную адресом, на первом выходе устройства. Если триггер 7 нахо, первый упдится в состоянии равляющий вход блока 5 вентилей возбуждается и последний пропускает адрес, записанный в регистре 2,, на первый выход устройства. После определенной временной задержки, соответствующей UHKJiy записи устройства запоминания данных, элемент 10 выдает импульс синхронизации на вход триггера 7, устанавливая его в положение, соответствующее условиям на его входах. Однако в соответствии с предположением, что триггер 8 находился в состоянии О, в триггере 8 не происходит изменений. Если на четвертый вход устройства поступает индикатор, помимо команды записи на третьем входе, триггер 8 будет находиться в состоянии i под действием этого индикатора, в это время начинается описанная процедура записи. После записи информации в регистр 14, разряд запоминающего устройства поля А,, триггер 7 получает импульс синхронизации от элемента 10 задержки, за счет чего состояние Tpifrrepa 8 переносите н в триггер 7. В блоке 5 вентилей возбуждается второй управляющий вход и результирующий

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство управления конвейерным вычислительным устройством | 1980 |

|

SU896623A1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для обработки информации мультипроцессорной системы | 1989 |

|

SU1619288A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

Авторы

Даты

1980-06-30—Публикация

1974-12-13—Подача