(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией программы | 1981 |

|

SU963108A2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Устройство для коррекции информации в блоке постоянной памяти | 1978 |

|

SU752501A1 |

| Запоминающее устройство с коррекцией информации | 1986 |

|

SU1392596A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

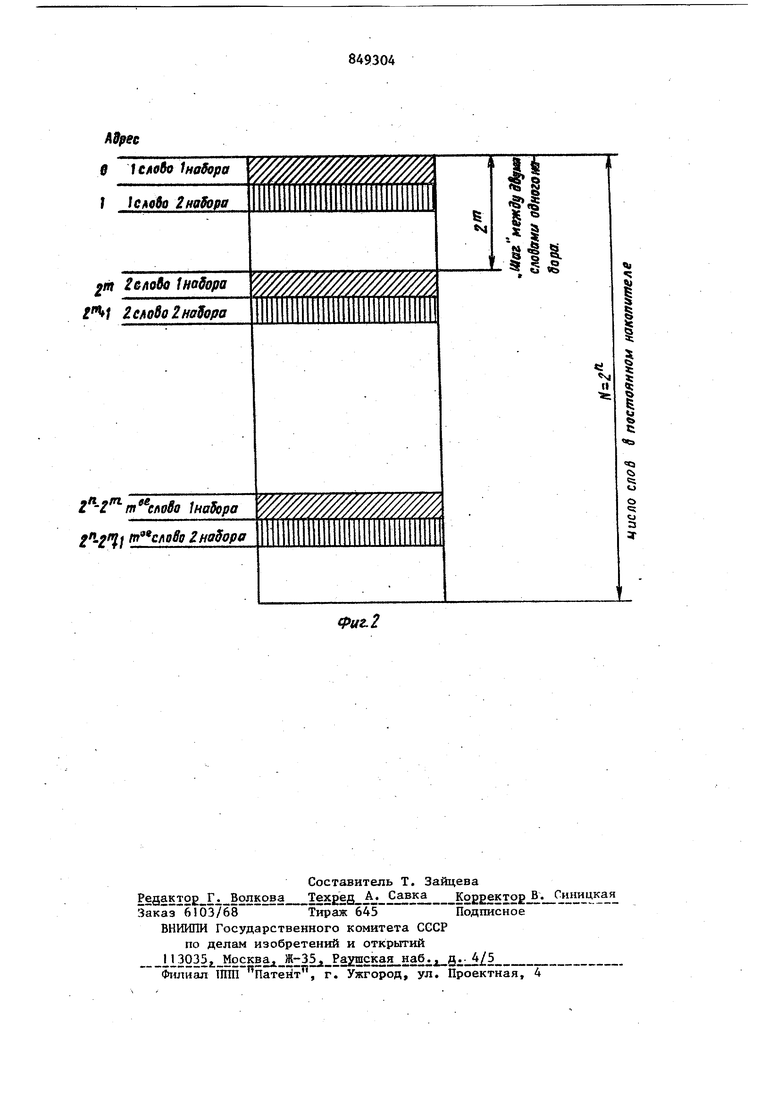

Изобретение относится к запоминающим устройствам. Известно устройство, которое содержит дешифратор адреса, накопители, шифраторы, блоки контроля, регистр числа, сумматоры по модулю дв и элементы И О . Недостатком этого устройства явл ется его сложность. Наиболее близким по технической сущности к предлагаемому является у ройство, содержащее адресный накопитель, схемы ИЛИ и блок коррекции дефектных ячеек, включающий в себя ассоциативный накопитель, в котором записаны адреса отказавших ячеек, причем при обращении к отказавшей ячейке происходит блокирование адрес ного накопителя и обращение к информационной части ассоциативного накопителя fz. Недостатком известного устройства является его низкая надежность вслед ствие сложности ассоциативного накопителя. Цель изобретения - повышение надеж ности устройства. Поставленная цель достигается тем, что в постоянное запоминающее устрой5СТВО с коррекцией информации, содержащее первый накопитель и группу элементов ИЛИ, причем одни из входов первого накопителя являются адрес- ными входами устройства,, а выходы подключены к одним из входов элементов ИЛИ группы, выходы которых являются выходами устройства, введены второй накопитель, схемы сравнения, группы элементов И, формирователь импульсов, регистр адреса и элемент ИЛИ, причем одни из входов второго накопителя подключены к одним из адресных входов устройства, первые входы схем сравнения соединены с другими адресными входами устройства, выходы второго накопителя подключены к первым входам элементов И первой группы и 384 вторым входам схем сравнения, -выходы которых .соединены соответственно с первыми входами элементов И второй группы, вторые входы которых подключены к первому выходу формирователя импульсов и другим входам первого накопителя, выходы элементов И второй группы соединены соответственно с одними из входов регистра адреса и со входами элемента ИЛИ, выход которого подключен ко входу формирователя импульсов, второй выход которого соединен с другим входом регистра адреса, а третий выход со вторыми входами элементов И первой группы, выходы которых подключены к другим входам элементов ИЛИ гругшы, выходы регистра адреса, соединены с другими входами второго накопителя. На фиг. 1 изображена функдиональпая схема предлагаемого.устройства; на фиг. 2 - расположение наборов слов в первом накопителе. Устройство содержит (фиг. 1) парвый накопитель 1, являющийся накопителем постоянного типа, группу элемен тов ИЛИ 2, регистр 3 адреса, второй накопитель 4, являющийся накопителем с адресной выборкой, первую группу элементов И 5, схемы 6 сравнения, вто рую группу элементов И 7, элемент ИЛИ 8 и формирователь 9 импульсов. из входов первого накопителя 1 являются адресными входами устройства, а выходы подключены к ОДНИ ИЭ входов элементов ИЛИ группы 2. Одни из входов второго накопителя 4 подклю чены к одним из адресных входов уст.ройства, первые входы схем сравнения 6 соединены с другими адресными входа ми устройства. Выходы второго накопителя 4 подключены к перйым входам элементов И первой группы 5 и вторым входам схем 6 сравнения, выходы кото рых соединены соответственно с первы входами элементов И второй группы 7, вторые входы которых подключены к пе вому выходу формирователя 9 импульсо и другим входам первого накопителя l Выходы элементов И второй группы 7 соединены соответственно с одними из входов регистра 3 адреса и со входами элемента ИШ 8, выход которого подключен ко входу формирователя 9 импульсов, второй вход которого соединен с другим входом регистра 3 адр са, а третий выход - со вторыми вход ми элементов И первой группы 5, выходы которых подключены к другим входам группы элементов ШТИ 2, Выходы регистра 3 адреса соединены с другими входами второго накопителя 4. Число наборов и число слов в наборе (фиг. 2) выбрано кратным целой степени двух, при этом если число слов в накопителе 1 равно , а число слов в наборе равно 2, то число наборов равно . На фиг. 2 обозначены 0,2, адреса последовательно расположенных корректируемых слов, входящих в первый набор и 1, , +1 - адреса корректируемых слов, входящих во второй набор. Устройство работает следующим образом. Для обнаружения и исправления слов, подлежащих коррекции, используется вто рой накопитель, разделенный на две оЬласти. Каждому из наборов слов (фиг.2) первого накопителя 1 (фиг, 1) соответствует определенное слово первой области второго накопителя 4, при этом номер набора слов первого накопителя 1 и номер слова в этой области второго накопителя 4 является соответственно младшими разрядами в поле адресов накопителей 1 и 4. Если необходимо исправить некоторое слово в первом накопителе 1, то по номеру набора, к которому принадлежит это слово, определяется соответствующее слово первой области во втором накопителе 4, в которое записьшается номер слова в этом наборе, т.е. старшие к разрядов адреса корректируемого слова в поле адресов первого накопителя 1 . В соответствии с разрядностью б слова второго накопителя 4 в него может быть записано j номеров слова в наборе, где j - ближайшее целое число меньшее или равное (f - 1). В соответствии с расположением номе ра. к оррек тируемого слова первого накопителя 1 в наборе в слове второй области второго накопителя 4 записывают скорректированную информацию (j слов). Работу устройства рассмотрим на примере коррекции слов в первом накопителе I, имеющем объем 64 К 36 разрядных чисел, причем второй накопитель 4 имеет объем 1К 36 раз. рядных чисел. Разобъем слова первого накопителя I на 256 наборов по 256 схлов в каждом наборе (). Согласно этому разбиению, первая область второго накопителя 4 также, равна 256 словам (по числу наборов) В каждом слоие первой области записьгааем j номера слов в соответствующем наборе (8 старших разрядов адреса корректируемых слов). Таким образом, при обращении к лйбому слову.первого накопителя Г одновременно производится обращение к соответствующему слову первой области второго накопителя 4. Считанная информация (ноль, один, два, или три номера корректируемых слов в наборе) поступает на три схемы 6 сравнения, на вторые входы которых поступают старшие восемь разрядов адреса слова в поле адресов первого накопителя 1. В случае совпадения кодов на входах одной из схем 6 сравнения, сигнал с ее выхода через соответствующий элемент И второй группы 7 на . элемент ИЛИ 8 поступает на формирователь 9 импульсов, генерирующий импульсы, один из которых блокирует выход первого накопителя I на группы элементов ИЛИ 2, другой - открывает путь для .прохождения корректирующей информации с выхода второго накопителя 4.на входы группы элементов ИЛИ 7, поступают также на регистр 3 адре са где устанавливается код в соответствии с номером группы элемента ИЛИ 7. Этот код (старшие разряды адр са слова во второй области второго накопителя 4, где хранится корректирующая информация) поступает на вход второго накопителя 4. После извлечен корректирующей информации из него формирователь 9 импульсов устанавливает регистр 3 адреса вновь в исходн состояние соответствующее обращению к первой области второго накопителя Технико-экономическое преимущество предлагаемого устройства заключае ся в повьшешш его надежности за сче замены сложного ассоциативного накоп :теля, используемого в известном устАройстве, накопителем с адресной выборкой. Формула изобретения Постоянное запоминающее устройство с коррекцией информации, содержащее первый накопитель и группу элементов ИЛИ, причем одни из входов первого накопителя являются адресными входами устройства, а выходы подключены к одним из входов элементов ИЛИ группы, выходы которых являются выходами устройства, отличающее-. с я тем, что, с целью повыщения надежности устройства, оно содержит второй накопитель, схемы сравнения, группы элементов И, фop шpoвaтeль им-г пульсов, регистр адреса и элемент ИЛИ, причем одни из входов второго накопителя подключены к одшм из адресных входов устройства, первые входы схем сравнения соединены с другими адресными входами устройства, выходы второго накопителя подключены к первым входам- элементов И первой группы и вторым входам схем сравнения, выходы которых соединены соответственно с первыми входами элементов И второй группы, вторые входы которьк подключены к первому выходу формирователя импульсов и другим входам первого накопите- , ля, выходы элементов И второй группы соединены соответственно.с бднимн из входов регистра адреса и со входами элемента ИЛИ, выход которого подключенко входу формирователя импульсов, второй выход которого соединен с другим входом регистра адреса, а третий выход - со вторыми входами элементов И первой группы, выходы которых подключены к другим входам элементов ИНН группы, выходы- регистра адреса соединены с другими входами второго накопителя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 568081, кл. G 1 С 17/00, 11 С 29/00, 1977. 2.Автоматика и телемеханика,. № 7, 1974, с. 162, (прототип).

I

t----- s

Ф

Tmniii

H ДГ

ж

«a

Ф

е 1 с лево iHofopa

1 слово 2надора

т Белова 1надора

2ело8о 2набора

«

I

Ǥ 1

is § 5 «л «е

«NI II

ч

Г-г т слоЗо 1 набора

с/дД iHaSopa

чэ

г

§

о

5

S .2

Авторы

Даты

1981-07-23—Публикация

1979-11-20—Подача