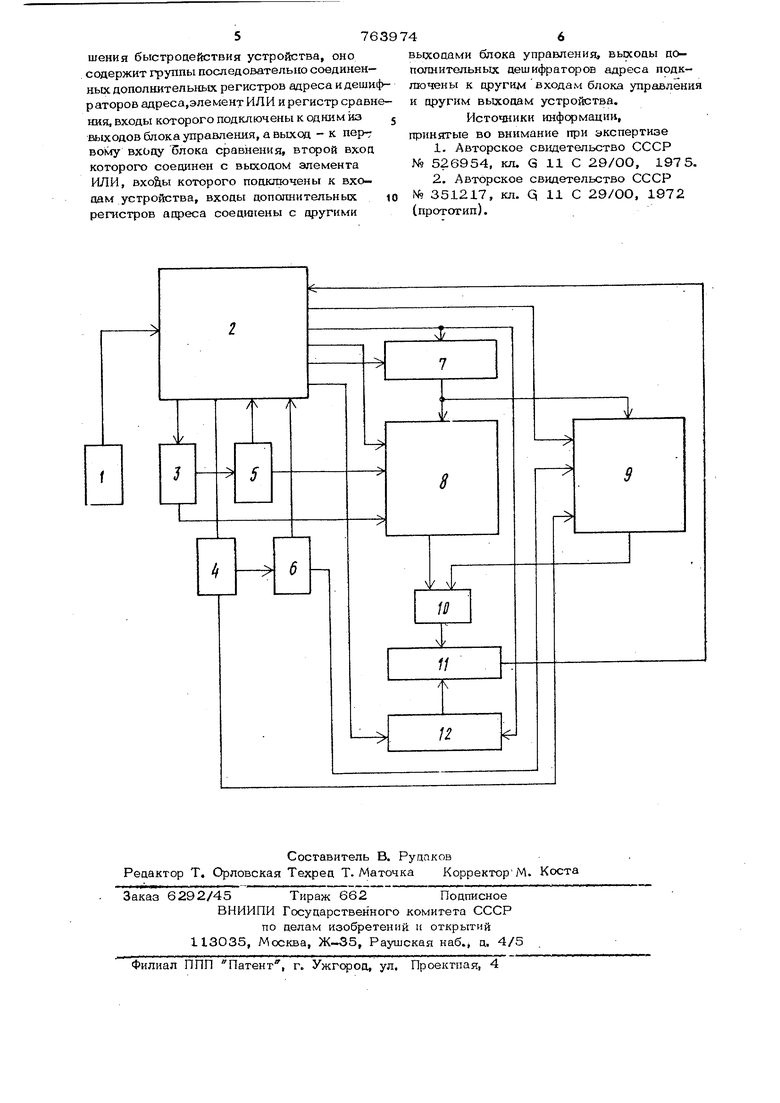

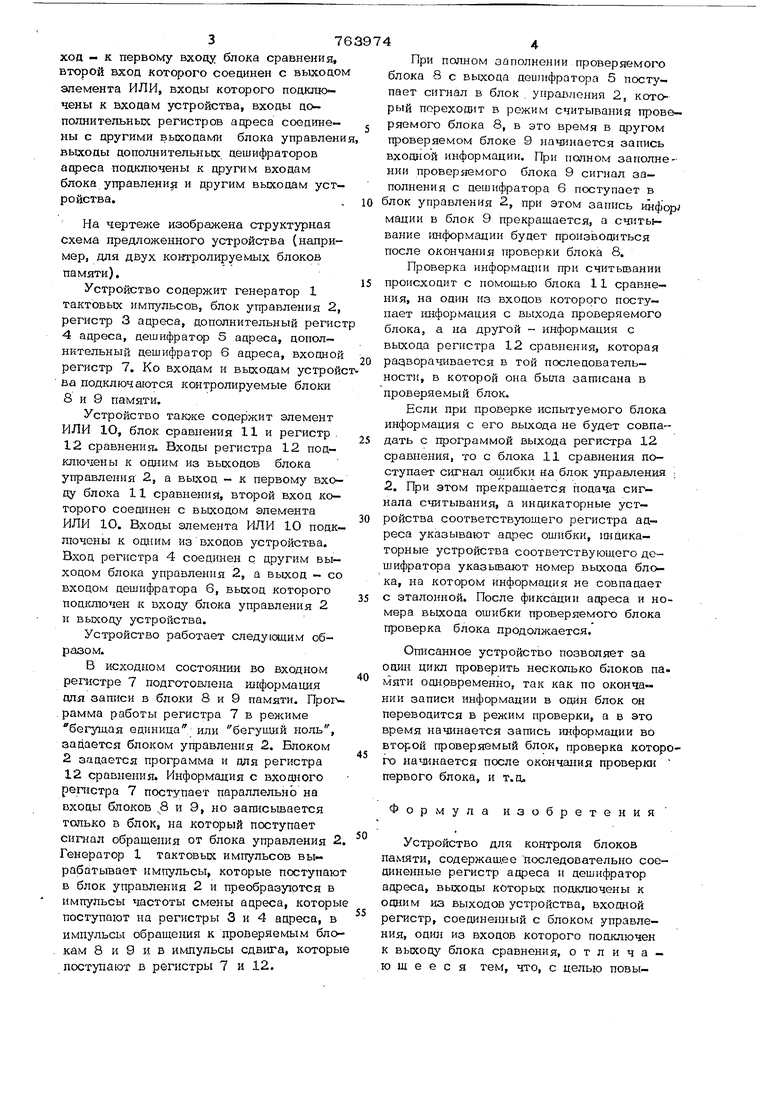

Изобретение относится к запоминающим устройствам. Известны устройства для контроля блоков памяти . Одно из известных устройств содержит счетчик адресов, подключенный к блоку формирования адресов, блоку сравнения адресов и блоку анализа, коммутатор, соешшенный с блоком формиров ния чисел, счетчик циклов, подключенны к блоку сравнения адресов и блЬку сравнения циклов, блок формирования сигналов управления, соединенный с программным блоком и блоком управления, счет чик адресных операций, дешифратор, бло сравнения количества циклов и амплитудно-временной дискриминатор . Недостатком этого устройства являет ся то, что за цикл проверки оно мсисет 1фсверить только один блок памяти, т.е. устройство обладает ограниченной пропускной способностью за цикл проверки. Кроме того, устройство характеризуется большими аппаратурными затратами. Наиболее близким техническим решением к изобретению является устройство для контроля памяти, содержащее последовательно соеоиненные регистр адреса и дешифратор адреса, выходы которых поцключень к одним из вьосоцов устройства, входной регистр, соединенный с блоком управления, один из входов которого подключен к выходу блока сравнения QSj. Недостатком этого устройства является невысокая скорость работы, обусловленная тем, что с его помощью можно проверить только один блок памяти за цикл. Цель, изобретения - повьпиение быстродействия устройства. Поставленная цель достигается тем, что в устройство вредены группы последовательно соециненньк дополнительных регистров адреса, и дешифраторов адреса, элемент ИЛИ и регистр сравнения, входы которого подключены к одним из выходов блока у правлен ия а вы37хоц - к первому входу блока сравнения, второй вход которого соединен с выходо элемента ИЛИ, входы которого подключены к входам устройства, входы дополнительных регистров афеса соединены с другими выходами блока управлен выходы дополнительных дешифраторов асфеса подключены к другим входам блока управление и другим выходам устройства. На чертеже изображена структурная схема предложенного устройства (например, для двух контролируемых блоков памяти). Устройство содержит генератор 1 тактовых импульсов, блок управления 2, регистр 3 адреса, дополнительный регис 4 адреса, дешифратор 5 адреса, допол- нительный дешифратор б адреса, регистр 7. Ко входам и вькодам устрой ва подключаются контролируемые блоки 8 и 9 памяти. Устройство такгке содержит элемент ИЛИ 1О, блок сравнения 11 и регистр . 12 сравнения. Входы регистра 12 подключены к одним из выходов блока управления 2, а выход - к первому входу блока 11 сравнения, второй вход которого соединен с выходом элемента ИЛИ 10. Входы элемента ИЛИ 10 подк лючены к одним из входов устройства. Вход регистра 4 соединен с другим выходом блока управления 2, а выход - со входом дешифратора 6, выход которого подключен к входу блока управления 2 и выходу устройства. Устройство работает следующим образом. В исходном состоянии во входном регистре 7 подготовлена шгформация для записи в блоки 8 и 9 памяти. Прог . рамма работы регистра 7 в ренсиме единица, или бегущий ноль, задается блоком управления 2. Блоком 2 задается программа и для регистра 12 сравнения. Информация с вхошюго регастра 7 поступает параллельно на входы блоков .8 и 9, но записывается только в блок, на который поступает сигнал обращения от блока управления 2 Генератор 1 тактовых импульсов вырабатывает импульсы, которые поступаю в блок управления 2 и преобразу1отся в импульсы частоты смены адреса, которы поступают на регистры 3 и 4 адреса, в импульсы обращения к проверяемым бло . кам 8 и 9 и в импульсы сдвига, котор поступают в регистры 7 и 12. При полном заполнении проверяемого блока 8 с выхода дешифратора 5 поступает сигнал в блок . управления 2, который переходит в режим считывания проверяемого блока 8, в это время в другом проверяемом блоке 9 начинается запись входной информации. При полном заполнении проверяемого блока 9 сигнал заполнения с дешифратора 6 поступает в лок управления 2, при этом запись вдфор мации в блок 9 прекращается, а считывание 1шформации будет производиться после окончания проверки блока 8. Проверка информации при считьюании происходит с помощью блока 11 сравнения, на один из входов которого поступает 1шформация с выхода проверяемого блока, а на другой - информация с выхода регистра 12 сравнения, которая радвор ачивае тс я в той по лёдователь которой она бьша записана в проверяемый блок. Если при проверке испытуемого блока информация с его выхода не будет совпадать с программой выхода регистра 12 сравнения, то с блока 11 сравнения поступает сигнал ошибки на блок управления ; 2. При этом прекращается подача сигнала считывания, а индикаторные уст- ройства соответствующего регистра адреса указывают адрес ошибки, 1шцика- торные устройства соответствующего дешифратора указьюают номер выхода блока, на котором информадия не совпадает с эталонной. После фиксации адреса и номера выхода ошибки проверяемого блока проверка блока продолжается, Ош санное устройство позволяет за один цикл проверить несколько блоков па. мяти ош рвременно, так как по окончании записи информации в один блок он переводится в режим проверки, а в это время начинае1х;я запись информации во второй провер51емый блок, проверка которого нагв1нается после окончания проверки первого блока, и т.д. Формула изобретения Устройство для контроля блоков памяти, содержаш.ее последовательно соединенные регистр адреса и дешифратор адреса, выходы которых подключены к опним из выходов устройства, входной регистр, соединенный с блоком управления, один из входов которого подключен к выходу блока сравнения, о т л и ч а ю ш е е с я тем, что, с целью повы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокапАМяТи | 1979 |

|

SU801106A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля программ и микропрограмм | 1983 |

|

SU1176334A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

Авторы

Даты

1980-09-15—Публикация

1978-01-13—Подача