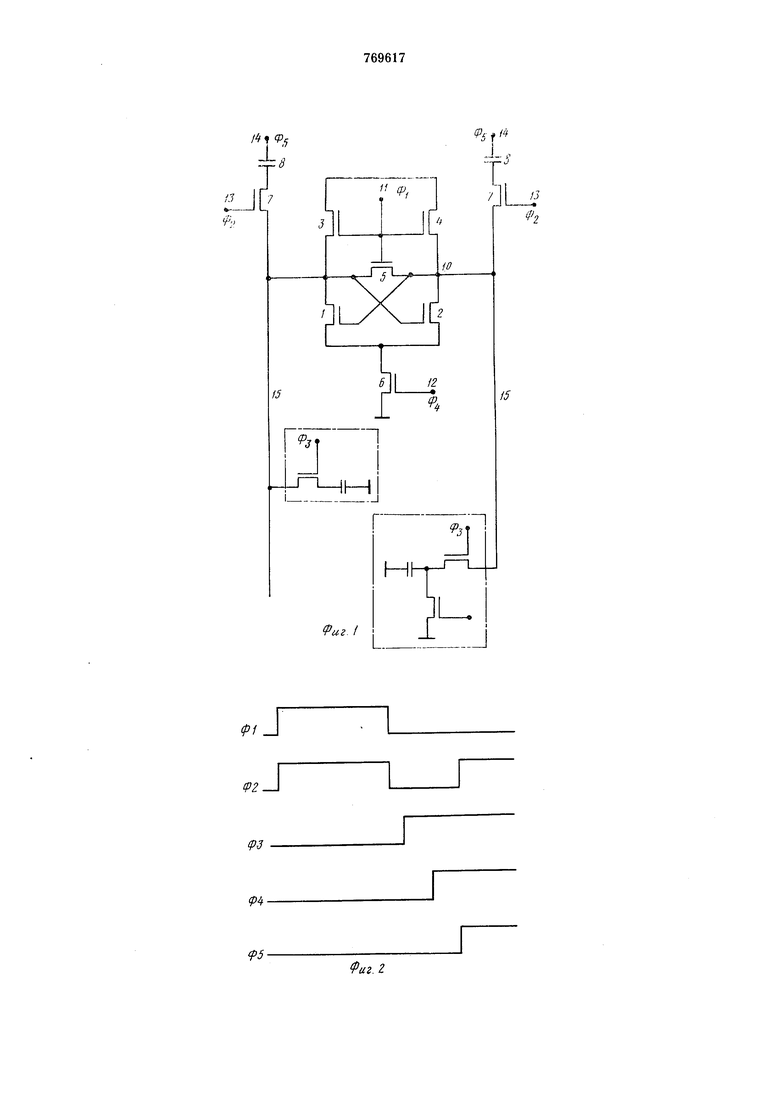

ответствующее хранившейся в элементе памяти информации.

На время выбора строки отключается конденсатор 8 от разрядной шины. После установления напряжения на входных шинах усилителя на затвор транзистора 6 подается напряжение Ф и через открывшийся транзистор 6 происходит разряд одного из плеч усилителя -в зависимости от хранившейся в элементе памяти информации. При этом если в элементе памяти хранился «О, будет разряжено левое плечо усилителя, если в элементе памяти хранилось «1, - правое плечо усилителя.

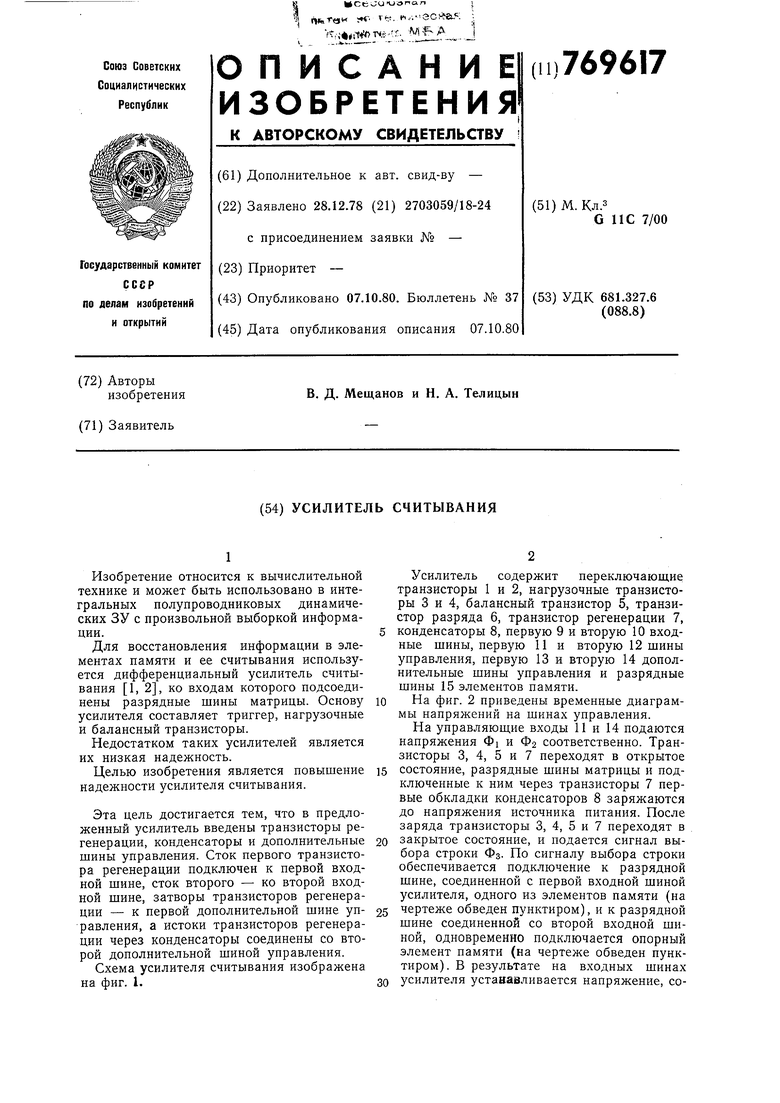

После разряда одного из плеч дифференциального усилителя для восстановления уровня логической единицы на дополнительные шины управления 14 и 15 подаются напряжения Фа и Фб соответственно.

Напряжение Фб создает на первой обкладке конденсатора 8 уровень напряжения, превосходяший уровень напряжения на разрядной шине. Избыточный заряд с первой обкладки конденсатора 8 через открытый транзистор 7 проходит на разрядную шину. Заряд, пришедший на разрядную шину с единичной информацией, восстанавливает уровень логической единицы, заряд, пришедший на второе (открытое) плечо усилителя, через открытые транзисторы 2 и 6 проходит на шину нулевого потенциала, не изменяя потенциала разрядной шины.

Формула изобретения

Усилитель считывания, содержащий два переключающих транзистора, сток первого

из которых соединен с затвором второго переключающего транзистора и первой входной шиной, сток второго переключающего транзистора соединен с затвором первого переключающего транзистора и второй входной шиной, два нагрузочных транзистора, стоки которых объединены, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора и

первой входной шиной, сток - с истоком второго нагрузочного транзистора и второй входной шиной, а затвор - с затворами нагрузочных транзисторов и первой шиной управления, разрядный транзистор, сток

которого соединен с истоками переключающих транзисторов, исток - с шиной нулевого потенциала, а затвор - с второй шиной управления, отличающийся тем, что, с целью повышения надежности устройства, оно содержит транзисторы регенерации, конденсаторы и дополнительные шины управления, причем сток первого транзистора регенерации подключен к первой входной шине, сток второго - ко второй входной шине, затворы транзисторов регенерации - к первой дополнительной шине управления, истоки транзисторов регенерации через конденсаторы соединены с второй дополнительной шиной управления.

Источники информации, принятые во внимание при экспертизе

1. «Электроника, № 13, 1973, с. 43-51. 2. «Электроника, N° 4, 1976, с. 44-52 (прототип).

J

/J I

V.1

(P. f /4

t

/J

72

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

/

15

J

fuz.l

/

z

6 f2

15

f

.J

.J

Авторы

Даты

1980-10-07—Публикация

1978-12-28—Подача