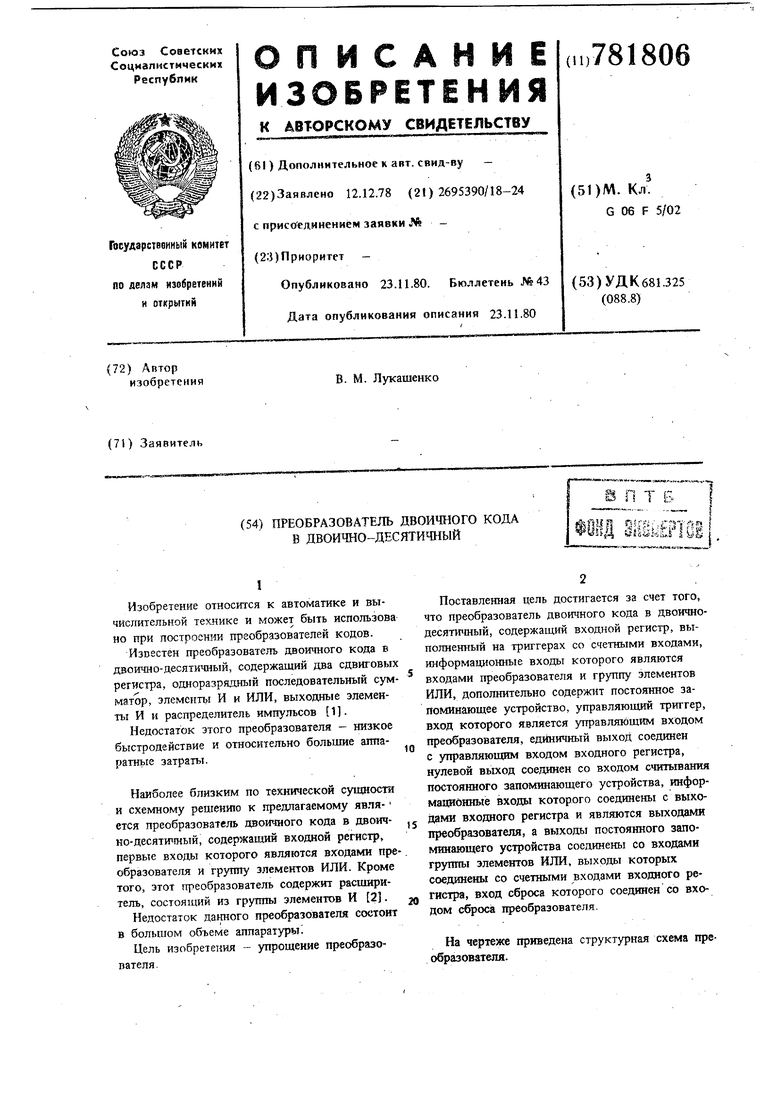

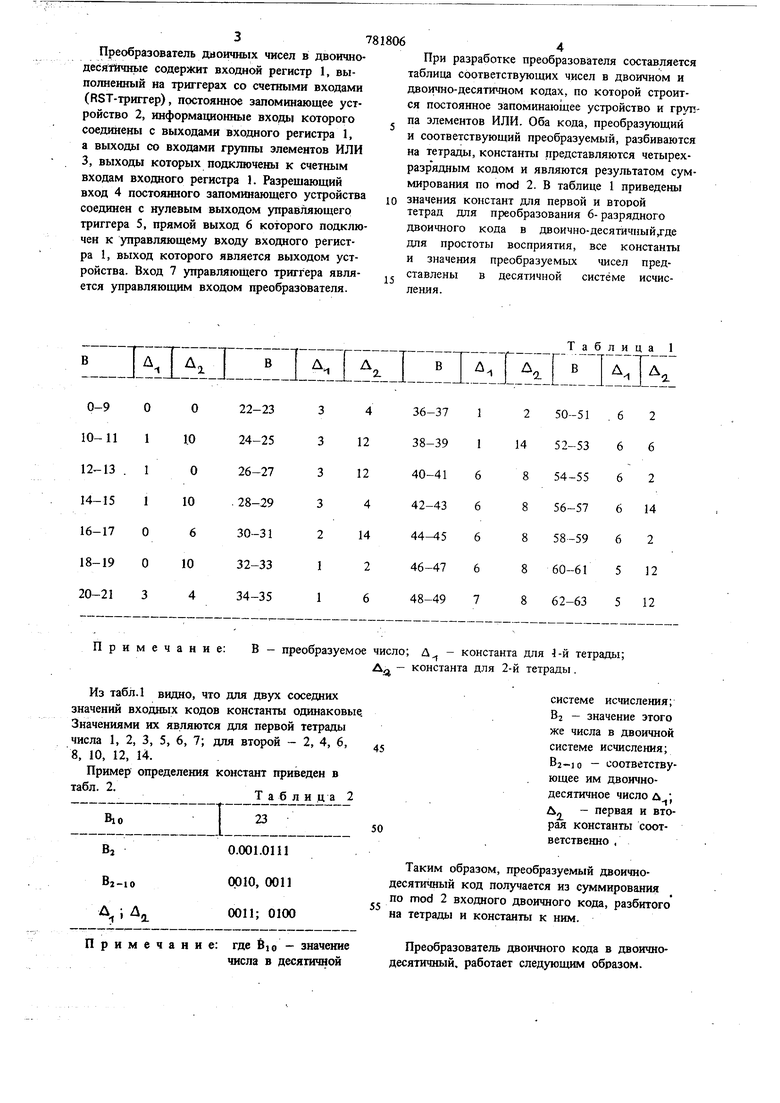

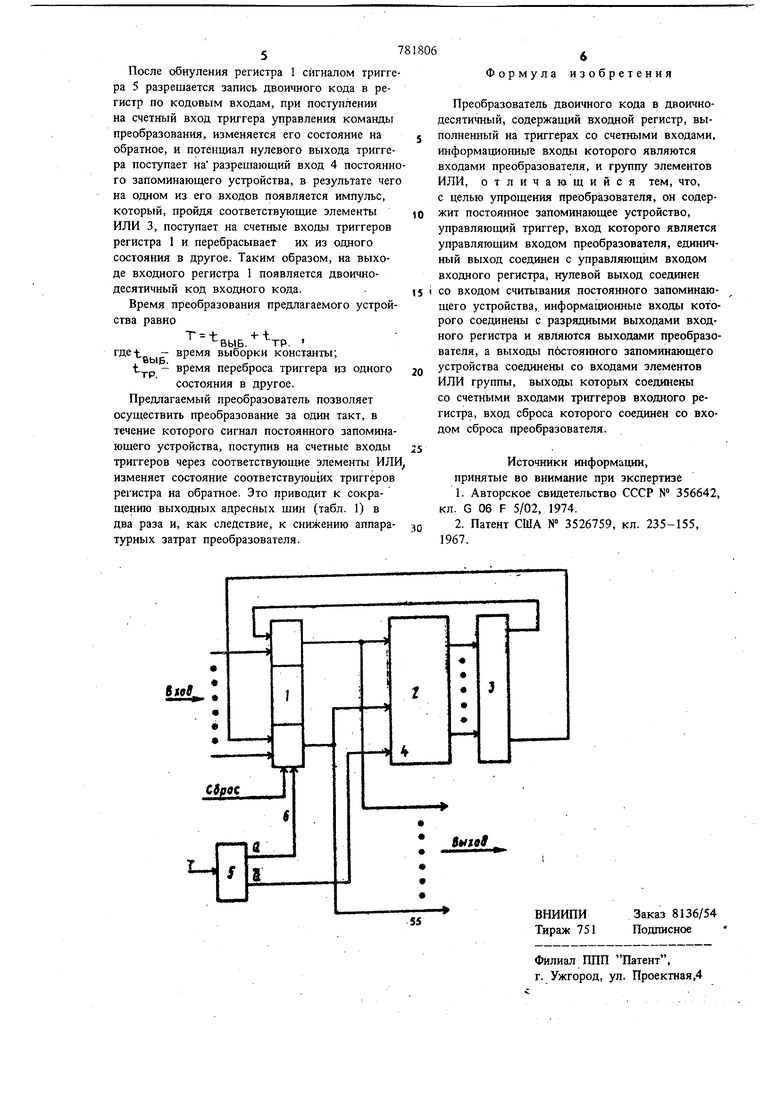

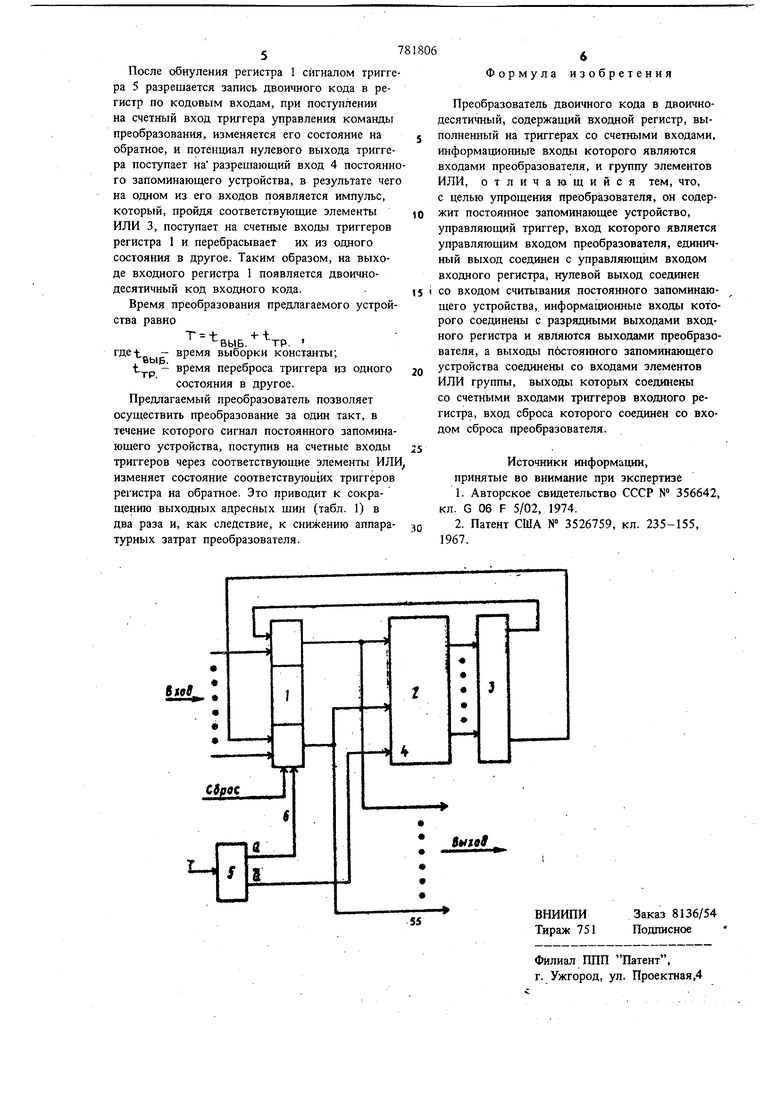

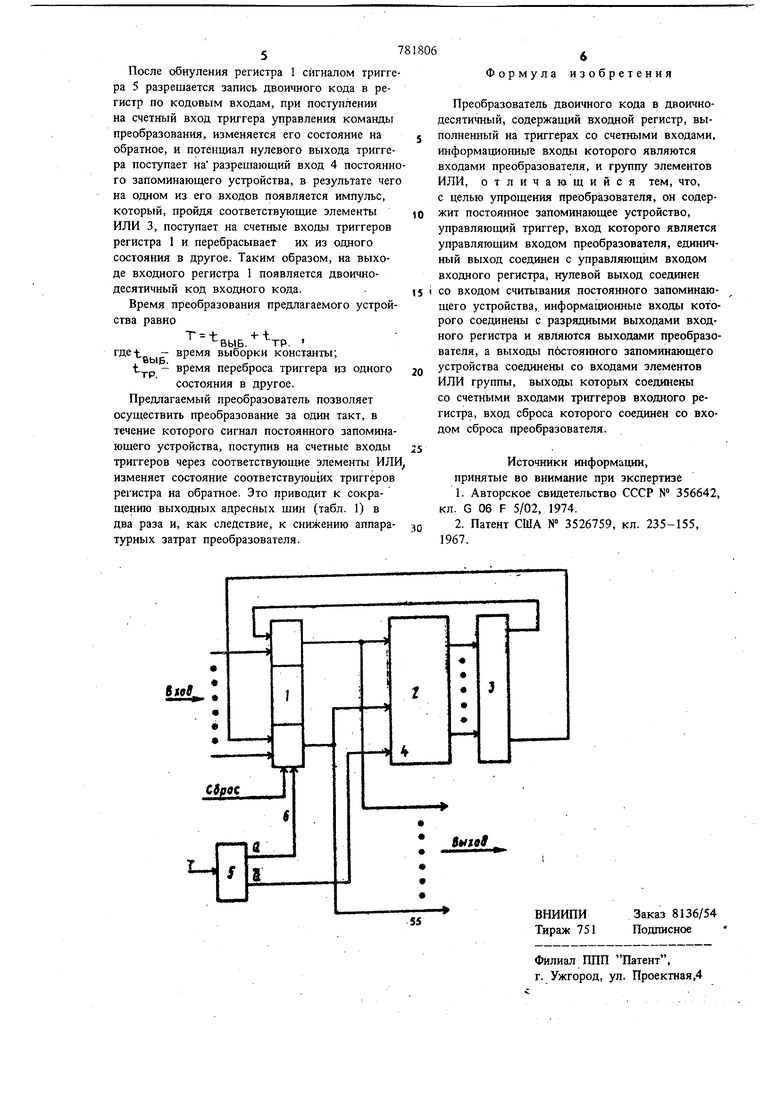

3 Преобразователь двоичных чисел в двоичнодесятйчнь1е содержит входной регистр 1, выполненный на триггерах со счетными входами (RST-триггер), постоянное запоминающее устройство 2, информационные входы которого соединены с выходами входного регистра 1, а выходы со входами группы элементов ИЛИ 3, выходы которых подключены к счетным входам входного регистра 1. Разрешающий вход 4 постоянного запоминающего устройства соединен с нулевым выходом управляющего триггера 5, прямой выход 6 которого подклю чен к управляющему входу входного регистра 1, выход которого является выходом устройства. Вход 7 управляющего триггера является управляющим входом преобразователя. При разработке преобразователя составляется таблица соответствующих чисел в двоичном и двоично-десятичном кодах, по которой строится постоянное запоминающее устройство и гр /тзпа элементов ИЛИ. Оба кода, преобразующий и соответствующий преобразуемый, разбиваются на тетрады, константы представляются четырехразрядным кодом и являются результатом суммирования по mod 2. В таблице 1 приведены значения констант для первой и второй тетрад для преобразования 6- разрядного двоичного кода в двoичнo-дecятичный дe для простоты восприятия, все константы и значения преобразуемых чисел представлены в десятичной системе исчисления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

Примечание: В - Из табл.1 видно, что для двух соседних значений входных кодов константы одинаковы Значениями их являются для первой тетрады числа 1, 2, 3, 5, 6, 7; для второй - 2, 4, 6, 8, 10, 12, 14. Пример определения констант приведен в - 2-Таблица 2 0.001.0111 OplO, ООП i г ООП; 0100 Примечание: где бю - значение числа в десятичной

Таблица 1 преобразуемое число; Д константа для 1-й тетрады; Дд - константа для 2-й тетрады. системе исчисления; БЗ - значение этого же числа в двоичной системе исчисления; Ва-ю - соответствующее им двоичнодесятичное число д ; Лл - первая и вторая константы соответственно , Таким образом, преобразуемый двоичноесятичный код получается из суммирования о mod 2 входного двоичного кода, разбитого а тетрады и константы к ннм. Преобразователь двоичного кода в двоичноесятичный, работает следующим образом. 5 После обнуления регистра 1 сигналом тригг ра 5 разрешается запись двоичного кода в регистр по кодовым входам, при поступлении на счетный вход триггера управления команды преобразования, изменяется его состояние на обратное, и потенциал нулевого выхода тригге ра поступает на разрешающий вход 4 постоянн го запоминающего устройства, в результате чег на одном из его входов появляется импульс, который, пройдя соответствующие элемен1ы ИЛИ 3, поступает на счетные входы триггеров регистра 1 и перебрасывает их из одного состояния в другое. Таким образом, на выходе входного регистра 1 появляется двоичнодесятичный код входного кода. Время преобразования предлагаемого устрой ства равно ВЫБ.Чр. . ВЫБ Р выборки константы; t-pp - время переброса триггера из одного состояния в другое. Предлагаемый преобразователь позволяет осуществить преобразование за один такт, в течение которого сигнал постоянного запоминающего устройства, поступив на счетные входы триггеров через соответствующие элементы ИЛИ изменяет состояние соответствующих триггеров регистра на обратное. Это приводит к сокращению выходных адресных щин (табл. 1) в два раза и, как следствие, к снижению аппаратурных затрат преобразователя. 6 Формула изобретения Преобразователь двоичного кода в двоичнодесятичный, содержащий входной регистр, выполненный на триггерах со счетными входами, информационные входы которого являются входами преобразователя, и группу элементов ИЛИ, отличающийся тем, что, с целью упрощения преобразователя, он содержит постоянное запоминающее устройство, управляющий триггер, вход которого является управляющим входом преобразователя, единичный выход соединен с управляющим входом входного регистра, нулевой выход соединен со входом считывания постоянного запоминающего устройства, информационные входы которого соединены с разрядными выходами входного регистра и являются выходами преобразователя, а выходы постоянного запоминающего устройства соединены со входами элементов ИЛИ группы, выходы которых соединены со счетными входами триггеров входного регистра, вход сброса которого соединен со входом сброса преобразователя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 356642 кл. G 06 F 5/02, 1974. 2.Патент США № 3526759, кл. 235-155 1967.

Авторы

Даты

1980-11-23—Публикация

1978-12-12—Подача