УСТРОЙСТВО для УМНОЖЕНИЯ ПОСЛЕДОВАТЕЛЬНОГО

(54) КОДА НА ДРОБНЫЙ КОёФФИЦИЕНТ

;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения | 1983 |

|

SU1129606A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

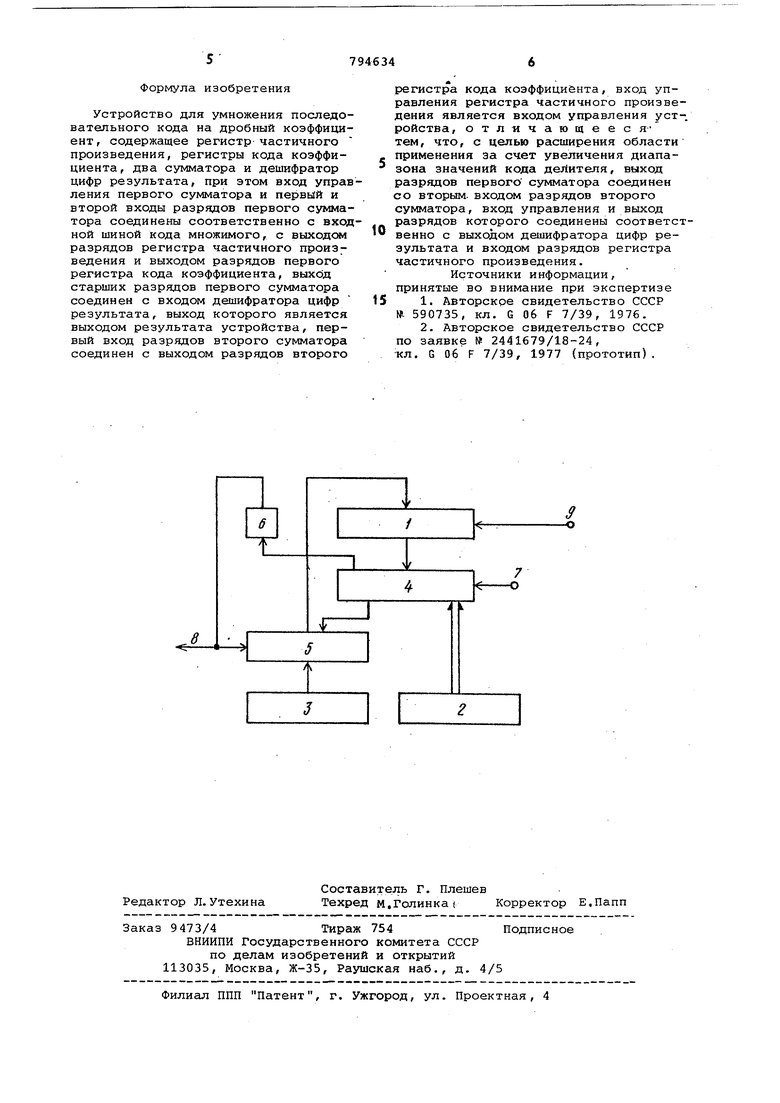

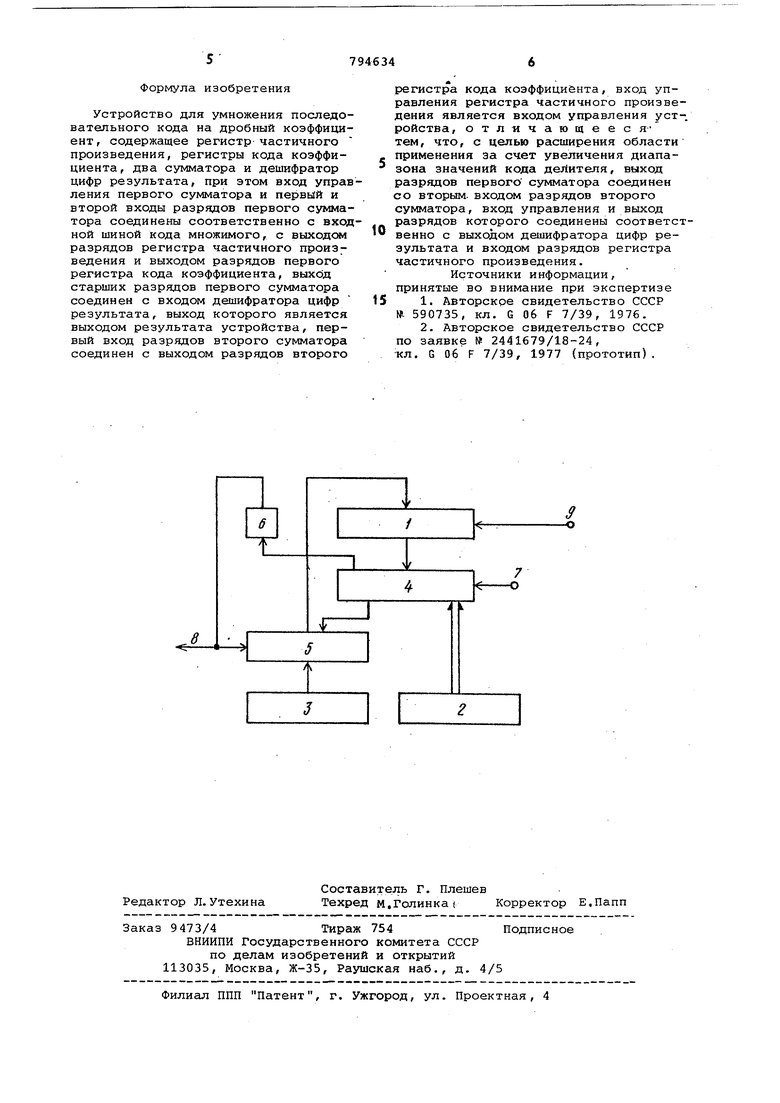

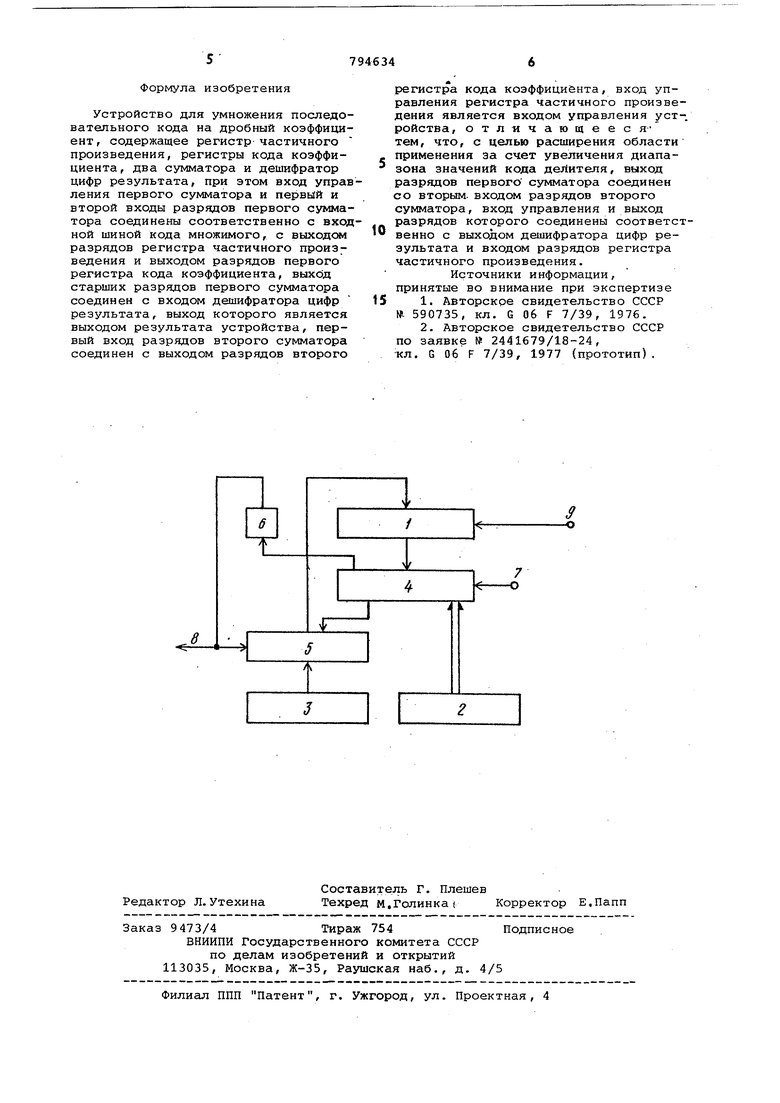

Изобретение относится к областивычислительной техники и может быть применено для умножения на дробный коэффициент числа, представленного последовательным Д1воичным квазиканоническим модифицированным кодом. Известно устройство 1} для умножения на коэффициент, содержащее гене ратор импульсов, элемент И, делители частоты, счетчики и блок совпгщения кодов. Однако оно не позволяет совмещать во времени процессы поразрядного ввода операнда, вычисления и поразрядной выдачи результата, что может быть необходимым, если операнды на входе и выходе устройства представлены последовательным кодом (например, в случае ограничений на количество внещних выводов при изготовлении устройст ва в виде БИС). Наиболее близким по технической сути к изобретению является устройст во 2, содержащее регистр частичного произведения, регистры кода ко эффициента, два сумматора идешифратор цифр результата, при этом вход управления первого сумматора и первый и второй входы разрядов первого сумматора соединены соответственно с входной шиной кода множимого, с выходом разрядов регистра частичного произведения и выходом разрядов регистра кода коэффициента, выход старших разрядов первого сумматора соединен с входом дешифратора цифр результата, выходы которого являются выходом результата устройства. Первый вход разрядов второго сумматора соединен с выходом разрядов второго регистра кода коэффициента, вход управления регистра частично произведения является входом управления устройства. Функциональные возможности такого устройства ограничены, поскольку устройство позволяет умножать число на дробный коэффициент только в том случае, если знаменатель коэффициента является целой степенью основания системы счисления. Целью изобретения является расширение функциональных возможностей устройства, Поставленная цель достигается тем, что в устройстве, содержащем регистр частичного произведения, регистры кода коэффициента, два сумматора и дешифратор цифр результата, при эхом вход управления первого сумматора и первый и второй входы разря дов первого сумматора соединены соответственно с входной шиной, кода множимого, с выходом разрядов регист ра частичного произведения и выходом разрядов первого регистра кода коэффициента, выход старших разрядов пер )вого сумматора соединен с входом дешифратора цифр результата, выход которого яв-ляется выходом результата устройства, первый вход разрядов вто го сумматора соединен с выходом разр дов второго регистра кода коэффициен та, вход управления регистра частичного произведения является взсодом управления устройства, дополнительно введены связи; выход разрядов первого сумматора соединен со вторым входом разрядов второго сумматора, вход управления и выход разрядов которого соединены соответственно с выходом д шифратора цифр результата и входом разрядов регистра частичного произведения. На чертеже приведена схема устройс ва . Устройство содержит регистр 1 час тичного произведения, первый 2 и второй 3 регистры кода коэффициента, сумматоры 4, 5, дешифратор 6 цифр результата, входную шину 7 кода множимо го. Дешифратор 6 цифр результата пред ставляет собой комбинационную схему, реализующую следующие логические функ ции f а () где индексы аргументов соответствуют номе)ам разрядов сумматора 4, f и f2 с значения цифр (соответственно 1 и 1) результата. Устройство работает следующим образом. В исходном состоянии (цепи установ ки исходного состояния на чертеже не показаны) в регистре 1 записаны нули в первом регистре 2 числитель Л коэффициента, а во втором регистре 3 число 1-В,.т.е. дополнительный код знаменателя В коэффициента. Значения А и В удовлетворяют условиям 0,,

2

О

е

0001100000 00011 11101 0000011101

е

0000ООН 1111 0001 11111110

0001100110 00001 11111 1111011003

.4

.0 1 о о о 1

001

000

111 011

.5

4 Т

000

111

000

000 110 001

111

000 в каждом i-м цикле вычисления на входную шину 7 кода множителя поступает цифра операнда X с весом , (где р - количество разрядов) , после которых фиксируется запятая в X. Эта цифра управляет видом операции, выполняемой сумматором таким образом, что на сумматоре 4 складывается содержимое регистра 1 с прямым кодом содержимого регистра 2, если цифра равна плюс единице, и с дополнительным кодом - если цифра равна минус единице, и код регистра 2 не выдается на суммирование, если эта цифра равна нулю. Дешифратор цифр результата б, анализируя содержимое трех старших разрядов сумматора 4, формирует цифру результата У. Бели на выходе указанных разрядов 000 или 111, то цифра результата равна нулю, в остальных случаях цифра результата равна по модулю единице, а ее знак равен знаку кода сумматора 4. Цифра результата выдается из устройства по выходной шине 8 Чи, описанным выше способом для сумматора 4) и управляет видом операции, выполняемый сумматором 5, где происходит сложение прямого или дополнительного кода регистра 3 с кодом сумматора 4. Цикл заканчивается сигналом на входе управления 9, по которому код сумматора 5 принимается в регистр 1. Работа устройства на числовом примере для значений А , 011 3/8, В , 111 7/8, X lOllOl 35 поясняется таблицей 1, где получена цифра результата У 010001 15. Как видно из примера, предлагамое устройство позволяет совмещать во времени процессы порязрадного ввода операнда и вывода результата при вычислении функции у - К. Однако в отличие от устройства-прототипа для предлагаемого устройства не требуется, чтобы В 2, где с - целое. Следовательно, предлагаемое устройство может найти более широкое применение.

Формула изобретения

Устройство для умножения последовательного кода на дробный коэффициент , содержащее регистр частичного произведения, регистры кода коэффициента, два сумматора и дешифратор цифр результата, при этом вход управления первого сумматора и первый и второй входы разрядов первого сумматора соединены соответственно с входной шиной кода множимого, с выходом разрядов регистра частичного произ ведения и выходом разрядов первого регистра кода коэффициента, выход старших разрядов первого сумматора соединен с входом дешифратора цифр результата, выход которого является выходом результата устройства, первый вход разрядов второго сумматора соединен с выходом разрядов второго

регистра кода коэффициента, вход управления регистра частичного произведения является входом управления уст ройства, отличающеесятем, что, с целью расширения области применения за счет увеличения диапазона значений кода делителя, выход разрядов первого сумматора соединен со вторым, входом разрядов второго сумматора, вход управления и выход разрядов которого соединены соответсвенно с выходом дешифратора цифр результата и входом разрядов регистра частичного произведения.

Источники информации, принятые во внимание при экспертизе

кл. G Об F 7/39, 1977 (прототип).

Авторы

Даты

1981-01-07—Публикация

1979-02-02—Подача