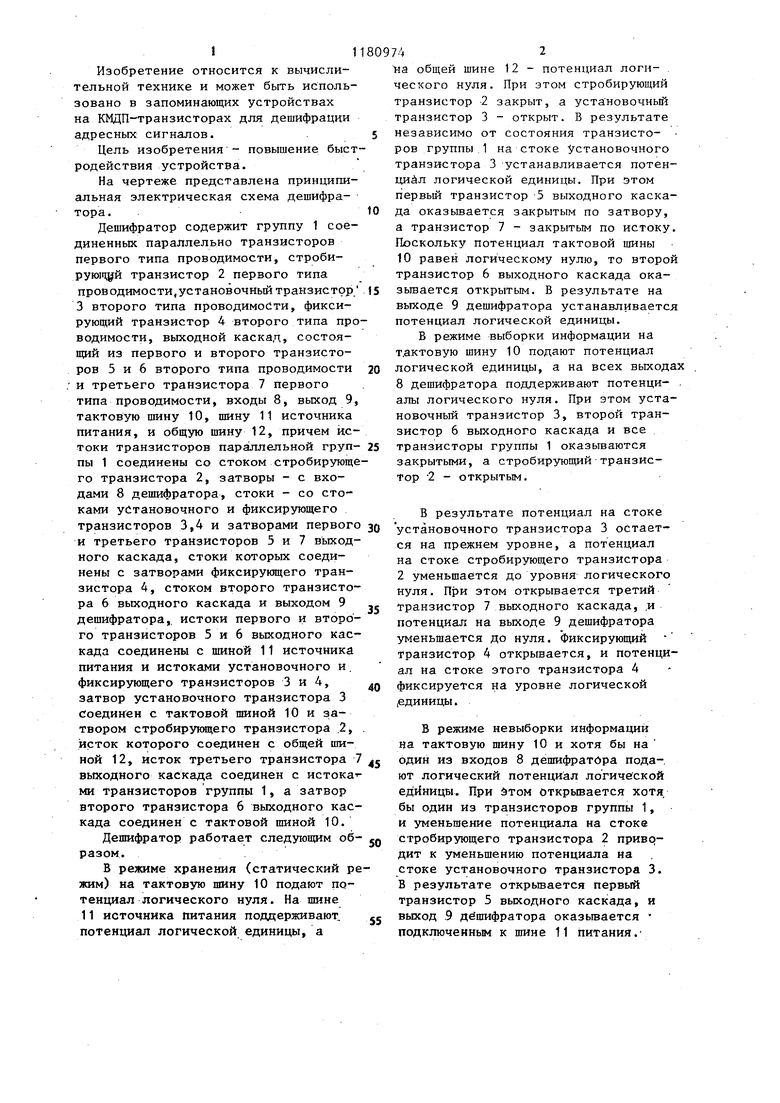

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах для дешифрации адресных сигналов.. Цель изобретения - повышение быст родействия устройства. На чертеже представлена принципиальная электрическая схема дешифратора. Дешифратор содержит грзшпу 1 соединенных параллельно транзисторов первого типа проводимости, стробируюнщй транзистор 2 первого типа проводимости,установочный транзистор 3 второго типа проводимости, фиксирующий транзистор 4 второго типа про водимости, выходной каскад, состоящий из первого и второго транзисторов 5 и 6 второго типа проводимости и третьего транзистора 7 первого типа проводимости, входы 8, выход 9 тактовую шину 10, шину 11 источника питания, и общую шину 12, причем истоки транзисторов параллельной группы 1 соединены со стоком стробирующ го транзистора 2, затворы - с входами 8 дешифратора, стоки - со стоками установочного и фиксирующего транзисторов 3,4 и затворами первог и третьего транзисторов 5 и 7 выходного каскада, стоки которых соединены с затворами фиксирующего транзистора 4, стоком второго транзистора 6 выходного каскада и выходом 9 дешифратора,, истоки первого и второго транзисторов 5 и 6 выходного каскада соединены с шиной 11 источника питания и истоками установочного и, фиксирующего транзисторов 3 и 4, затвор установочного транзистора 3 Соединен с тактовой шиной 10 и затвором стробирукндего транзистора 2, исток которого соединен с общей шиной 12, исток третьего транзистора выходного каскада соединен с истока ми транзисторов группы 1, а затвор второго транзистора 6 выходного кас када соединен с тактовой шиной 10. Дешифратор работает следующим об разом. В режиме хранения (статический р жим) на тактовую шину 10 подают потенциал логического нуля. На шине 11 источника питания поддерживают, потенциал логической единицы, а на общей шине 12 - потенциал логичесхого нуля. При этом стробирующий транзистор 2 закрыт, а установочньй транзистор 3 - открыт. В результате независимо от состояния транзисторов группы 1 на стоке Установочного транзистора 3 устанавливается потенцийл логической единицы. При этом первый транзистор 5 выходного каскада оказывается закрытым по затвору, а транзистор 7 - закрытым по истоку. Поскольку потенциал тактовой шины 10 равен логическому нулю, то второй транзистор 6 выходного каскада оказьшается открытым. В результате на выходе 9 дешифратора устанавливается потенциал логической единицы. В режиме выборки информации на тдктовую шину 10 подают потенциал логической единицы, а на всех выходах 8 дешифратора поддерживают потенци- . алы логического нуля. При этом установочный транзистор 3, второй транзистор 6 выходного каскада и все транзисторы группы 1 оказываются закрытыми, а стробирующий транзистор 2 - открытым. В результате потенциал на стоке установочного транзистора 3 остается на прежнем уровне, а потенциал на стоке стробирующего транзистора 2 уменьшается до уровня логического нуля. При этом открывается третий транзистор 7 выходного каскада, ,и потенциал на выходе 9 дешифратора уменьшается до нуля. Фиксирующий транзистор 4 открывается, и потенциал на стоке этого транзистора 4 фиксируется на уровне логической |единицы. В режиме невыборки информации на тактовую шину 10 и хотя бы на один из входов 8 дешифратора подают логический потенциал логической единицы. При йтом открьгоается хотя, бы один из транзисторов группы 1, и уменьшение потенциала на стоке стробирующего транзистора 2 приводит к уменьшению потенциала на стоке установочного транзистора 3. В результате открьтается первый транзистор 5 выходного каскада, и выход ,9 дешифратора оказьшается подключенным к шине 11 питания.

ilr

ill-

11Г-|

Till

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Усилитель считывания на КМДП-транзисторах для статических запоминающих устройств | 1987 |

|

SU1513513A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Дешифратор для запоминающего устройства с резервированием | 1986 |

|

SU1429166A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Усилитель считывания на МДП-транзисторах | 1989 |

|

SU1679547A1 |

ДЕШИФРАТОР HA ЩЦП-ТРАНЗИСТОРАХ, содержащий параллельную группу транзисторов первого типа проводимости, стробируюпщй транзистор первого типа проводимости, установочный транзистор второго типа, проводимости, фиксирующий транзистор второго типа проводимости и выходной каскад, состоящий из первого и второго транзисторов второго тийа -проводимости и третьего транзистора первого типа проводимости, истоки транзисторов параллельной группы соединены со стоком стробирующего транзистора, затворы с соответствующими входами дешифратора, а стоки со стоками установочного и фиксирующего транзисторов и затворами первого и третьего транзиьторов выход 1ого каскада, стоки которых объединены и подключены к затвору фиксирующего транзистора, стоку второго транзистора выходного и выходу дешифратора,истоки первого и второго транзисто ров выходного каскада соединеныс шиной источника питания и истоками установочного и фиксирующего транзисторов, затвор второго транзистора выходного каскада соединен Стак(Л товой шиной и затвором стробируюс щего транзистора, исток которого соединен с общей шиной, отличающийся тем, что, с целью повышения быстродействия, исток третьего транзистора выходного каскада соединен с истоками транзисторов параллельной группы, а затвор установочного транзистора подключен к 00 тактовой шине. о ;о iti

о

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Ohoytna А., а.о | |||

| CMOSHk, Static, RAM., Toshiba Review № 110, | |||

| Jul-Aug, 1977, p | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1985-09-23—Публикация

1983-06-09—Подача