1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных системах nporpaNMHoro управления, имеюьшх кодовые выходы.

Известен интерполятор, построён;ный на двух, охваченных отрицатель-, ной обратной связью, цифровых диАференциальньлх ангшизаторах, каждый из которых состоит из последовательно соединенных накапливаю1цего сумсяатора блока ;;лючей переноса и регистра подынтегральной функции (или счетчика) , причем выход переполнения накапливающего сумматора одного интегратора присоединен ко входу счетчика подынтегральной функции второго и наоборот, причем одна из этих связей подключена к суммирующему входу счетчика , а другая - к вычитающему flj . Недостатком этого интерполятора является сложность программирования цифрового синуса згщанной частоты и низкая точность получения цифровбго синуса заданных различных частот. Наиболее близким к изобретению является интерполятор, содержащий элементы И и ИЛИ, последовательно соединенные первый реверсивный , первый блок ключей и первый накапливающий сумматор, последовательно соединенные первый суглмирующий счетчик, первый формирователь импульсов и первый элемент И, последоватёльно соединенные второй реверсивный счетчик, второй блок ключей и второй накапливакхдий сумматор, а также последовательно соединенные второй суммирующий счетчик, второй форOмирователь импульсов и второй элемент И, выходы первого и второго формирователей импульсов подключены к соответствующим входсШ третьего элемента И, а выход генератора импульсов - ко входу четвертого элемента И 2 .

5

Недостатком такого интерполятора является ТО, что он не пригоден для воспроизведения зависимости R созФ и R sln-Ps том ,ecли необходи0мо обеспечить заданную частоту изменения функции siпЧ и еовФ , а не заданную скорость движения точки с координатами X R cos4 и у - R sin по окружности рёщиуса R. Количество;

5 импульсов аргумента при изменении величины радиуса (амплитуды) R необходимо для интерполяции полного периода синусоиды в интерполяторах, построениях на основе цифровых дифференциальных анализаторов (ЦДЛ),

0

не постоянно и меняется в зависимости от амплитуды а в интерполяторах, построенных на основе оценочной функции, вообще отсутствует связь между координатными перемещениями и аргументом , так как он работает в деKapiroBHX координатах по формуле Л у, т.е. строит зависимости у - f (х). Таким образом, этот интерполятор не позволяет просто и точно генерировать коды цифровых синусов заданных частот.

Цель изобретения - расширение функциональных возможностей интерполятора .

. Цель достигается тем, что в интерполятор введены сумматор, первые триггер и делитель частоты, последовательно соединенные второй триггер и второй делитель частоты, последовательно соединенные третий суммирующий счетчик, дешифратор, шифратор, третий блок ключей, третий накапливающий сумматор и третий триггер, а также последовательно соединенные четвертый суммирующий счетчик, четвертый блок ключей, четвертый накапливающий сумматор и третий делитель частоты, выход которого подключен к первым входам пятого и шестого элементов И, соединенных вторыми входами через первый и второй элементы ИЛИ к соответствующим выходам дешифратора, первый вход третьего элемента ИЛИ соединен с выходом шестого элемента И, второй вход - через первый делитель частоты с выходом пятого элемента И, а выход - через последовательно включенные седьмой элемент И, четвертый элемент ИЛИ, вось«мой элемент И и девятый элемент И со входом четвертого суммирующего счетчика, вход первого триппера под соединен к выходу третьего элемента И, а выход - через восьмой элемент И ко вторым входам первого и второго элементов И, подключенных выходгили ко вторьм входам первого и второго блоков ключей соответственно, выход четвертого элемента И соединен со входом второго триггера, второй вход третьего триггера подключен к выходу второго делителя частоты, а выход к первому входу десятого элемента И, выход которого соединен со вторыми третьего и четвертого блоков ктчиеК, а второй вход - со вторым выходом второго триггера и с первым входом одиннадцатого элемента И, подключенного вторым входом ко второму входу девятого элемента И и ко входу интерполятора, а выходом - ко второму входу четвертого элемента ИЛИ, вход сумматора соединен со входами первого суммирующего и второго реверсивного счетчиков и с выходом первого накапливающего сумматора, а выход второго накапливающего сумматора со входами первого реверсивного и второго суммирующего счетчиков.

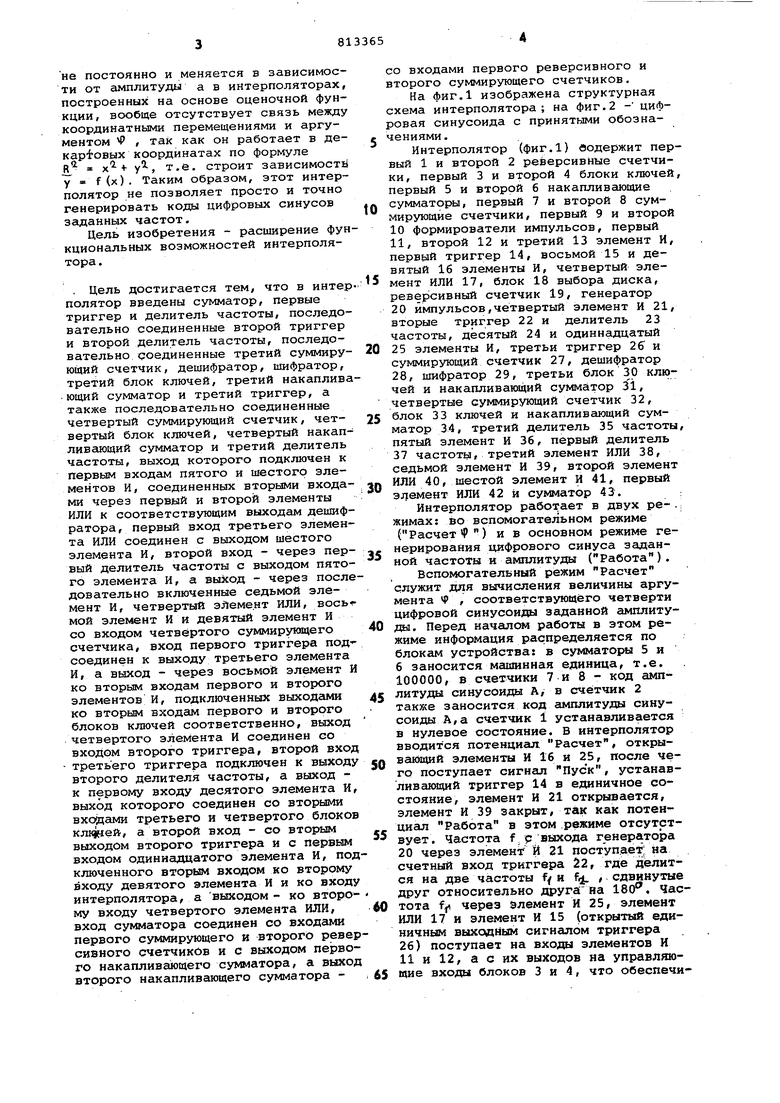

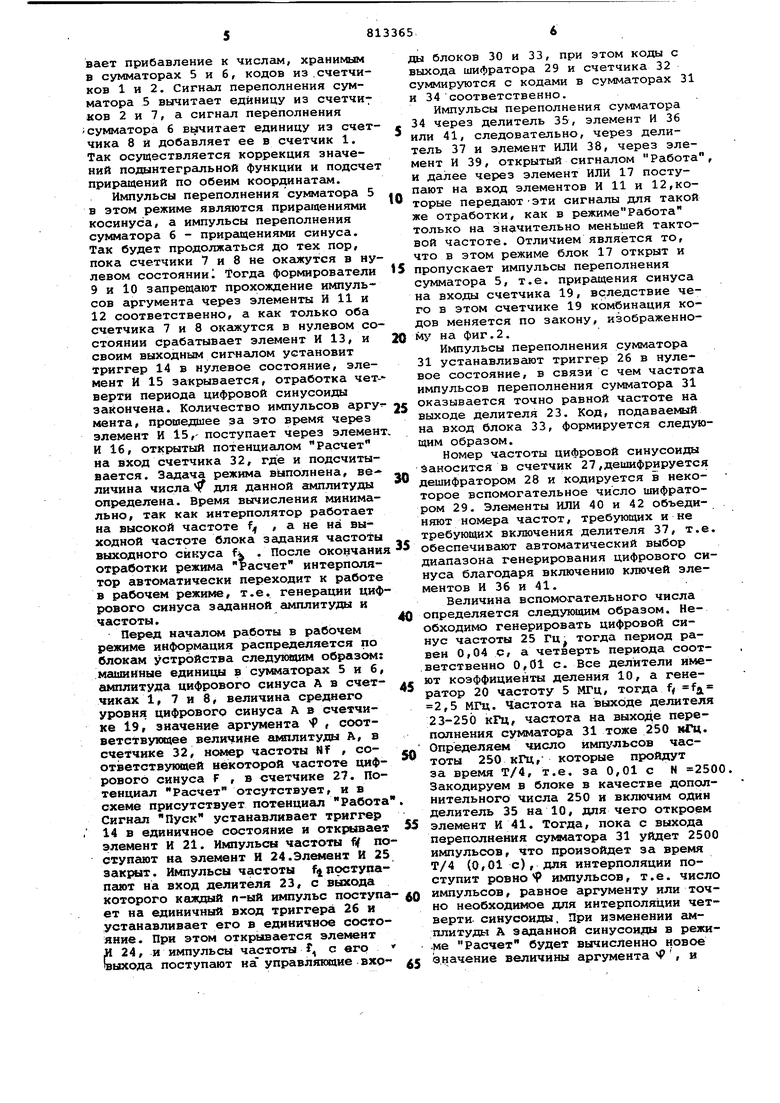

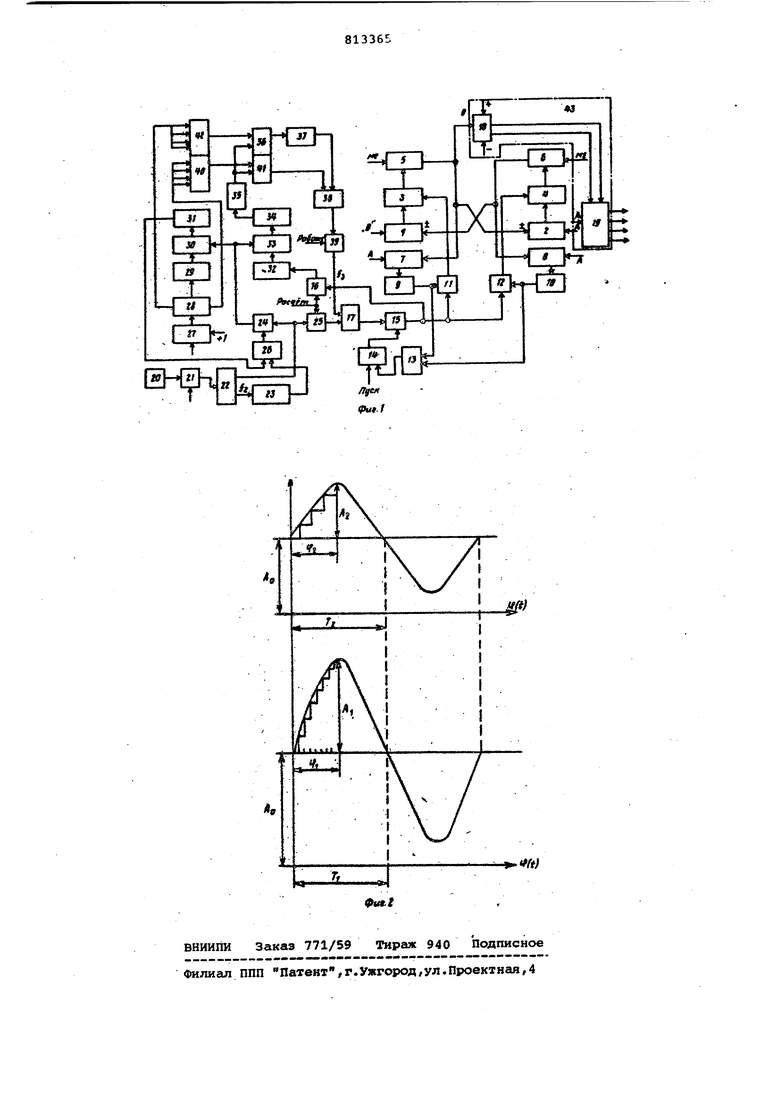

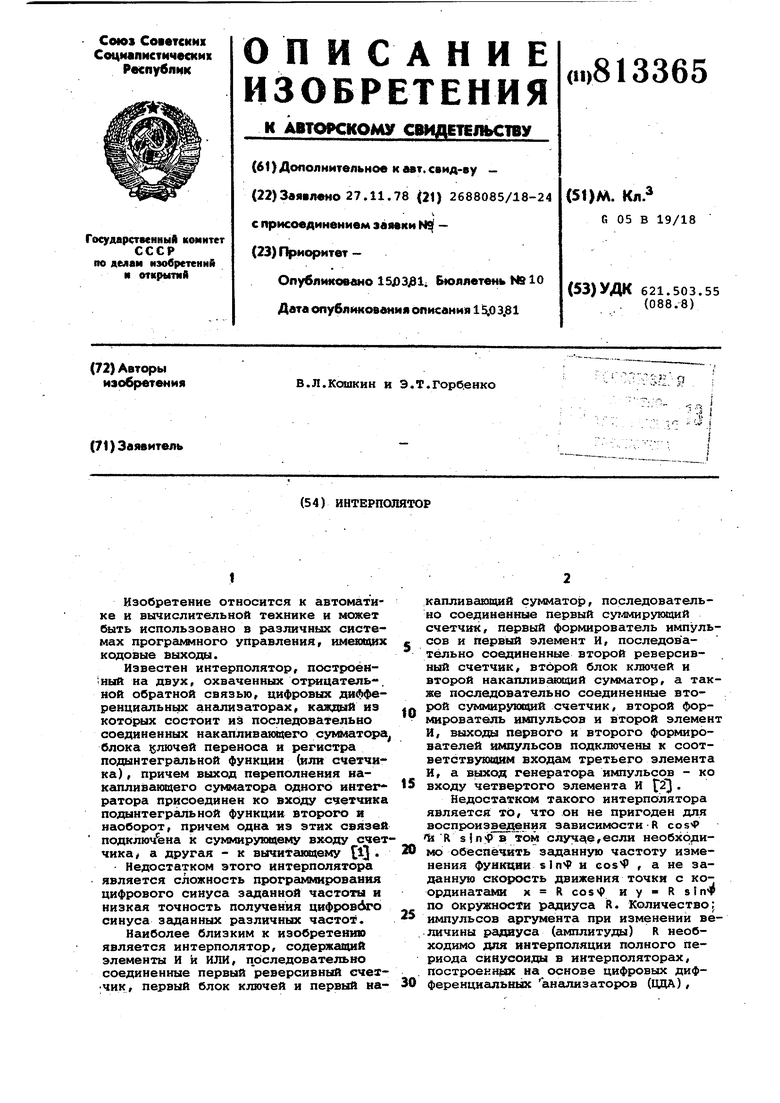

На фиг.1 изображена структурная схема интерполятора; на фиг.2 - цифровая синусоида с принятыми обозначениями.

Интерполятор (фиг.1) «одержит первый 1 и второй 2 реверсивные счетчики, первый 3 и второй 4 блоки ключей первый 5 и второй б накапливающие сумматоры, первый 7 и второй 8 суммирующие счетчики, первый 9 и второй 10 формирователи импульсов, первый 11, второй 12 и третий 13 элемент И первый триггер 14, восьмой 15 и девятый 16 элементы И, четвертый элемент ИЛИ 17, блок 18 выбора диска, реверсивный счетчик 19, генератор 20 импульсов,четвертый элемент И 21 вторые триггер 22 и делитель 23 частоты, десятый 24 и одиннадцатый 25 элементы И, третьи триггер 26 w. суммирующий счетчик 27, дешифратор 28, шифратор 29, третьи блок 30 ключей и накапливающий сумматор 31, четвертые суммирующий счетчик 32, блок 33 ключей и накапливающий сумматор 34, третий делитель 35 частоты пятый элемент И 36, первый делитель 37 частоты, третий элемент ИЛИ 38, седьмой элемент И 39, второй элемент ИЛИ 40, шестой элемент И 41, первый эогемент ИЛИ 42 и сумматор 43.

Интерполятор рабоо ает в двух режимах: во вспомогательном режиме (РасчетФ) и в основном режиме генерирования цифрового синуса заданной частоты и амплитудаг (Работа).

Вспомогательный режим Расчет служит для вычисления величины аргумента Ф , соответствующего четверти цифровой синусоиды заданной амплитуда. Перед началом работы в этом режиме информация распределяется по устройства: в сукйлаторы 5 и 6 заносится машинная единица, т.е. 100000, в счетчики 7 и 8 - код амплитуда синусоиды А, в счётчик 2 такхсе заносится код амплитуда синусоиды А, а счетчик 1 устанавливается в нулевое состояние, в интерполятор вводится потенциал Расчет, открывающий элементы И 16 и 25, после чего поступает сигнгш Пуск, устанавливакиций триггер 14 в единичное состояние, элемент И 21 открывается, элемент И 39 закрыт, так как потенциал Работа в этом режиме отсутствует. Частота f р вьвсода генератора 20 через элемент И 21 поступает: на счетный вход триггера 22, где делится на две частоты f и fij. , сдвинутые друг относительно друга на 18С. Частота ff через элемент И 25, элемент ИЛИ 17 и элемент И 15 (открытый единичным выхсюным сигналом триггера 26) поступает на входы элементов И 11и12, асих выходов на управляющие входы блоков 3 и 4, что обеспечивает прибавление к числам, хранимым в сумматорах 5 и 6, кодов из .счетчиков 1 и 2. Сигнал переполнения сумматора 5 вычитает единицу из счетчи7 ков 2 и 7, а сигнал переполнения ;сумматора 6 вычитает единицу из счет чика 8 и добавляет ее в счетчик 1. Так осуществляется коррекция значений подынтегральной функции и подсче приращений по обеим координатам. Импульсы переполнения сумматора 5 в этом режиме являются приращениями косинуса, а импульсы переполнения сумматора 6 - приращениями синуса. Так будет продолжаться до тех пор, пока счетчики 7 и 8 не окгикутся в ну левом состоянии Тогда формирователи 9 и 10 запрещают прохождение импульсов аргумента через элементы И 11 и 12 соответственно, а как только оба счетчика 7 и 8 окажутся в нулевом со стоянии Срабатывает элемент И 13, и своим выходным сигналом установит триггер 14 в нулевое состояние, элемент И 15 закрывается, отработка четверти периода цифровой синусоиды закончена. Количество импульсов аргу мента, прошедшее за это время через элемент И 15,- поступает через элемен И 16, открытый потенциалом Расчет на вход счетчика 32, где и подсчитывается. Задача режима выполнена, ве личина числа для данной амплитуды определена. Время вычисления минимально, так как интерполятор работает на высокой частоте f , а не на выходной частоте блока задания частоты выходного синуса f . После окончани отработки режима расчет интерполятор автоматически переходит к работе в рабочем режиме, т.е. генерации циф рового синуса заданной амплитуды и частоты. Перед началом работы в рабочем режиме информация распределяется по блокам устройства следующим образом: машинные единицы в сукшаторах 5 и 6, амплитуда цифрового синуса А в счетчиках 1, 7 и 8, величина среднего уровня цифрового синуса А в счетчике 19, значение аргумента , соответствующее величине амплитуды А, в счетчике 32, номер частоты Nf , соответствующей некоторой частоте цифрового синуса F , в счетчике 27. Потенциал Расчет отсутствует, и в Работа схеме присутствует потенциал Сигнал Пуск устанавливает триггер 14 в единичное состояние и отк1%гаает элемент И 21. Импульсы частоты по ступают на элемент И 24.Элемент И 25 закрыт. Импульсы частоты f BOCTynaпают на вход делителя 23, с выхода которого каждый п-ый импульс поступа ет на единичный вход триггера 26 и устанавливает его в единичное состояние. При этом открывается элемент И 24, и импульсы частоты f с его выхода поступают науправляняцие вхо ы блоков 30 и 33, при этом коды с выхода шифратора 29 и счетчика 32 суммируются с кодами в сумматорах 31 и 34 соответственно. Импульсы переполнения сумматора 34 через делитель 35, элемент И 36 или 41, следовательно, через делитель 37 и элемент ИЛИ 38, через элемент И 39, открытый сигналом Работа, и далее через элемент ИЛИ 17 поступают на вход элементов И 11 и 12,которые передаютэти сигналы для такой же отработки, как в режиме Работа только на значительно меньшей тактовой частоте. Отличием является то, что в этом режиме блок 17 открыт и пропускает импульсы переполнения сумматора 5, т.е. приращения синуса на входы счетчика 19, вследствие чего в этом счетчике 19 комбинация кодов меняется по закону, изображенному на фиг.2. Импульсы переполнения сумматора 31 устанавливают триггер 26 в нулевое состояние, в связи с чем частота импульсов переполнения сумматора 31 оказывается точно равной частоте на выходе делителя 23. Код, подаваекий на вход блока 33, формируется следующим образом. Номер частоты цифровой синусоиды Заносится в счетчик 27,дешифрируется дешифратором 28 и кодируется в некоторое вспомогательное число шифратором 29. Элементы ИЛИ 40 и 42 объединяют номера частот, требующих и не требующих включения делителя 37, т.е. обеспечивают автоматический выбор диапазона генерирования цифрового синуса благодаря включению ключей элементов И 36 и 41. Величина вспомогательного числа определяется следующим образом. Необходимо генерировать цифровой синус частоты 25 Гц тогда период равен 0,04 с, а четверть периода соответственно 0,01 с. Все делители имеют коэффициенты деления 10, а генератор 20 частоту 5 МГц, тогда f fa, 2,5 МГц. Частота на выходе делителя 23-250 кГц, частота на выходе переполнения сумматора 31 тоже 250 кГц. Определяем число импульсов частоты 250 кГц, которые пройдут за время Т/4, т.е. за 0,01 с N 2500, Закодируем в блоке в качестве дополнительного числа 250 и включим один делитель 35 на 10, для чего откроем элемент И 41. Тогда, пока с выхода переполнения сумматора 31 уйдет 2500 импульсов, что произойдет за время Т/4 (0,01 с), для интерполяции поступит ровной импульсов, т.е. число импульсов, равное аргументу или точно необходимое для интерполяции четверти синусоиды. При изменении амплитуды А заданной синусоиды в режиме Расчет будет вычисленно новое значение величины аргумента , и вследствие этого частота цифровой синусоида останется без изменений, т.е. AJ A,.,j, так как Ф,, (фиг.2)., . Таким образом, интерполятор обеспёчивает автоматическое поддержание задеГнной частоты при изменении туды цифрового синуса, что в известных интерполяторах не достигается во обще или требует пересчета частоты fj , что неудобно, так как практически рассчитать точно частоту j невозможно. В результате генерируются синусоиды не только отличные по амплитуде, но и ртличные друг от друга по частоте на неучтенную величину, т.е. задача решается не точно, ас большой погрешностью, чт.о недопустимо при управлении конкретными объектами и особенно вредно при использо. вании интерполятора в составе измери тельных стенд Ов, так как это может привести к получению абсолютно неверных результатов. Предлагаемый интерполятор обеспе-i ивает генерирование цифрового синуса любых амплитуд с точностью по амплитуде в пределах одной дискреты и точностью периода в пределах стабиль ности задающего генератора, т.е. величины порядка 10. Формула изобретения Интерполятор, содержащий элементы И и ИЛИ, последовательно соединенные первый реверсивный счетчик, первый блок ключей и первый накапливающий сумматор, последовательно соединенны первый суммирующий счетчик, первый формирователь игшульса и первый элемент И, последо тельно соединенные второй реверсивный счетчик, второй блок ключей и второй накапливающий сумматор, а также последовательно со единенные второй суммирующий счетчик второй формирч:ватель импульсов и вто рой элемент И, выходы первого и второго формирователей импульсов подклю чены к соответствующим входам третье го элемента И, а вьиод генератора им пульсов - ко входу .;;четвертого элемен та И, от л и ча ю и ся тем, что, с целью расширения функциональных возможностей интерполятора, в негх введены сумматор,, первые тригге и делитель частоты, последовательно соединенные второй триггер и второй делитель частоты, последовательно соединенные третий суммирующий счетчик, дешифратор, шифратор, третий блок ключей, третий накапливающий сумматор и третий триггер, а также последовательно соединенные четвертый суммирующий счетчик, четвертый блок ключей, четвертый накапливающий сумматор и третий делитель частоть, выход которого подключен к первым входам пятого и шестого элементов И, соединенных вторыми входами через первый и второй элементы ИЛИ к соответствующим выходам дешифратора4 первый вход третьего элемента ИЛИ соединен с выходом шестого элемента И, второй вход - через первый делитель частоты с выхг.здом пятого элемента И,а выход черех последовательно включенные.седьмой Элемент И, четвертый элемент ИЛИ, восьмой элемент И и девятый элемент И со входом четвертого cyм tиpyющeгo счетчика, вход первого триггера под;соединен к выходу третьего элемента И, а выход - через восьмой элемент И ко вторым входам первого и второго элементов И, подключенных выходс1ми ко вторым входам первого и второго блоков ключей соответственно, выход четвертого элемента И соединен со входом второго триггера, второй вход третьего триггера подключен к выходу второго делителя частоты, а выход к первому входу десятого элемента И, выход которого соединен со вторыми входами третьего и четвертого блоков ключей, а второй вход - со вторым выходом второго триггера И с первым входом одиннадцатого элемента И, подключенного вторым входом ко вторсялу входу девятого элемента И и ко входу интерполятора, а выходом - ко второму входу четвертого элемента ИЛИ, вход сумматора соединен со входами первого суммирующего и второго реверсивного счетчиков и с выходом Первого накапливающего сумматора, а выход второго накапливающего сумматора со входами первого реверсивного и второго суммирующего счеБЧйков. Источники информации, принятые во внимание при экспертизе 1.Кисилев В.М. Фазовые системы . числового программного уйравления. И., Машиностроение, 1976, с.133136. 2.Авторское свидетельство СССР 555381, кл.G 05 В 19/18, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1986 |

|

SU1376065A1 |

| Устройство для измерения угла в системах числового программного управления | 1987 |

|

SU1495749A1 |

| Устройство для коррекции эквидистанты | 1985 |

|

SU1282082A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для задания программы в полярных координатах | 1986 |

|

SU1396125A1 |

| Линейно-круговой интерполятор | 1975 |

|

SU555381A1 |

| Цифровой генератор синусоидальных сигналов | 1983 |

|

SU1193763A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Устройство для воспроизведения полиномов | 1980 |

|

SU930321A1 |

Авторы

Даты

1981-03-15—Публикация

1978-11-27—Подача