1

Изофетение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей в системах автоматического управления при контроле производственных процессов и для измерений при испытаниях аппаратуры.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий Q каскады сзгммируюших блоков и элементы И-НЕ, выходы суммируюигах блоков каж дого.каскада соединеньп с входами суммирующих блоков соседнего старшего каскада, а входы суммирукндих блоков is младшего каскада являкггся информационными входами преобразователя.

Недостаток известного преобразователя состоит в сложности схемы, что выражается в том, гго преобразователь не до- 20 пускает нарапшвания или уменьшения разрядности путем подсоединения (отсоединения) каскадов. При неоСкодимости изменения разрядности, например, с целью

получения более высокой разрядности, всякий раз требуется новая схема,с иными связями. Этот недостаток наиболее ярко проятляется тогда, когда в системе используется значительное количество прюобразователей и при этом с разными коэффициентами масштабирования..

Другим недостатком известного преобразователя является отсутствие входа управления масштабировайием, так как известный преобразователь предназначен для перевода чисел единиц, изображенных в ДВОИЧНОЕ коде, в то же число, единиц, изображенных в двоично-десятич ном коде.

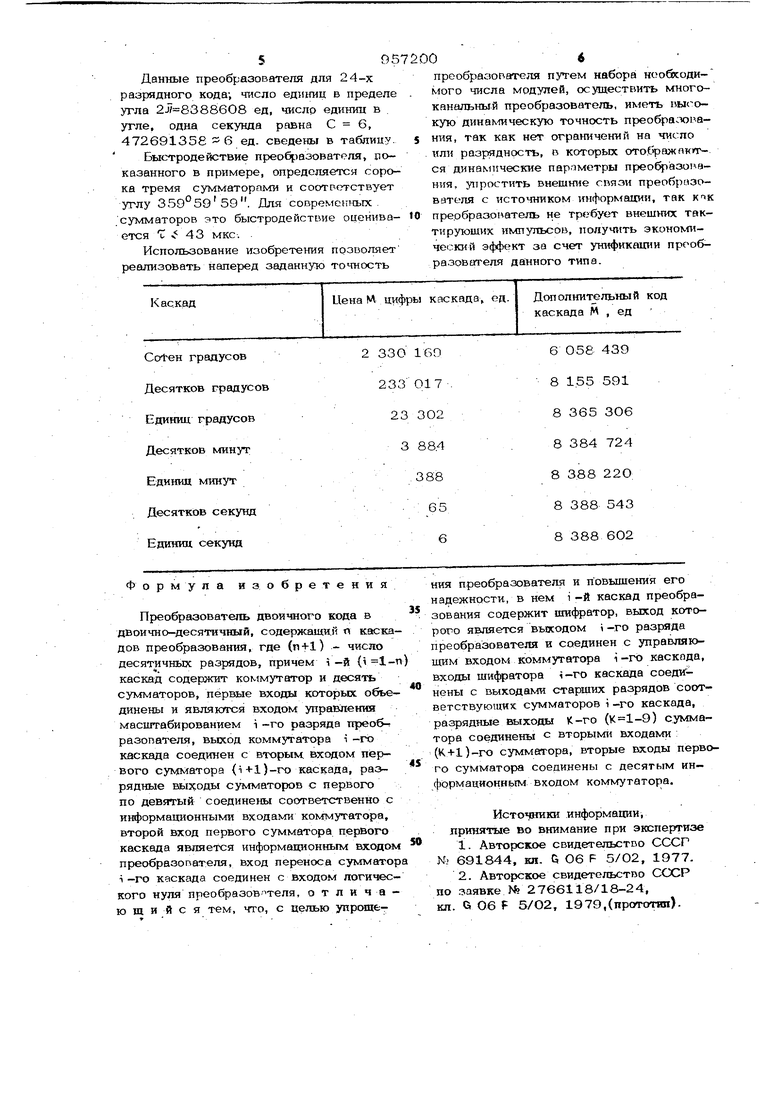

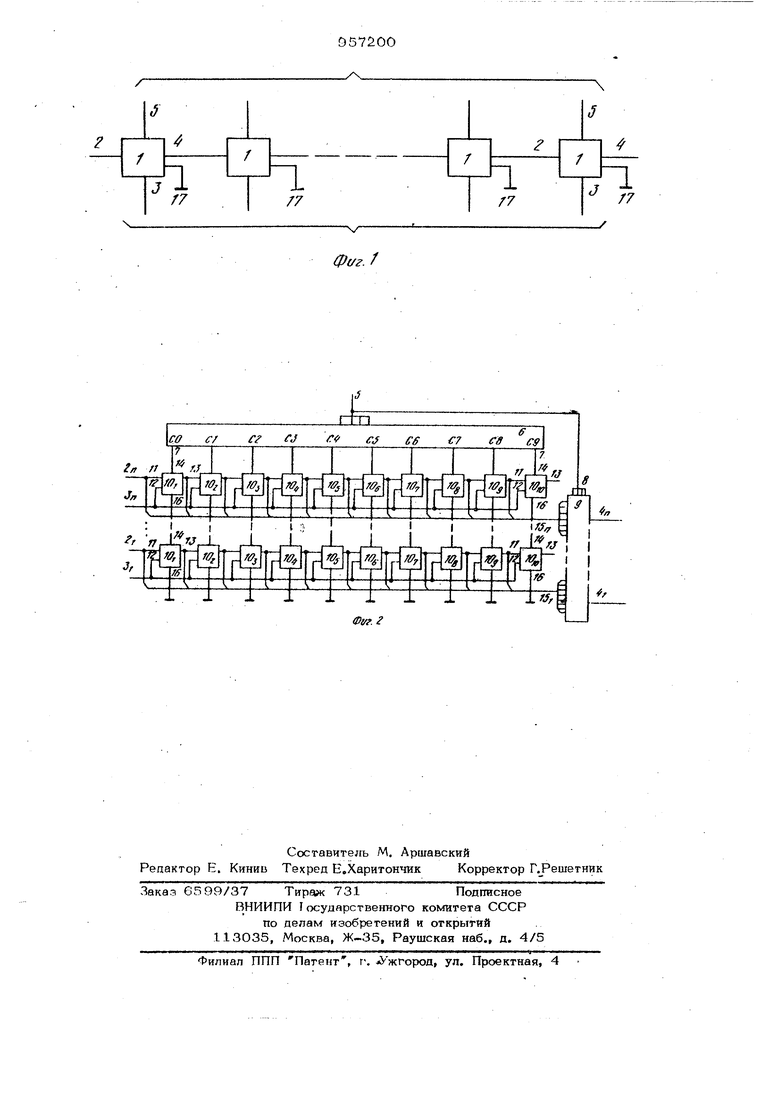

Наиболее близким решением по тех1шческой сущности и схемному построению к предлагаемому является преобразователь двоичного кода в двоично-десятичный, содерисащий последовательно соедкненкые каскады, каждый из которых содерокит десять сумматоров и ко У1мутатор. Кроме того, каждый каскад известног преюбразователя содержит логический блок определения кргайней единицы Г2 . Недостаток данного преобразователя состоит в сравнительно большом объем аппаратуры и низкой надежности. Цель изобретения - упрощение преобразователя и повышение его надежности Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный, содержащий п каскадов преобразования, где (п+1) - оюло десятичных разрядов, причем i -и (i ) каскад содержит коммутатор и десять сумматоров, первые входы котор объединены и ЯВЛЯКУГСЯ входом управления масштабированием -т -го разряда преобразователя, выход коммутатора, i -го каскада соединен с вторым входом первого сумматора (i+1)-го каскада, разрядные втьгходы сумматоров с первого по девятый соединены соответственно с информационными- входами коммутатора, второй вход первого сумматора первого каскада является информационнымвходом преобразователя, вход переноса cyrvi матора i -го каскада ссрдичен с входом логического нуля преобразователя, i -и каскад преобразования содержит щифра- тор, выход которого яышется выходом i-ro разряда преобразователя и сйэединен с управляющим входом коммутатора 1 -го каскада, входы шифратора i -го Каскада соединены с выходами старших разрядов соответствующих сутугматоров i-го каскада, разрядные выходы К -го (К.) сумматора соединены с вторыми входами (К + 1)-го сумматора, вторые входы первого сумтиатора соединены с десятым информационным входом коммутатора. На фиг. 1 приведена блок-схема .пре разователя; на фиг. 2 - блок-схема со динений одного каскада преобразования. Устройство содержит каскад 1 преоб разования, информационный вход 2 каскада, вход 3 управления масштабированием, выход 4 остатка каскада, информапиоин 11е выходы 5 каскада, шиф тор 6, входы 7 шифратора 6, управляющие Входы 8 коммутатора 9, сумматоры , входы 11 и 12 сумматоров, выходы 13 и 1-1 су(маторов, информациошгые входы 15 кочмутатора 9 вход 16 переноса cy rмoтo -oв и вход 17 логического нуля преобразователя. Предлагаемое устройство соде11жит ряд последовательно ,ключенных каскад прообразоватш (см. фиг. 1). Каскпд содержит десять сумматоров. 10 в ряде (разряде) включенных последовательно и пронумерованных от входа в порядке последовательного включения СО-С9, один шифратор 6, входы 7 которого промаркированы в порядке Возрастания также СО-С9, один коммутатор-9, входы 1 5 коп орого промаркированы также СОС9. Входы 12 сумматоров 10 ряда объединены, образуя разряд входа 3 управления масштабированием, выходы 14 с-таршего разряда сумматоров соедине1Пз1 с входами 7 шифратора 6 в порядке одноименной маркировки, входы 15 комк-гутатора 9 подсоединены к входам 11 сумматоров 10 в порядке маркировки, управляющие входы 8 коммутатора 9 подсоединены к выходам 5 шифратора. При преобразоватпга кода, поступившего на вход 2 каскада {см. фиг. 2), на вход 3 должен быть подан двоичный код являющийся дополнительным кодом цены единицы каскада. В этом случае каждый сумматор 10 каскада будет осуществлять операцию вычитания из кода, поданного на вход 2, числа м , соответствующего црне еди-ницы цифры. Рассмотрев операш ю вычитания для всех сумматоров ряда, можно заключить, что на выходе .14 одного из десяти cyjv.fматоров содержится логи--1еский нуль при логической единице на остальных. Логический нуль содерлтатся на том су мвторе 10, на вх.оде 11 которого код меньше цены М единиць. Номер, присвоенный сумматору 1О, у которого) имеется логический нуль, и число вычитаний или значащая цифра каскада совпадают. Положение логического нуля на входах 7 шифратора 6 однозначно определяет код хифры на выходе 5 шифратора 6, который затем поступает на управлякяци-й вход 8 коммутатора 9, что определяет выборку входа 2 II и подключение его к выходу 4 коммутатора и каскада 1 в целом. Остаток на выходе 4 подается на вход 2 следукшего младшего каскада преобразователя для соответствующего анализа кода, поступившего на его вход. ВьЕСод последнего младшего кас1када не используется. Код информации на нем является погрешностью преобразователя, который всегда-меньше цены .единицы самого младшего каскада. В ка-честве примера показан преобразователь двоичного кода и двоично-десятичный код градусов, минут, секунд на 24 двоичных разряда.

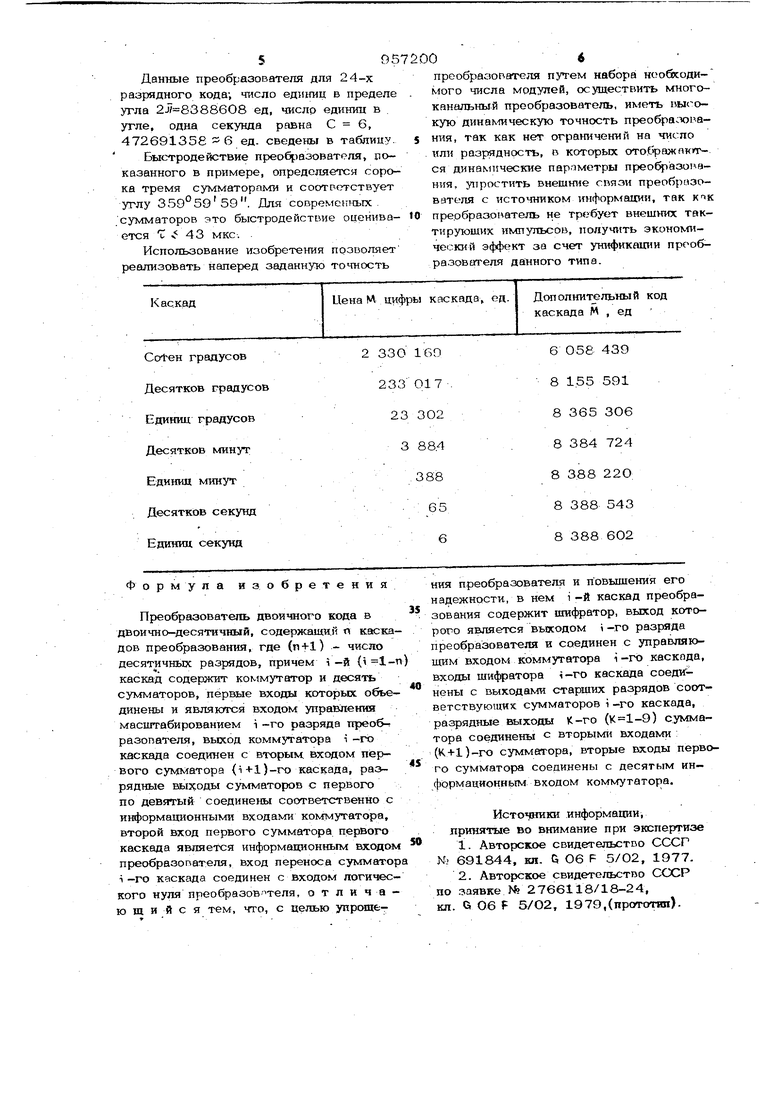

Данные преобразователя для 24-х разрядного кода; число едщшц в пределе угла 2J/ 83886O8 ед, число единиц в угле, одна секунда равна С 6, 472691358 6 ед. сБедень1 в таблицу.

Быстродействие преоб{.)азователя, показанного в примере, определяется сорока тремя сумматорами и соотрсггствует углу 359° 5059. Для современных: . .сумматоров это быстродействие оценивается Т V 43 МКС. .

Использование изобрете1гая позволяет реализовать наперед заданную точность

преобразователя путем набора нообходимого числа модулей, осуществить многоканальный преобразователь, иметь кую динак1ическую точность преобразования, так как нет ограничений на число или разрядность, о которых ото.бражпк1Тся динамические параметры прео азо1 ания, упростить внешние связи преобразователя с источником информации, так К преобразователь не требует тактирующих импульсов, получить экономический эффект за счет унификашш преобразователя данного типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Реверсивный преобразовательдВОичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU849198A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU960794A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

Формула изобретения Преобразователь двоичного кода в двоично-десятичный, содержащи.н л каска дов преобразования, где {nfl) - число десятичных разрядов, причем i-и (i 1каскад содержит коммутатор и десять сумматоров, первые входы которых объе динены и являются входом управления масштабированием i -го разряда прео& разопателя, выход коммутатора т -го каскада соединен с вторым, входом niepвого сум1 атора (i-И)-го каскада, разрядные выходы сумматоров с первого по девятый соединены соответственно с информационными входами коммутатора, второй вход первого сумматора первого каскада является информационным входом преобразователя, вход переноса суммегго i-го каскада соединен с входом логического нуля преобразов теля, отличающийся тем, что, с целью упрощения преобразователя и повышения его надежности, в нем i-и каскад преобразования содержит шифратор, выход которого является выходом i -го разряда преобразователя и соединен с управляющим входом коммутатора i -го каскада, входы шифратора i-ro каскада соединены с выходами старших разрядов соответствующих сумматоров i -го каскада, разрядные выходы К-го () сумматора соединены вторыми входами : (К+1)-го сумматора, вторые входы первого сумматора соединены с десятым ин- формационньгм входом коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 691844, кл. Об F 5/О2, 1977. 2.Авторское свидетельство СССР по .заявке № 2766118/18-24, кл. G Об F 5/О2, 1979,(прототип).

Г7

77

i/г. /

гг (Г/ г/ Л/ |Г л/ се f cff С9

х#

//.

л/

fff

;«7

L-i Г Г - Г Г Г

ТуНт IVlVliY iiV

«

:; Л VJfv

J /7

/7

/

г/

/./

g

/i

lPrir

f

/у

„

IIl fxT

Авторы

Даты

1982-09-07—Публикация

1980-10-20—Подача