(54) МИКРОПРЬГРАМИНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1977 |

|

SU679980A1 |

| Микропрограммное устройство управления | 1972 |

|

SU451080A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| Микропрограммное устройство управления | 1979 |

|

SU881749A1 |

| Перестраиваемое микропрограммноеуСТРОйСТВО упРАВлЕНия | 1979 |

|

SU830383A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

. . - . 1 ,-

Изобретение относится к вычислительной технике и может быть исполь- i эовано в универсальных и специали- зированиых ЦВМ.

По основному авт.св. W 451080 известно ьшкропрограммноё устройство управления, содержащее два запоми наюцих блока, два регистра адреса, два ком «гтатора, две схемы И и два триггера. Причем выход кгикдого KOJWiyтатора соединен с первым входом сосответствуяадего регистра адреса. Первый и второй входы каждого запоминакадего блока соединены с выходами соответствуиадих регистра адреса и схемой. Первые выходы первого и втсфого заполмнаювдих блоков соединекщ с вто1«ми входами второго и jiePtL. вого регистров адреса вторыевыходыпервого и второго запоминающих блоков соединены с входаки второго и первого триггеров. Первые выходы к аждого триггера соединены с первыми входг1ии соответствующих схем И. Вторые дагходы первого и второго регистров адреса соединены с первыми входа11б1 второго я первого коммутаторов. Вторые входы первой и второй сх;ем« И соединены с входами второго и первого коммутаторов. Вторые

входы первого и второго триггеров соедииешл с третьими входами второго, и первого коммутаторов Ч .

Недостатком известного микропрогpaUsftworo устройства является низкое

быстродействие.

Цель изобретения - повышение быстродействия устройства.

Эта цель достигается тем, что в

fU устройство введены задакидий генератор, рЬ1СП Е вделитвль импульсов, счет1{як, два дополнительных коммутатора, два дополиктельжлх элемента И, ИДИ. Инфоркюийонные входы дополtsнительных коммутаторов соединены с соответствующит выходами распреде. литеяя и п1уяьсой, адресные входы с ««ходами счетчика. Шход первого дополнительного 1юи«утатор а соединен 20 со BTptMiM входом первого элемента И и с первый входом первого дополнительного элемента И. Выход второго дополнительного коммутатора соединен с вторым Bxipac второго элемента И и с пер«л« входом второго дополнительног элемента И. Вторые входы первого и второго дополнительных элементов И соединены соответственно с нуЛекмш 11ходами второго и первого

, 30 триггеров. Выходы догголнительных

элементов И соединены с соответствующими входами дополнительного элемента ИЛИ, выход которого соединен с входом счетчика Выход задающего генератора соединен с входом распределителя импульсов,

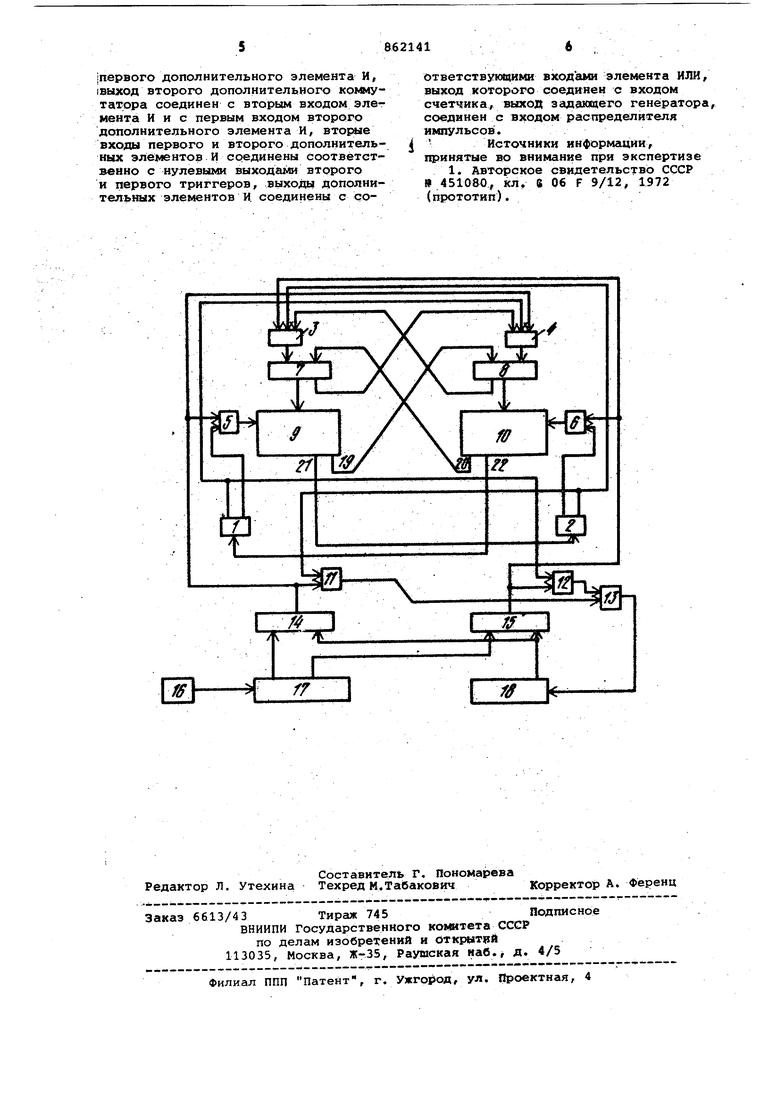

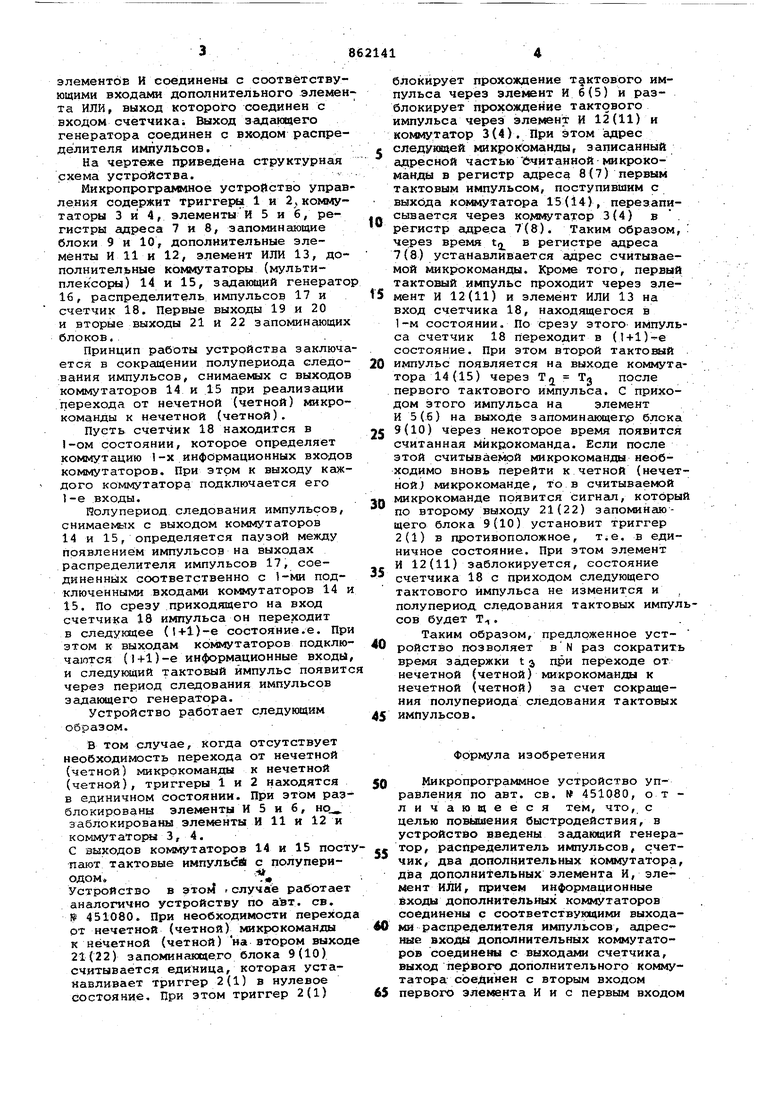

На чертеже приведена структурная схема устройства.

Микропрограммное устройство управления содержит триггеры 1 и 2,коммутаторы 3 и 4, элементы И 5 и 6, регистры адреса 7 и 8, запоминающие блоки 9 и 10, дополнительные элементы И 11 и 12, элемент ИЛИ 13, дополнительные коммутаторы (мультиплексоры) 14 и 15, задающий генерато 16, распределитель импульсов 17 и счетчик 18. Первые выходы 19 и 20 и вторые выходы 21 и 22 запоминающих блоков.

Принцип работы устройства заключается в сокращении полупериода следования импульсов, снимаемых с выходов коммутаторов 14 и 15 при реализации перехода от нечетной (четной) микрокоманды к нечетной (четной).

Пусть счетчик 18 находится в 1-ом состоянии, которое определяет коммутацию 1-х информационных входов коммутаторов. При этом к выходу каждого коммутатора подключается его 1-е входы.

Нолупериод следования импульсов, CHHMaeNfcix с выходом коммутаторов 14 и 15, определяется паузой между появлением импульсов на выходах распределителя импульсов 17, соединенных соответственно с 1-ми подключенными входами коммутаторов 14 и 15. По срезу приходящего на вход счетчика 18 импульса он переходит в следующее (l+D-e состояние .е. При этом к выходам коммутаторов подключаются (1+1)-е информационные входа, и следующий тактовый импульс появитс через период следования импульсов задакицего генератора.

Устройство работает следующим образом.

В том случае, когда отсутствует необходимость перехода от нечетной (четной) микрокоманды к нечетной (четной), триггеры 1 и 2 находятся в единичном состоянии. При этом разблокированы элементы И 5 и б, но заблокированы элементы И 11 и 12 и коммутаторы 3, 4.

С выходов коммутаторов 14 и 15 поступают тактовые импульбй с полупериодом. Устройство в это5| случае работает аналогично устройству по авт. св. № 451080. При необходимости перехода от нечетной (четной) микрокоманды к нечетной (четной) на втором выходе 21(22) запоминающего блока 9(10) считывается единица, которая устанавливает триггер 2(1) в нулевое состояние. При этом триггер 2(1)

блокирует прохождение тактового импульса через элемент И 6(5) и разблокирует прохождение тактового импульса через элемент И 12(11) и коммутатор 3(4). При bтом адрес следукяцей микрок оманды, записанный адресной частью бчитанной микрокоманды в регистр адреса 8(7) первым тактовым импульсом, поступившим с выхода коммутатора 15(14), перезаписывается через ко мутатор 3(4) в .

регистр адреса 7(8). Таким образом, через время t,j в регистре адреса 7(8) устанавливается адрес считываемой микрокоманды. Кроме того, первый тактовый импульс проходит через элемент И 12(11) и элемент ИЛИ 13 на вход счетчика 18, находящегося в 1-м состоянии. По срезу этого иМпульса счетчик 18 Переходит в (1+1)-е состояние. При этом второй тактовый

импульс появляется на выходе коммутатора 14(15) через TQ Tj после первого тактового импульса. С приходом этого импульса на элемент И 5(6) на выходе запоминающег1р блока

9(10) через некоторое время появится считанная микрокоманда. Если после этой считываемой микрокоманды необходимо вновь перейти к четной (нечетной) микрокоманде, то в считываемой

микрокоманде появится сигнал, который по второму выходу 21(22) запоминающего блока 9(10) установит триггер 2(1) в противоположное, . в единичное состояние. При этом элемент

И 12(11) заблокируется, состояние счетчика 18 с приходом следующего тактового импульса не изменится и , полупериод следования тактовых импульсов будет TI.

Таким образом, предложенное устройство позволяет BN раз сократить время задержки 13 при переходе от нечетной (четной) микрокоманды к нечетной (четной) за счет сокращения полупериода следования тактовых

импульсов.

Формула изобретения

Микропрограммное устройство управления по авт. св. 451080, от личающееся тем, что, с целью повышения быстродействия, в устройство введены задающий генератор, распределитель импульсов, счетчик, два дополнительных коммутатора, д)аа дополнительных элемента И, элемент ИЛИ, причем информационные входы дополнительных коммутаторов соединены с соответствующими выходамй распределителя импульсов, адресные входы дополнительных коммутаторов соединены с выходами счетчика, выход первого дополнительного коммутатора соединен с вторым входом

первого элемента И и с первым входом

inepBoro дополнительного элемента И, шыход второго дополнительного коммутатора соединен с вторым входом элемента Икс первым входом второго дополнительного элемента И, вторые входы первого и второго дополнительных элементов И соединены соответственно с нулевыми выходами второго и первого триггеров, выходы дополнительных элементов И. соединены с соответствующими входами элемента ИЛИ, выход которого соединен с входом счетчика, выход задающего генератора соединен с входом распределителя импульсов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-09-07—Публикация

1980-01-09—Подача