I

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах ЦВМ с хранением фиксированной информации, при построении процессов и управляющих вычислительных систем на постоянной памяти, а также в устройствах защиты, шифрования и передачи информации.

Известны постоянные запоминающие устройства (ПЗУ), содержащие входной (адресный) дещифратор, выходы которого соединены с соответствующими входными шинами матричного накопителя, выходной дещифратор (разрядных щин), выходы которого соединены с управляющими входами элементов совпадения и элементов ИЛ1

Недостатком этого устройства является наличие, в нем большого количества входныЯ и разрядных щин, большого количества запоминающих элементов.

Наиболее близким техническим рещением К изобретению является ПЗУ. 2, содержагцре матричный накопитель с 2п запоминающими элементами в каждой строке, разрядными и адресными щинами, при этбм адресные щины соединены с соответствующими выходами первого дешифратора, а

выходы второго дешифратора подключены к первым входам соответствующих 2n. элементов И, выходы которых соединены с соответствующими 2п. входами элемента ИЛИ.

Это устройство содержит большое количество адресных разрядных шин и запоминаюших элементов, каждый из которых хранит только один бит информации. Это приводит к усложнению блоков памяти, увеличению габаритов ЗУ, его стоимости и к снижению надежности работы устройства.

Целью изобретения является повышение информационной емкости и надежности устройства.

Указанная цель достигается тем, что в ПЗУ, содержащем матричный накопитель с 2 ц запоминающими элементами в каждой строке, разрядными и адресными щинами,

15 при этом адресные щины соединены с соответствующими выходами первого дещифратора, а выходы второго дешифратора подключены к первым входам соответствующих 2 п элементов И, выходы которых соединены с соответствующими 2 п входами элемента

20 ИЛИ, информационные входы элементов И соответственно соединены с (n-f 1) разрядными шинами накопителя, начиная с первой.

со сдвигом вправо на одну разрядную шину, а накопитель содержит дополнительные адресные шины, каждая из которых пропуш,ена через вторые TV запоминаюш,их элементов предыдущей строки накопителя и первые 71 запоминаюш,их элементов последующей строки, а дополнительная адресная шина, проходящая через вторые ti. запоминающих элементов последней нечетной строки, проходит через первые И запоминающих элементов первой нечетной строки.

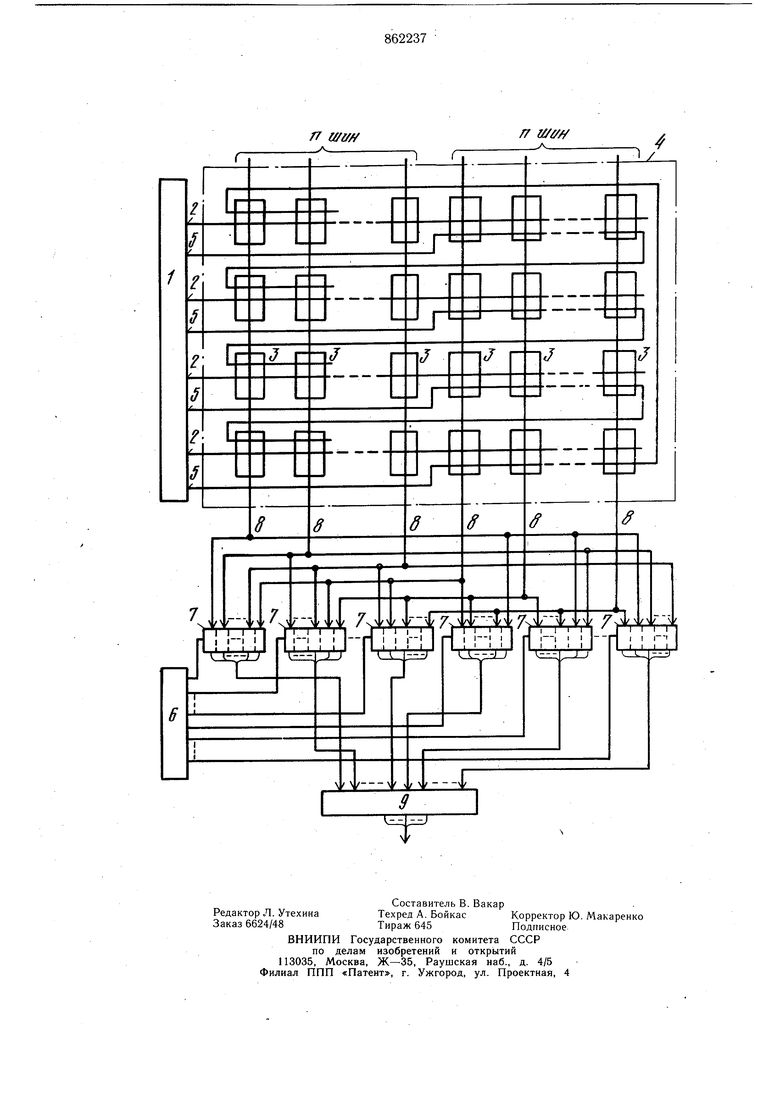

На чертеже представлена схема предлагаемого ПЗУ.

Оно содержит первый дешифратор 1, адресные шины 2, запоминающие элементы 3 накопителя 4, дополнительные адресные щины 5, второй дешифратор 6, элементы И 7, разрядные шины 8 и элемент ИЛИ 9.

Устройство работает следующим образомПервый дешифратор 1 после расшифровки старших разрядов адреса возбуждает соответствующую адресную шину 2 или 5, тем самым выбирается группа сжатых слов. Так как количество запоминающих элементов 3 на каждой адресной шине (четной и нечетной) одинаково, то ширина выборки для каждой из них постоянна. Число выбираемых слов в группе определяется числом разрядных щин 8 накопителя 4 и равно tl. Второй дешифратор б после расшифровки младших разрядов адреса открывает один из элементов И 7 и тем самым выбирает одно из слов группь. При возбуждении соответствующей адресной шины и выборе элемента И 7 считывается определенное (tl + 1) разрядное слово, которое через выбранный элемент И 7 и элемент ИЛИ 9 поступает на выход устройства.

Технико-экономические преимущества предлагаемого устройства заключаются в повышении его надежности за счет уменьшения числа запоминающих элементов в накопителе при хранении в нем одного и того же объема информации. Количество Запоминающих элементов ) накопителя предложенного устройства и прототипа соответственно определяются выражениями: ТП IVГТ7 « V-/7

Так, например, при емкости f 512 9разрядных слов количество запоминающих

элементов в накопителе для предложенного устройства равно 512, а для известного требуется 4608. Количество запоминающих элементов сокращается в п раз. В это же число раз может быть увеличена информационная емкость устройства.

Формула изобретения;

О 1. Постоянное запоминающее устройство, содержащее матричный накопитель с 2п запоминающими элементами в каждой строке, разрядными и адресными щинами, при этом адресные шины соединены с соответствующими выходами первого дешифратора, а выходы второго дешифратора подключены к первым входам соответствующих 2П элементов И, выходы которых соединены с соответствующими 2 п входами элемента ИЛИ, отличающееся тем, что, с целью повышения

0 информационной емкости и надежности устройства, информационные входы элементов И соответственно соединены с (tl-f 1)-разрядными шинами накопителя, начиная с первой, со сдвигом вправо на одну разрядную шину.

2. Устройство по п. 1, отличающееся тем, что накопи.тель содержит дополнительные адресные шины, каждая из которых пропущена через вторые И запоминающих 0 элементов предыдущей строки.наполнителя и первые п запоминающих элементов последующей строки, а дополнительная адресная щина, проходящая через вторые ц запоминающих элементов последней нечетной строки, проходит через первые п запоминающих элементов первой нечетной строки.

Источники информации, принятые во внимание при экспертизе

1.Вопросы радиоэлектроники. Серия «Электронная вычислительная техника, выпуск № 1, 1975, с. 14, рис. 6.

2.Брик Е. А. Техника ПЗУ. «Советское радио, 1973, с. 15, рис. 2.1. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1101896A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746731A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

Авторы

Даты

1981-09-07—Публикация

1980-01-28—Подача