(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕЖНТАРНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1977 |

|

SU703823A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1462300A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

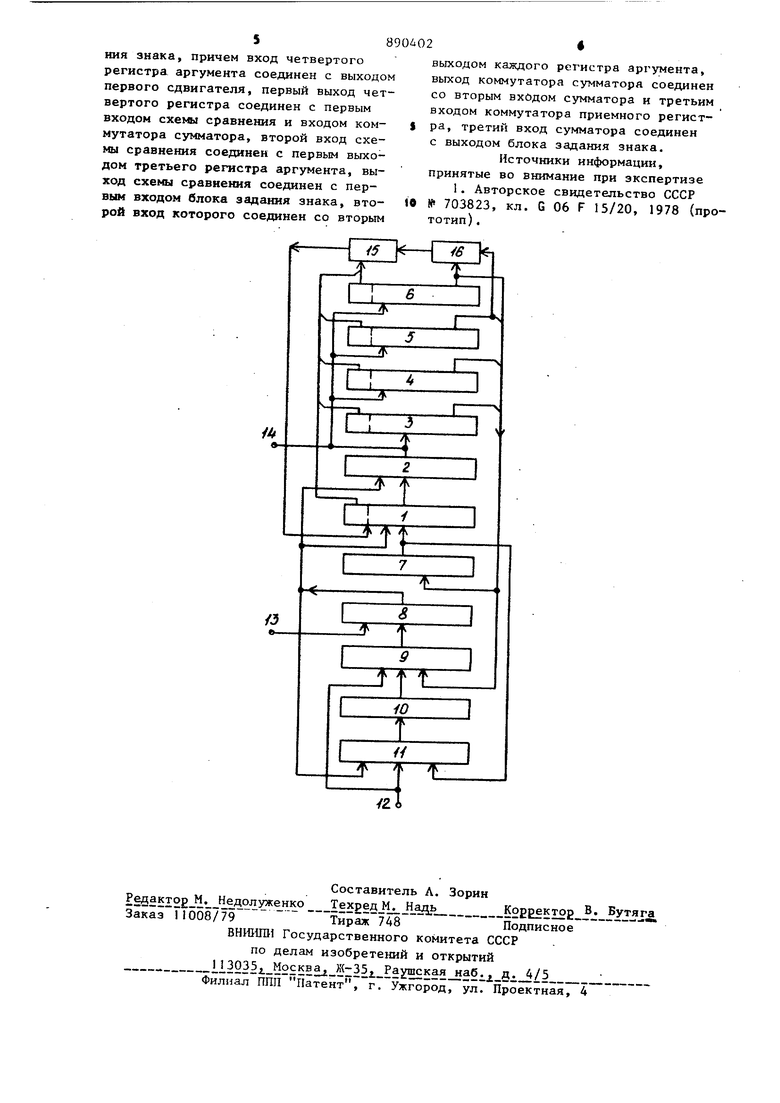

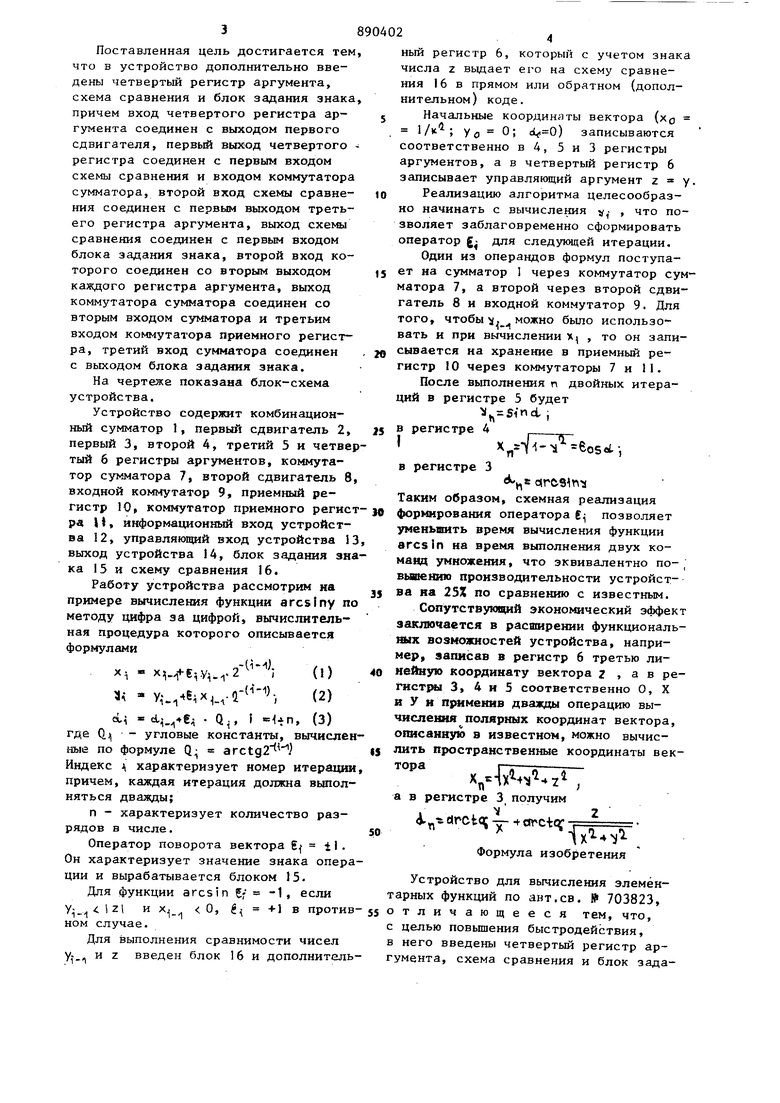

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе цифровой вычис лительной машины. По основному авт.св. № 703823 известно устройство для вычисления элементарных функций, содержащее комбинационный сумматор, соединенный выходом с первым входом первого двигателя, выход которого подключен ко вхо дам регистров и к выходу операционного устройства, причем первые выходы регистра аргументов подключены к первому входу коммутатора буферного регистра и к первому входу входного коммутатора, ко второму входу которого подключен выход приемного регистра соединенного своим, входом с выходом коммутатора приемного регистра, первый вход которого соединен с входом записи информации устройства, с третьим входом входного коммутатора, вход буферного регистра соединен с выходом коммутатора буферного регистpa, а выход буферного регистра соединен t первым входом комбинационного сумматора, второй сдвигатель, соединенный первым входом с выходом входного коммутатора, а выходом - со вторым входом комбинационного сумматора, со вторым входом коммутатора приемного регистра, со вторым входом коммутатора буферного регистра и со вторым входом первого сдвигателя, второй и третий входы второго сдвигателя соединены соответственно с первой н второй управляющими шинами устройства, вторые выходы регистра аргументов и комбинационного сумматора подключены к шине знаковых разрядов устройства, кроме того, выход буферного регистра подключен к третьему входу коммутатора приемного регистра П. Недостатком известного устройства является низкое быстродействие. Целью изобретения является повышение быстродействия. 3 Поставленная цель достигается тем что в устройство дополнительно введены четвертый регистр аргумента, схема сравнения и блок задания знака причем вход четвертого регистра аргумента соединен с выходом первого сдвигателя, первый выход четвертого регистра соединен с первым входом схемы сравнения и входом коммутатора сумматора, второй вход схемы сравнения соединен с первым выходом третьего регистра аргумента, выход сравнения соединен с первым входом блока задания энака, второй вход которого соединен со вторым выходом каждого регистра аргумента, выход коммутатора сумматора соединен со вторым входом сумматора и третьим входом коммутатора приемного регистра, третий вход сумматора соединен с выходом блока задания знака. На чертеже показана блок-схема устройства. Устройство содержит комбинационный сумматор 1, первый сдвигатель 2, первый 3, второй 4, третий 5 и четве тый 6 регистры аргументов, коммутатор сумматора 7, второй сдвигатель 8 входной коммутатор 9, приемный регистр 10, коммутатор приемного регис рд И, информационный вход устройства 12, управляющий вход устройства 1 выход устройства 14, блок задания зн ка 15 и схему сравнения 16. Работу устройства рассмотрим на примере вычисления функции arcslny п методу цифра за цифрой, вычислительная процедура которого описывается формулами х - x,.-f€,y.,. (О 3 yi.,tix.,., (2) « Qi 1 «(п (3) где - угловые константы, вычисле по формуле Q arctg2 } Индекс характеризует номер итераци причем, каждая итерация должна выпол няться дважды; п - характеризует количество разрядов в числе. Оператор поворота вектора g 11 . Он характеризует значение знака опер ции и вырабатывается блоком 15. Для функции arcsin 5- -1, если izl и х О, ii. +1 в проти ном случае. Для выполнения сравнимости чисел у.. и z введен блок 16 и дополнител ный регистр 6, который с учетом знака числа Z выдает его на схему сравнения I6 в прямом или обратном (дополнительном) коде. Начальные координаты вектора (хд УО 0; ) записываются соответственно в 4, 5 и 3 регистры аргументов, а в четвертый регистр 6 записывает управляющий аргумент z у. Реализацию алгоритма целесообразно начинать с вычисления у,. , что позволяет заблаговременно сформировать оператор g для следукицей итерации. Один из операндов формул поступает на сумматор 1 через коммутатор сумматора 7, а второй через второй сдвигатель 8 и входной коммутатор 9. Для Torot чтобы , можно было использовать и при вычислении и , то он записывается на хранение в приемный регистр 10 через коммутаторы 7 и 11. После выполнения п двойных итераций в регистре 5 будет Sindi В регистре 4 I ( , в регистре 3 j,e cirtein-a Таким образом, схемная реализация формирования оператора 6 позволяет уменьоить время вычисления функции arcs In на время выполнения двух комацц умножения, что эквивалентно по-, вывению производительности устройства на 2SZ по сравнению с известным. Сопутствующий экономический эффект заключается в расширении функциональных возможностей устройства, например, записав в регистр 6 третью линейную координату вектора 2 а в регист1 1 3, 4 и 5 соответственно О, X и У и применив дважды операцию вычисления полярных координат вектора, описанную в известном, можно вычислить пространственные координаты векх„.-( а в регистре 3 получим J.oircte;-r:- arciq; Ix Формула изобретения Устройство для вычисления элеменарных функций по ант.св. № 703823, тличающееся тем, что, целью повьппения быстродействия, него введены четвертый регистр арумента, схема сравнения и блок зада58ния знака, причем вход четвертого регистра аргумента соединен с выходом первого сдвигателя, первый выход четвертого регистра соединен с первым входом схеьш сравнения и входом коммутатора сумматора, второй вход схемы сравнения соединен с первым выходом третьего регистра аргумента, выход схемы сравнения соединен с первым входом блока задания знака, второй вход которого соединен со вторым выходом каждого регистра аргумента, выход коммутатора сумматора соединен со вторым входом сумматора и третьим входом коммутатора приемного регистра, третий вход сумматора соединен с выходом блока задания знака. Источники информации. Принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 703823, кл. G 06 F 15/20, 1978 (прототип) .

Авторы

Даты

1981-12-15—Публикация

1979-10-26—Подача