Изобретение относится к вычислительной технике, а именно к системам памяти с модульной структурой и средствами обнаружения многократных ошибок.

Известно запоминающие устройство с обнаружением ошибок, содержаш,ее накопитель из модулей памяти, блоки формирования контрольных разрядов по нечетному модулю и схему выработки ошибки 1.

Недостатком этого устройства является невозможность обнаружения всех многократных ошибок, которые могут возникнуть при отказах многоразрядных модулей памяти.

Наиболее близким к предлагаемому, является запоминающее устройство с автономным контролем, содержащее накопитель, информационные входы которого соединены с входами первого формирователя контрольных разрядов, первого формирователя четности и входами элементов И первой группы, контрольные входы - с выходами первого блока формирователей четности и первого формирователя четности, информационные выходы накопителя подключены к входам второго формирователя контрольных разрядов, элементов И второй группы и второго формирователя четности, контрольные выходы - к одним из входов блока контроля, соединенного с вторым блоком формирователей четноети 2.

Недостатком известного устройства является невозможность обнаружения всех ошибок в пределах пятиразрядных модулей памяти, входящих в накопитель, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением многократных ошибок, содержащее первую группу формирователей контрольных разрядов по нечетному модулю, формирователи четности с первого по третий, первую группу элементов И и накопитель, информационные входы накопителя, входы формирователей контрольных разрядов по нечетному модулю первой группы, одни из входов первого формирователя четности, входы элементов И первой группы являются информационными входами устройства, выход первого формирователя четности соединен с первым контрольным входом накопителя, второй и третий контрольные входы которого соединены соответственно с выходами второго и третьего формирователей четности, другие входы первого формирователя четности и входы первой группы второго формирователя четности подключены к выходам элементов И первой группы, входы второй группы второго формирователя четности и входы третьего формирователя четности соединены с выходами формирователей контрольных разрядов по нечетному модулю первой группы, информационные выходы накопителя являются информационными выходами устройства

и соединены с входами формирователей контрольных разрядов по нечетному модулю второй группы, входами элементов И второй группы и одними из входов четвертого формирователя четности, выходы формирователя контрольных разрядов по нечетному модулю второй группы соединены с входами первой группы пятого формирователя четности и входами шестого формирователя четности, выходы элементов И второй группы подключены к другим входам

5 четвертого формирователя четности и входам второй группы пятого формирователя четности, выходы формирователей четности с четвертого по шестой подключены к одним из входов блока контроля, другие входы которого соединены с контрольными выходами накопителя, а выход является контрольным выходом устройства, введены группы элементов ИЛИ-НЕ, причем входы элементов ИЛИ-НЕ первой группы подключены к информационным входам устройства,

5 а выходы - к входам третьей группы второго формирователя четности, входы элементов ИЛИ-НЕ второй группы соединены с выходами накопителя, а выходы - с входами третьей группы пятого формирователя четности.

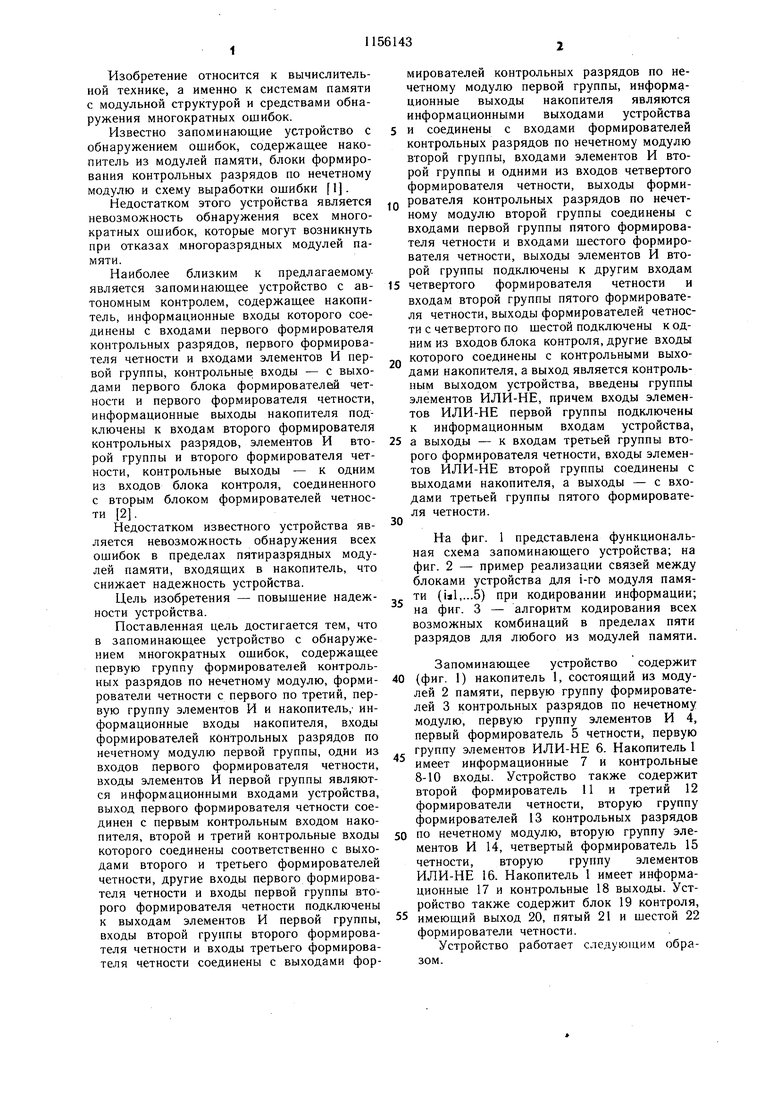

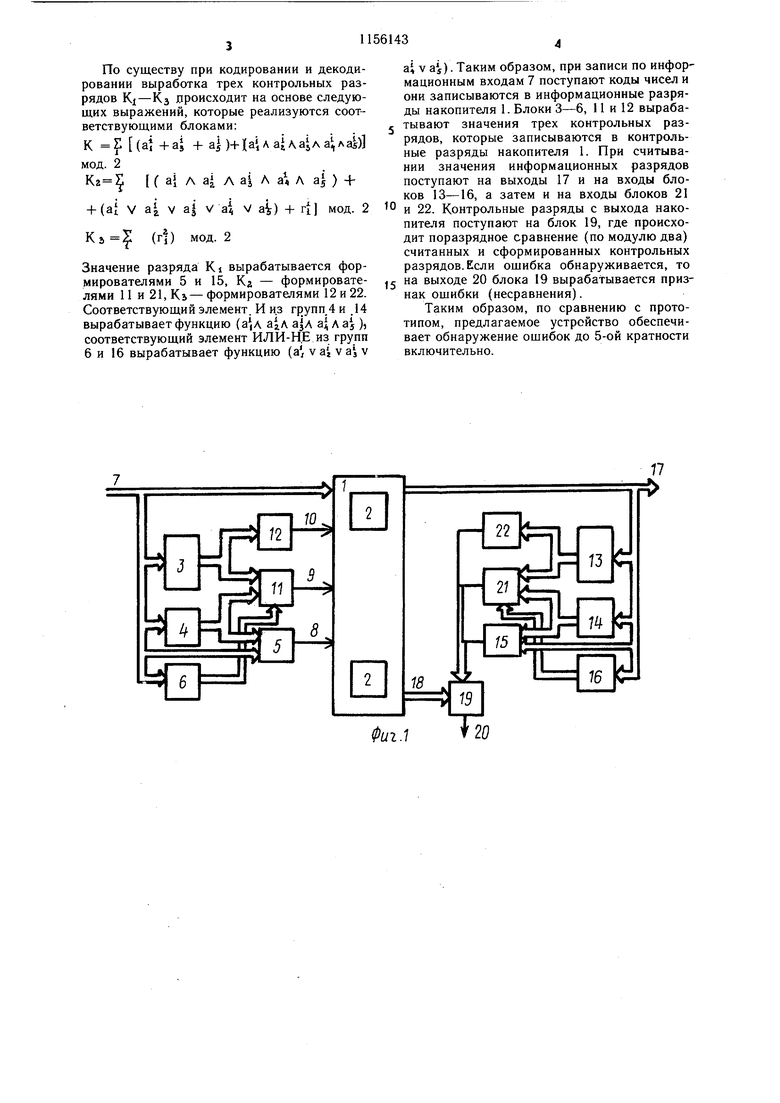

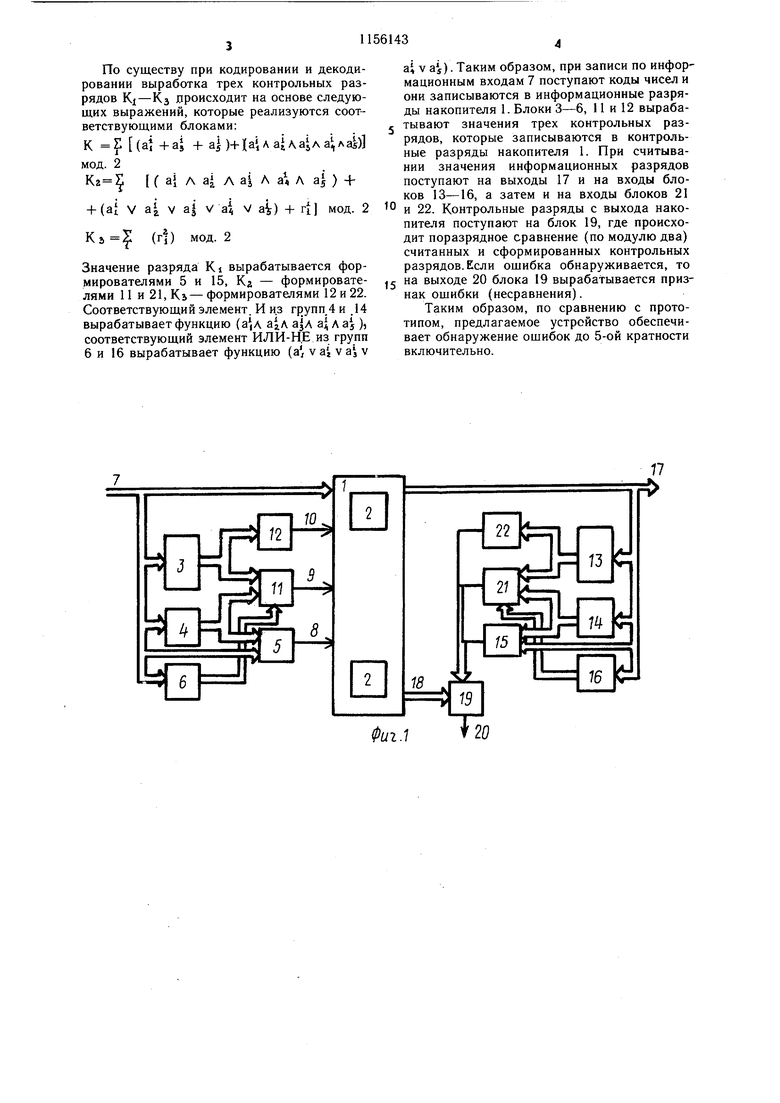

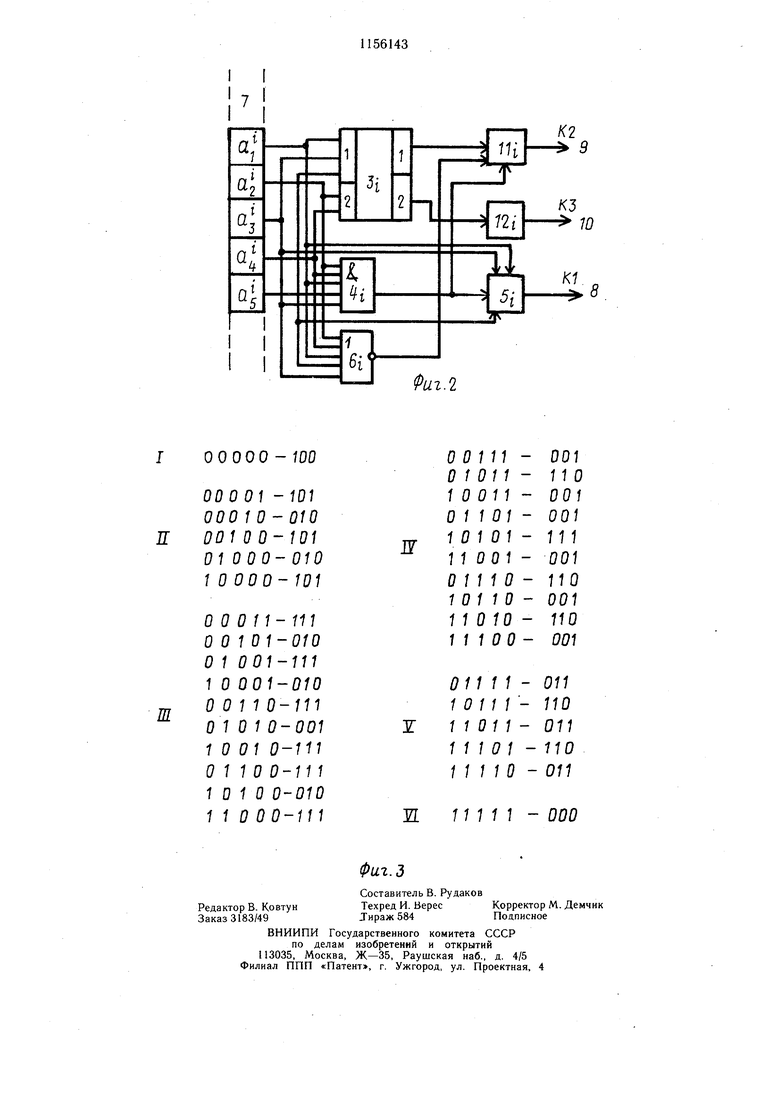

На фиг. 1 представлена функциональная схема запоминающего устройства; на фиг. 2 - пример реализации связей между блоками устройства для i-ro модуля памяти (1з1,...5) при кодировании информации; на фиг. 3 - алгоритм кодирования всех возможных комбинаций в пределах пяти разрядов для любого из модулей памяти.

Запоминающее устройство содержит 0 (фиг. 1) накопитель 1, состоящий из модулей 2 памяти, первую группу формирователей 3 контрольных разрядов по нечетному модулю, первую группу элементов И 4, первый формирователь 5 четности, первую группу элементов ИЛИ-НЕ 6. Накопитель 1 имеет информационные 7 и контрольные 8-10 входы. Устройство также содержит второй формирователь 11 и третий 12 формирователи четности, вторую группу формирователей 13 контрольных разрядов 0 по нечетному модулю, вторую группу элементов И 14, четвертый формирователь 15 четности, вторую группу элементов ИЛИ-НЕ 16. Накопитель 1 имеет информационные 17 и контрольные 18 выходы. Устройство также содержит блок 19 контроля, 5 имеющий выход 20, пятый 21 и шестой 22 формирователи четности.

Устройство работает следующим образом.

По существу при кодировании и декодировании выработка трех контрольных разрядов KI-Кз происходит на основе следующих выражений, которые реализуются соответствующими блоками:

К Е (а +г1 + а} )-f )(ai А al,Aas)j мод. 2 Кг ( а} л а Л ai Л а Л а} ) +

+ (а{ V ai V aj v а v а) + т{ мод. 2 (г) мод. 2

Значение разряда Ki вырабатывается формирователями 5 и 15, Кг - формирователями 11 и 21, KS- формирователями 12 и 22. Соответствующий элемент. И из rpynn.4 и 14 вырабатывает функцию (г а|л а л а ), соответствующий элемент ИЛИ-Н.Е из групп 6 и 16 вырабатывает функцию (а/ v ai v а v

ai V aj). Таким образом, при записи по информационным входам 7 поступают коды чисел и они записываются в информационные разряды накопителя 1. Блоки 3-6, 11 и 12 вырабатывают значения трех контрольных разрядов, которые записываются в контрольные разряды накопителя 1. При считывании значения информационных разрядов поступают на выходы 17 и на входы блоков 13-16, а затем и на входы блоков 21 и 22. Контрольные разряды с выхода накопителя поступают на блок 19, где происходит поразрядное сравнение (по модулю два) считанных и сформированных контрольных разрядов. Если ошибка обнаруживается, то на выходе 20 блока 19 вырабатывается признак ошибки (несравнения).

Таким образом, по сравнению с прототипом, предлагаемое устройство обеспечивает обнаружение ошибок до 5-ой кратности включительно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU894797A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1274004A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХ ОШИБОК, содержащее первую группу формирователей контрольных разрядов по нечетному модулю, формирователи четности с первого по третий, первую группу элементов И и накопитель, информационные входы накопителя, входы формирователей контрольных разрядов по нечетному модулю первой группы, одни из входов первого формирователя четности, входы элементов И первой группы являются информационными входами устройства, выход первого формирователя четности соединен с первым контрольным входом накопителя, второй и третий контрольные входы которого соединены соответственно с выходами второго и третьего формирователей четности, другие входы первого формирователя четности и входы первой группы второго формирователя четности подключены к выходам элементов И первой группы. входы второй группы второго формирователя четности и входы третьего формирователя четности соединены с выходами формирователей контрольных разрядов по нечетному модулю первой группы, информационные выходы накопителя являются информационными выходами устройства и соединены с входами формирователей контрольных разрядов по нечетному модулю второй группы, входами элементов И второй группы и одними из входов четвертого формирователя четности, выходы формирователя контрольных разрядов по нечетному модулю второй группы соединены с входами первой группы пятого формирователя четности и входами шестого формирователя четности, выходы элементов И второй групI пы подключены к другим входам четвертого формирователя четности и входам вто(Л рой группы пятого формирователя четности, выходы формирователей четности с четвертого по шестой подключены к одним из входов блока контроля, другие входы которого соединены с контрольными выходами накопителя, а выход является контрольным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены группы элементов ИЛИ-НЕ, причем входы элементов ИЛИ-НЕ ел первой группы подключены к информационО) ным входам устройства, а выходы - к 1входам третьей группы второго формирова теля четности, входы элементов ИЛИ-НЕ со второй группы соединены с выходами накопителя, а выходы - с входами третьей группы пятого формирователя четности.

I I

7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе СЦВМ | |||

| М., «Мир, 1972, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU894797A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-05-15—Публикация

1982-12-20—Подача