р) |v.

| название | год | авторы | номер документа |

|---|---|---|---|

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

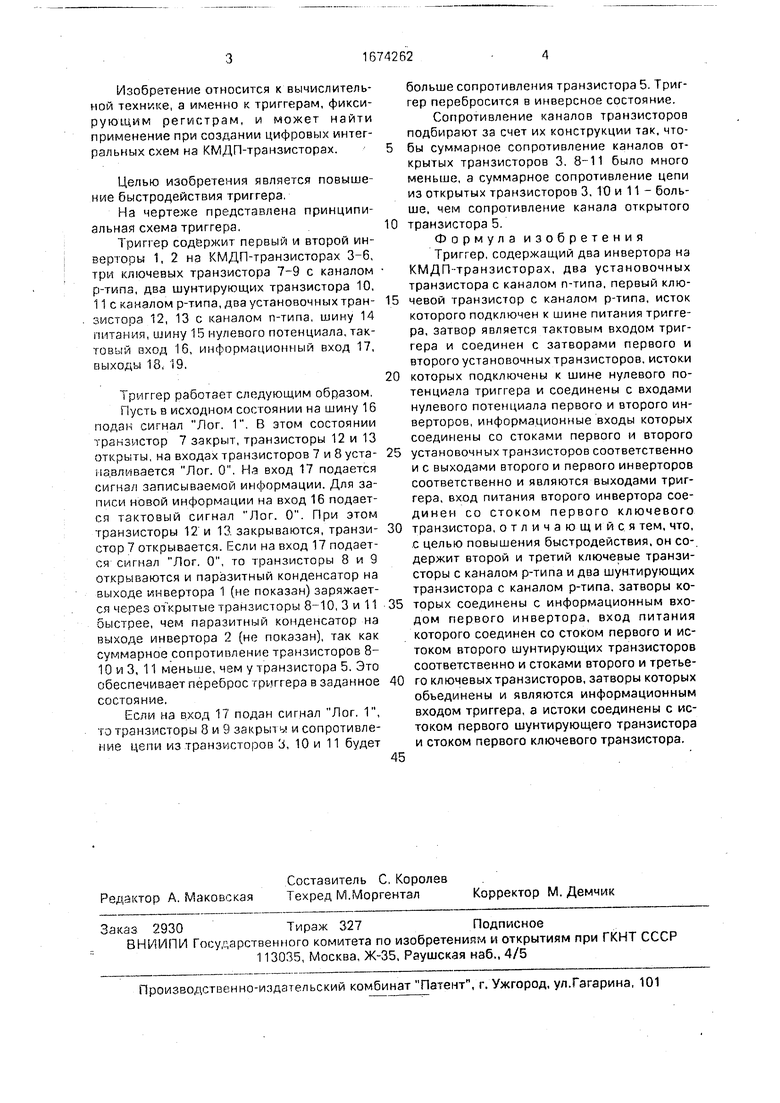

Изобретение относится к вычислительной технике и может быть использовано при создании цифровых интегральных схем на КМДП-транзисторах. Целью изобретения является повышение быстродействия триггера. Поставленная цель достигается за счет того, что триггер содержит второй и третий ключевые транзисторы 8, 9 и первый и второй шунтирующие транзисторы 10, 11 с соответствующими связями. Перезаряд паразитной емкости выхода первого инвертора 1 при лог. "0" на входе 17 будет производиться быстрее, чем на выходе второго инвертора 2, а при лог. "1" на входе 17 - наоборот. Этим обеспечивается запоминание триггером информации, поступившей на вход 17, и ее выдача на выходах 18, 19 без использования опорного входа. 1 ил.

19

ю

Оч

Изобретение относится к вычислительной технике, а именно к триггерам, фиксирующим регистрам, и может найти применение при создании цифровых интегральных схем на КМДП-транзисторах.

Целью изобретения является повышение быстродействия триггера.

На чертеже представлена принципиальная схема триггера.

Трипер содержит первый и второй ин- верюры 1, 2 на КМДП-транзисторах 3-6, три ключевых транзистора 7-9 с каналом р-типз, два шунтирующих транзистора 10, 11 с каналом р-типа, два установочных тран- зистора 12, 13 с каналом n-типа, шину 14 питании, шину 15 нулевого потенциала, тактов1 й оход 16, информационный вход 17, выходы 18, 19.

Триггер работает следующим образом.

Пусть в исходном состоянии на шину 16 подай сигнал Лог. 1. В этом состоянии ранзчстор 7 закрыт, транзисторы 12 и 13 открыты на входах транзисторов 7 и 8 устанавливается Лог. О. На вход 17 подается сигнз 1 записываемой информации. Для записи новой информации на вход 16 подается тактовый сигнал Лог. О При этом транзисторы 12 и 13 закрываются, транзистор 7 открывается. Если на вход 17 подается сигнал Лог. О, то транзисторы 8 и 9 открываются и паразитный конденсатор на выходе инвертора 1 (не показан) заряжается через от крытые транзисторы 8 10, 3 и 11 быстрее, чем паразитный конденсатор на выходе инвертора 2 (не показан), так как суммарное сопротивление транзисторов 8- 10 и 3, 11 меньше, чем у транзистора 5. Это обеспечивает переброс триггера в заданное состояние.

Сели на вход 17 подан сигнал Лог, 1, гj транзисторы 8 и 9 закрыт ы и сопротивление цепи из транзисторов 3, 10 и 11 будет

0

5

0

5

0

5

0

5

больше сопротивления транзистора 5 Триггер перебросится в инверсное состояние.

Сопротивление каналов транзисторов подбирают за счет их конструкции так, чтобы суммарное сопротивление каналов открытых транзисторов 3. 8-11 было много меньше, а суммарное сопротивление цепи из открытых транзисторов 3, 10 и 11 - больше, чем сопротивление канала открытого транзистора 5.

Формула изобретения Триггер, содержащий два инвертора на КМДП-транэисторах, два установочных транзистора с каналом n-типа, первый ключевой транзистор с каналом р-типа, исток которого подключен к шине питания триггера, затвор является тактовым входом триггера и соединен с затворами первого и второго установочных транзисторов, истоки которых подключены к шине нулевого потенциала трипера и соединены с входами нулевого потенциала первого и второго инверторов, информационные входы которых соединены со стоками первого и второго установочных транзисторов соответственно и с выходами второго и первого инверторов соответственно и являются выходами триггера, вход питания второго инвертора соединен со стоком первого ключевого транзистора, отличающийся тем, что, с целью повышения быстродействия, он содержит второй и третий ключевые транзисторы с каналом р-типа и два шунтирующих транзистора с каналом р-типа, затворы которых соединены с информационным входом первого инвертора, вход питания которого соединен со стоком первого и истоком второго шунтирующих транзисторов соответственно и стоками второго и третьего ключевых транзисторов, затворы которых объединены и являются информационным входом триггера, а истоки соединены с истоком первого шунтирующего транзистора и стоком первого ключевого транзистора.

| @ -Триггер | 1984 |

|

SU1174987A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электроника | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1991-08-30—Публикация

1989-10-19—Подача