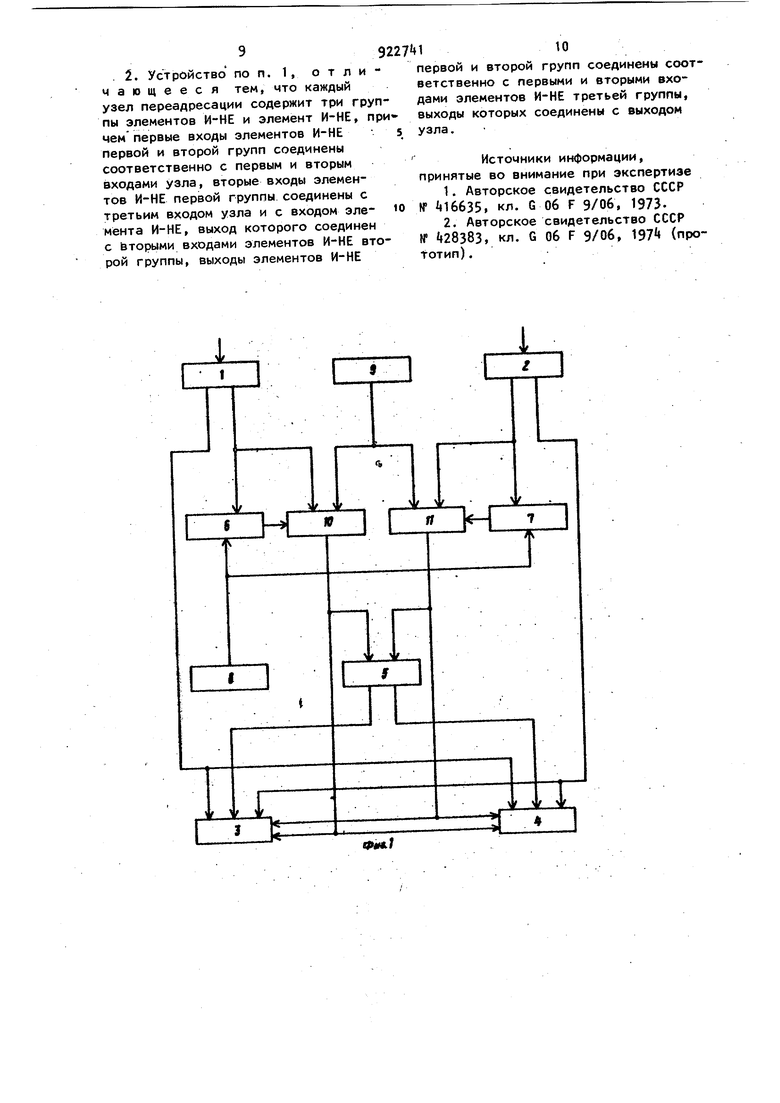

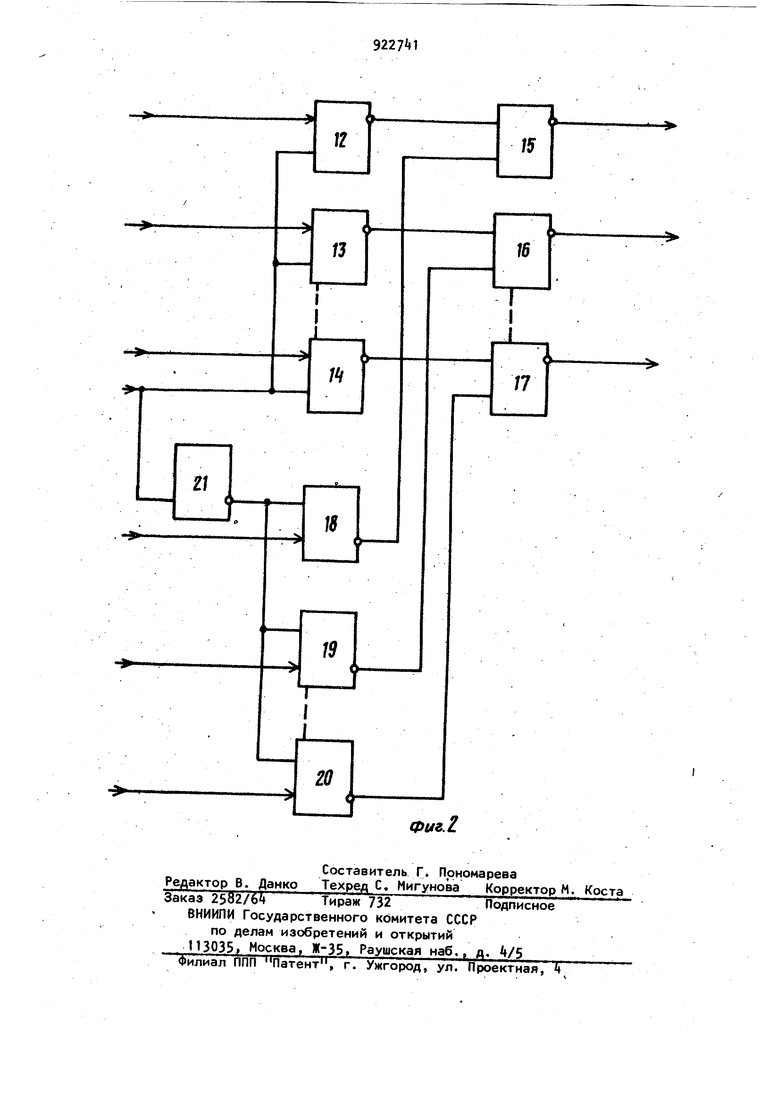

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных системах с. программным управлёй ием.. Известно устройство управления ци ровых вычислительных машин, содержащее счетчик команд и регистр адреса ГП. Однако обращение за командой и за операндом в устройстве происходит по одним и тем же цепям, что ограничивает его логические возможности. Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее счетчик команд, регистр адреса запоминающего устройства, дешифратор, блок памяти, регистр команд и схему сравнения. Функционирование этого устройства в составе управляющей цифровой вычис лительной машины происходит в соответствии с программами, которые хранятся в постоянном запоминающем устройстве 2. Устранение ошибок, обнаруживаемых в процессе первоначальной отладки программ, осуществляют, например, изменением прошивки магнитных сердечников, что является весьма трудоемкой операцией. Кроме того, во время перепрошивки постоянного запоминающего устройства цифровая вычислительная машина не функционирует, что приводит к увеличению времени наладки и ввода машины в эксплуатацию. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для программного управления, содержащее счетчик команд, вход которого является первым входом устройства, первую схему сравнения, два регистра адреса .и дешифратор, введены два регистра зоны, .два узла переадресации, вторая схема сравнения и регистр адреса операнда, причем выход старших разрядов адреса счетчи ка команд соединен -с входами первой схемы сравнения и первого узла переадресации, второй вход которого соединен с выходом первого регистра , первый вход второго узла переадресации соединен с выходом старших разрядов адреса регистра адреса Операнда и с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра зоны и с вторым входом первой схемы сравнения, вторые входы первого и вт рого узлов переадресации соединены с выходом первого регистра зоны, выход первого узла переадресации соединен с первым входом дешифратора, с первыми входами старших разрядов адреса первого и второго регистров адреса, вторые входы старших разрядов адреса- которых соединены с выходом второго узла переадресации и с вторым входом дешифратора, первый и второй выходы которого соединены, соответственно с управляющими входами первого и второго регистров адреса, первые входы младших разрядов адреса которых соединены с выходом младших разрядов адреса счетчика команд, выходы первой и второй схем сравнения соединены соответственно с третьими входами первого и второго узлов переадресации, выход младших разрядов адреса регистра адреса операнда сЬединен с вторыми вхо Дс$(м .младших радрядов адреса первого и второго регистров адреса, вход регистра адреса операнда является втоpbiM входом устройства. Кроме того, каждый узел переадресации содержит три группы элементов И-НЕ и элемент И-НЕ, причем первые входы элементов И-НЕ первой и второй групп соединены соответственно с пер jsm и вторым входами узла, вторые вхсд8 } зламентов Й-НЕ первой группы соединены с третьим входом узла и с х&дом элемента И-НЕ, выход которого соединен с вторыми входами элементов И-НЕ второй группы, выходы элементов И-НЕ первой и второй.групп соединены соответственно с первыми и вторыми входам элементов И-НЕ третьей группы, выходы которых соединены с выходом узла. Предлагаемое устройство позволяет в процессе отладки уп|}авляющей цифровой вычислительной машины при обращении устройства управления за командами и константами в постоянное запоминающее устройство производить замену адресов обращения в постоянное запоминающее устройство адресами обращения в оперативное запоминающее, устройство, в которое предварительно записана отлаживаемая часть программы, тем самым легко проводить корректировку программы, записанной в оперативном запоминающем устройстве. Отладка программы в оперативном запоминающем устройстве позволяет устранить ошибки составления программы непосредственно перед занесением ее в постоянное запоминающее устройство. В результате этого уменьшаются простои вычислительной машины, связанные с корректировкой программ, записанных в постоянном запоминающем устройстве, и, следовательно, сокращаются сроки отладки программ управляющих цифровых вычислительных машин. На фиг. 1 представлена блок-схема устройства для программного управления; на фиг. 2 - блок-схема узла переадресации. Устройство содержит счетчик 1 команд, регистр 2 адреса операнда, первый регистр 3 адреса, второй регистр 4 адреса, дешифратор 5 первую схему 6 сравнения,вторую схему 7 сравнения, второй регистр 8 зоны, первый регистр Э зоны, первый узел 10 переадресации, второй узел 11 переадресации.. Узел 10 переадресации совершенно идентичен узлу 11 переадресации. Узел 10 переадресации состоит из первой группы элементов И-НЕ 12-1, третьей группы элементов И-НЕ . второй группы элементов И-НЕ 18-20 и элемента И-НЕ 21. Узел to переадресации работает следующим образом. При наличии управляющего сигнала на выходе схемы 6 сравнения на вторые входы элементов И-НЕ 12-14 пеовой группы и элемента И-НЕ 21 поступает низкий потенциал, который закрывает эти элементы. При этом с выхода элементов И-НЕ 12-14 первой группы высокий потенциал поступает на первые входы элементов И-НЕ третьейгруппы, а с выхода элемента И-НЕ 21 высокий потенциал поступает на BTopbie входы элементов И-НЕ 18-20 второй группы. В результате значения сигналов на выходах элементов И-НЕ третьей группы однозначно соответствуют значениям сигналов, поступающих с выхода регистра Э на первые входы элементов И-НЕ 18-20 второй группы, проходящих на выход узла 10 переадресации через два последоватёльйо соединенных элемента И-НЕ 18 и 15 19 и 16, 20 и 17 второй и третьей групп. При отсутствии управляющего сигн ла на выходе схемы 6 сравнения на вторые входы элементов И-.НЕ 12-1 i первой группы и вход элемента И-НЕ 21 поступает высокий потенциал. При этом элементы И-НЕ 18-20 второй , группы закрыты низким потенциалом, поступающим на их вторые входы с вы хода элемента И-НЕ 21, и на вторые входы элементов И-НЕ 15-17 третьей группы поступают высокие потенциалы с выхода элементов И-НЕ 18-20 второ группы. В результате значения сигналов на выходах элементов И-НЕ 15 17 третьей группы однозначно соответствуют значениям сигналов группы старших разрядов счетчика 1 команд, поступающих на первые .входы элементов И-НЕ 12-1 первой группы и прох дящих на выход узла 10 переадресаци через два последовательно соединенных элемента И-НЕ 12 и 15, 13 и 16, I и 17 первой и второй групп. Таким образом, в зависимости от значения сигнала на выходе схемы 6 сравнения на выход узла 10 переад ресации проходит группа старших раз рядов адреса команды, либо адрес специальной заиы отладки оперативного запоминающего устройства. Устройство работает следующим об разом.. В исходном состоянии на первый вход устройства с пульта поступает к первой команды программы, а на второй его вход - адрес операнда, учас вующего в операции, В процессе раб ты после выполнения очередной команды в счетчик 1 команд добавляется единица, либо на его вход с ариф метическо-логического устройства ма шины поступает код команды перехода, а на вход регистра 2 поступает адрес операнда, участвующего в очередной операции машины. При работе управляющей цифровой вычислительной машины в режиме отладки программы в регистр 8 записывают адрес той зоны постоянного зап минающего устройства, в которой впоследствии после отладки записывается управляющая программа машины, а в регистр 9 записывают адрес специальной зоны отладки оперативного запоминающего устройства в которой на время отладки записана подлежащая отладке управляющая программа машины. В процессе работы устройства в . первой схеме 6 сравнения происходит поразрядное сравнение адреса зоны постоянного запоминающего устройства, поступающего на второй вход первой схемы 6 сравнения с регистра 8 устройства с группой старших разрядов адреса команды. Причем поступающая на первый вход первой схемы 6 сравнения группа старших разрядов адреса команды представляет собой адрес зоны постоянного запоминающего устройства. При совпадении сравниваемых разрядов на входах первой схемы 6 сравнения на ее выходе формируется управляющий сигнал, который поступает на вход первого узла 10 переадресации. При наличии управляющего сигнала на , входе первого узла 10 пере- . адресации на его выход проходит ад рее специальной зоны отладки оперативного запоминающего устройства, под действием которого дешифратор 5 формирует сигнал управления на своем втором выходе. Под действием этого сигнала управления в регистр I поступает в младшие разряды группа младших разрядов с выхода счетчика 1 команд, а в старшие разряды с выхода первого узла 10 переадресации адрес специальной зоны отладки оперативного запоминающего устройства. Тем самым происходит замена поступающего со счётчика 1 команд истинно-; , го адреса обращения в постоянное запоминающее устройство соответствующим адресам-обращения в специальную зону отладки оперативного запоминающего устройства, в крторой записана подлежащая отладке управляющая программа машины. . В случае не совпадения адресов на входах первой схемы 6 сравнения на ее выходе не формируется управляющий сигнал, и на выход первого 10 переадресации проходит группа старших разрядов адреса команды. .При этом на первом выходе дешифратора 5 формируется сигнал управления, под действием которого в регистр 3 поступает в младшие разряды группа младших разрядов с выхода счетчика 1 команд, а в старшие разряды с выхода первого узла 10 переадресации - группа старших разрядов адреса команды. Тем самым происходит обращение в постоянное запоминающее устройство по истинному адресу, поступающему со счетчика 1 команд. Работа второй схемы 7 сравнения и второго узла 11 переадресации аналогичнй описанной работе первой схем 6сравнения и первого узла 10 переад ресации. Отличие состоит в том, что на второй схеме 7 сравнения происходит поразрядное сравнение поступающи на ее входы адреса зоны постоянного запоминающего устройства с группой старших разрядов адреса операнда. Пр совпадении сравниваемых разрядов на выход второго узла 11 переадресации проходит адрес специальной зоны отла ки оперативного запоминающего устрой ства, и в регистр k в младшие разряд поступает группа младших разрядов с выхода регистра 2, а в старшие разря ды - адрес специальной зоны отладки оперативного запоминающего устройства. Тем самым происходит замена обращения в постояннее запоминающее устройство по адресу из регистра 2 на обращение в специальную зону отладки оперативного запоминающего уст ройства по соответствующему адресу, сформированному в регистре Ц. В случае несовпадения сравниваемых разрядов на входах второй схемы 7сравнения на выход второго узла 11 переадресации проходит группа с-тарших разрядов адреса операнда, и обращение происходит в оперативное запоминающее устройство по истинному адресу, сформированному в регистре l в случае обращения за операндо и в регистре 3 в случае обращения за константой, Применение предлагаемого устройств позволяет в истинных адресах осущест влять отладку программы перед занесением ее в постоянное запоминающее устройство. Благодаря этому существенно упрощается процесс отладки программы и значительно сокращается количество перепрошивок магнитных сердечников постоянного запоминающе го устройства. В результате этого повышается надежность постоянного за поминающего yctpoйcтвa, уменьшаются 9 18 простои машины, связанные с корректировкой программ, и сокращаются сроки отладки программ и срокм ввода в эксплуатацию управляющей цифровой вычислительной машины. Формула изобретения Устройство для программного управления, содержащее счетчик команд, вход которого является первым входом устройства, первую схему сравнения , два регистра адреса и дешифратор, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены два регистра зоны, два узла переадресации, вторая схема сравнения и регистр адреса операнда, причем выход старших разрядов адреса счетчика команд соединен с входами первой схемы сравнения и первого узла переадресации , второй вход которого соединен с выходом первого регистра зонй, первый вход второго узла переадресации соединен с выходом старших разрядов адреса регистра адреса операнда и с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра зоны и с вторым входом первой схемы сравнения, вторые входы первого и второго узлов переадресации соединены с выходом первого регистра зоны, выход первого узла переадресации соединен с первым рходом дешифратора, с первыми входами старших разрядов адреса первого и второго регистров адреса, вторые входы старших разрядов адреса которых соединены с выходом второго узла переадресации и с вторым входом дешифратора, первый и второй выходы которого соединены соответственно с управляющими входами первого и второго регистров адреса, первые входы младших разрядов адреса которых соединены с выходом младших разрядов адреса счетчика команд, выходы первой и второй схем сравнения соединены соответственно с,третьими входами первого и второго узлов переадресации, выход младших разрядов адреса регистра адреса операнда соединен с вторыми входами младших разрядов адреса первого и второго реги- строе адреса, вход регистра адреса операнда является вторым входом устройства. . 2. Устройство по п. 1, отличающееся тем, что каждый узел переадресации содержит три группы элементов И-НЕ и элемент И-НЕ, при чем первые входы элементов И-НЕ первой и второй групп соединены соответственно с первым и вторым входами узла, вторые входы элементов И-НЕ первой группы соединены с третьим входом узла и с входом элемента И-НЕ, выход которого соединен с вторыми входами элементов И-НЕ второй группы, выходы элементов И-НЕ 9 1 первой и второй групп соединены соответственно с первыми и вторыми входами элементов И-НЕ третьей группы, выходы которых соединены с выходом узла. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № «16635, кл. G 06 F 9/06, 1973. 2.Авторское свидетельство СССР № ««28383, кл. G 06 F 9/06, 197 (прототип) .

м

IS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программ | 1985 |

|

SU1280637A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство управления с контролем переходов | 1983 |

|

SU1103238A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

13

/

16

77

Авторы

Даты

1982-04-23—Публикация

1980-02-26—Подача