1

Изобретение огносигся к запоминающим устройствам и может быть использовано шю создания запоминающих уст- ств на МДП-транзисгорах.

Известны усилители считывания дпя запоминаюпшх ус1ройств Щ и 2 .

Один из известных усилителей содержит транзисторы, соединетные по триггерной схеме, и управлякяцие транзисторы, стоки и затворы которых подключе- ю ык соответствующим числовым юинаМ СХ,

Недостатком этого устройства является малое быстродействие.

Из известных устройств наиболее

близким по тезогаческой сущности к хгредлагаемому является усилитель считы1Мнкя для запоминакяцего устройстЕй,; со- держаший транзисторы связи, затворы которых подключены к первой числовое 20 шине, исток соединен со стоксм первого и затвором второго упрешляюших транзисторов, сток второго транзистора связисо второй числовой шиной, исток - со

стоком второго и затвором первого управляющих транзисторов, истоки управляющих транзисторов подключены к разрядным приборам с оптимальными парЕОлеграмн 2J.

Недостатке этого усилителя является нвзкое быстродействие так как напряже ние йри разряде числовой шины, на KOTopofJ формируется уровень логического нуля, ограничивается транзистором связц что снижает быстродействие усилителя.

Цель изобретевня - повышение быстродействия усилителя.

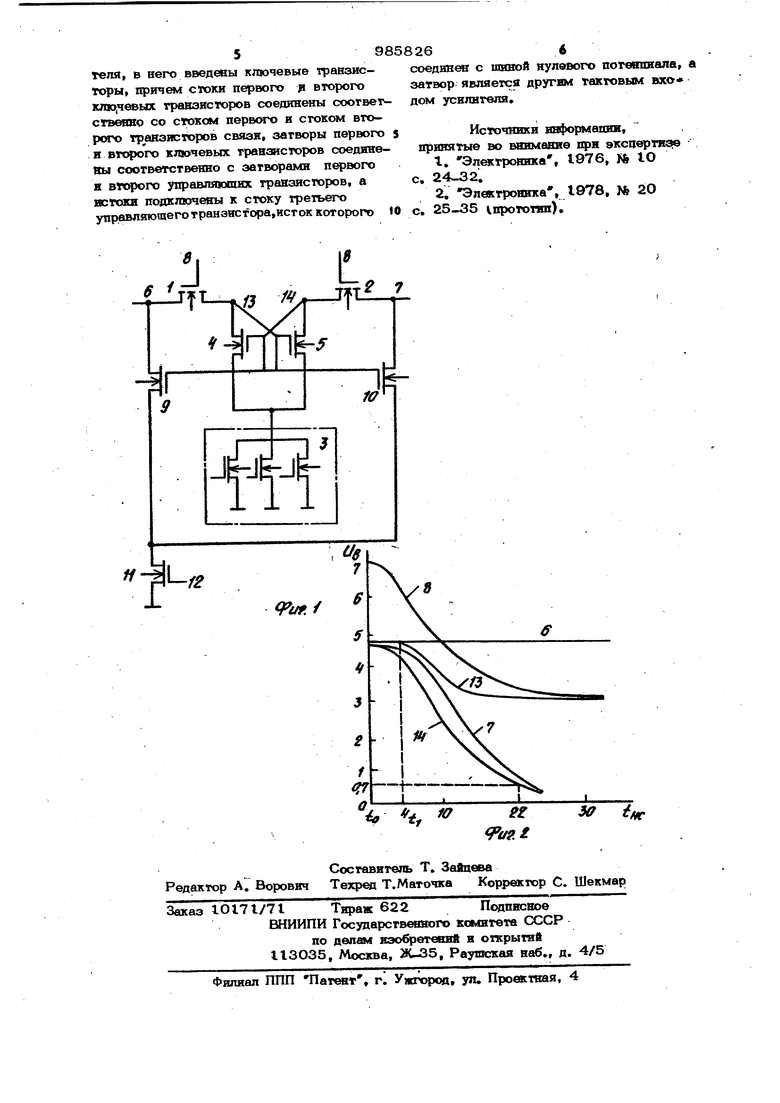

Поставленная цель достигается тем, что в усилитель считывания для запсяиш-. кающетх) устройства, содержащий транзисюры связи в управляющие транзисторы, прячем истоки первого и второго управляющих транзисторов подключены к стокам разрядных транзисторов, исто-: ки которых соедин 1ы с шввой нулевого потенпвала, сток управляющего транзистора подключен к истоку первого транзистсфа свяаи н затвору второго управляющего гранзисгора, сток которого соединен с затвором первого управляющего транзисюра и истоком второго транзистора связи, стоки первого и второго транзисторов связи являются соответственно первым и вторым информационнымн входами усилителя, а затворы являются одними из тактовых входов усюштеля, введены ключевые транзисторы, причем стоки первого и второго ключевьгх транзисторов соединены соответственно с . стоком первого и стоком второго транзисторов связи, затворы первого и второ го ключевых транзисторов соединены соответственно с затворами первого и второго управляющих транзисторов, а истоки подключены к стоку третьего у1фавл5пощего 1ранзистора, исток которо го соединен с шиной нулевого потенциала, а затвор является другим тактовым входом усилителя. На фиг. 1 преде Ставлена пртшипиалъная схема предлагаемого усилителя считывания; на фиг. 2 -временная диаграмма, поясняющая его работу. Предлагаемый усилитель считывания содержит первый 1 и второй 2 транзисторы связи, разрядные ,транзисторы 3, первый 4 и второй 5 управлякипие транзисторы. На фиг. I обозначены первый 6 и второй 7 информационные и одни из тактовых 8 входы усилителя. Усилитель содержит также первый 9 и второй 1О ключевые транзисторы и третий управляющий транзистор И , другой таковый вход 12 усилителя к стоки 13 и 14 соответственно первого и второго управлякядих транзисторов. На фиг. 2 изображены диаграммы напряжений на входах 6 и 7 соответств но, на входах 8, нахфяжений в стоках 13 и 14 в координатах времени . и напряжения (j. , а также обозначены моменты врем am tj, и t , Предлагаемый усилитель считывания работает следукядим образом. До момента времени IQ (фиг. 2) напряжение на выходах 8 высокое, на входе 6 и затворе транзистора 5 равно U а на входе 7 и затворе транше тора 4-( Д). где Д - перепад напряжения, получакяцийся в прпесс доступа в ячейку памяти Напряжение на тактовом входе 12 (фиг, I) равно О, Следовательно,транзис х р Ни гра зисторы 9 и Ю закрыты. С мсмента . ) работают транзи торы 3 (фиг. I). Стоки 14 и 13 разря жаются. Одновременно идет паразитный разряд стока 13 (фиг. I, 2), обусловленный протеканием тчэка через транзистор 4 до тех пор, пока напряжение на епз затворе (в стоке 14) не доргигнет поро.гового значения. Напряжение на Ьходах 8 меняется таким образом, что в процесюе работы усилителя транзистрр I закртт и паразитный разряд через вход 6 отсутствует. Однако уменьшение напряжения на затворах транзисторов I и 2 в свою очередь могло бы ограничить разряд через вход 7 и увеличивать вр&ля формирован11Я да входе 7 уровня логического Нуля, что снижало бы быстродействие усилителя. Это исключается тем, что в момент времени i (фиг. 2) напряжение в стоке 13 (т. е. на затворе транзистора II) в,ысокое и параллельно цети разряда через вход 7 (фиг. 1), транзистор 5 и транзисторы 3 включается цепь из транзисторов Ю и II. Транзистор 9 закрыт, так как на его затворе напряжение ниже -порогового, поэтому отсутствует паразит|Ный разряд через вход 6, а напряжение |на входе 6 высокое, а на входе 7 снижается до нуля.j Таким образом, введение в. усилитель считывания тршсзис Торов 9 и Ю прзволяет повысить его быстродействие. Технико-экономическое преимущеЬтво предлагаетлого усилителя считывания для запоминающего устройства заключается в .его более высоком по сравнению с .прототипом, быстродействии. Формудаизобретения Усилитель считывания для запоминающего устройства, содержащий транзисторы связи и управляющие транзисторы, причем истоки первого и второго управлякядих транзисторов подключены к стокам разрядных транзисторов, истоки которых соединены с шиной нулевого no-i тешщала, сток первого управлякяцего транзистора подключен к истоку первого 1ранзистора связи и затвору второго управляющего транзистора, сток которого соедикш с затвором первого управляющего транзистора и истоком второго транзистора связи стоки первого и второго траазйс1х ров связи яьляются соответственно первым и вторым инфорШционными входами усилителя, а затворы явл51ются одними из тактовых входов усилителя, отличающийся тем, что, с целью повышения быстродействия усилитепя, в него введены ключевые транзисторы, причем сгокя первого д второго кл|а1чевых транзисторов соединены соотве ствевко со стоком первого в стоком второго TpjaHSHCTopoB связи, затворы первого н второго ключевых транзисторов соединеВы соответственно с затворами первого я второго управляющих транзнсгоров, а истоки подключены к стоку третьего управляющего трананстора.исток которого

соединен с шиной нулевого потешшала, а затвор является другим тактовым вхо дом усилителя.

Источники ияформапии, принятые во внимание при экспертною г. Электроника, 1976, « Ю с. 24-32.

2. Электроника, 1078. N 20 с, 25-35 прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1980 |

|

SU938316A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1977 |

|

SU708417A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания | 1980 |

|

SU951390A1 |

Авторы

Даты

1982-12-30—Публикация

1981-07-16—Подача