Изобретение относится к запоминающим устройствам техники и может быт использовано при создании оперативных запоминающих устройств (ОЗУ) большой емкости. Известно ОЗУ, содержащее накопиЧ;ель емкостью слов и блок адресации, включающий регистр адреса на число р рядов, соответствующее данному п Дальнейшее увеличение емкости ОЗУ желательное в точки зрения пользователей, при постоя 1ной длине слова при водит к необходи11юсти соответствующего увеличения числа разрядов в регистре сцфеса. Однако это не всегда, представляется возможным ввиду того, что -операционная система ЭВМ, использующей данное ОЗУ, существенно учитывает .принятую в данной серии ЭВ разрядность адреса.. Наиболее близким техническим ре.шением к изобретению является оперативное запоминающее устройстве, состоящее из четырех независимых блоков .памяти, входного регистра адреса и дешифратора, причем каждый блок памяти содержит накопитель, регистр, вводимой и выводимой информации, регистр адреса, схему коммутации записываемого и считываемого числа, адресную схему совпадения и имеет информационные входы и выходы, адресные входы, вход выборки блока и два входа признаков считывания и записи информационные входы и выходы каждого блока памяти подключены к внешней числовой магистрали, вход выборки соединен с соответствующим выходом дешифратора, а входы признаков считывания и записи объединены с одноименными входами остальных блоков памяти и подключены соответственно к внешнему входу признака считывания и внешнему входу признака записи; адресные входы всех блоков памяти поразрядно объединены и связаны с выходами соответствующих старших и средних разрядов входного регистра адреса, имеющего внешние адресные входы, входы дешифратора подключены к выходам двух младших разрядов входного регистра адреса l2j. Общая емкость этого ОЗУ и разрядность его входного регистра адреса полностью соответствуют друг другу, т.е. дальнейшее увеличение емкости ОЗУ (при той же разрядное ти слова) невозможно без введения дополнительных разрядов в поле адреса команд. Это является основным

препятствием для наращивания емкости ОЗУ, так как требует серьезной и дорогостоящей корректировки сложившегося математического обеспечения ЭВМ.Кроме того, эта корректировка привела бы к нарушению программной совместимости в иерархии моделей ЭВМ,

Целью изобретения является повыше ние информационной емкости ОЗУ, минимально затрагивающее математическое обеспечение ЭВМ,

Поставленная цель достигается тем что в оперативное запоминающее устройство, содержащее блоки памяти, регистр адреса и дешифратор, причем информационные входы и выходы блоков псмяти являются одними из информационньах входов и информационными выходами устройства, входы выборки блоков памяти подключены к выходам дешифратора, управляющие входЬт блоков памяти объединены и являются одними из управляющих входов устройства,-а одни из адресньлх входов подключены к одним из входов регистра адреса, введены элемент И, регистр номера логического блока памяти и блок корректировки адреса, причем первые и вторые входы элемента И и регистра номера логического блока памяти являются соответственно другими информационными и управляющими входами устройства, входы блока корректировки адреса подключены соответственно к другим выходам регистра адреса и выходам регистра номера логического блока памяти, управляющий вход которого соединен с выходом элемента И,.выходы блока корректировки адреса подключены соответственно-к входам дешифратора и другим адресным входам блоков памяти-

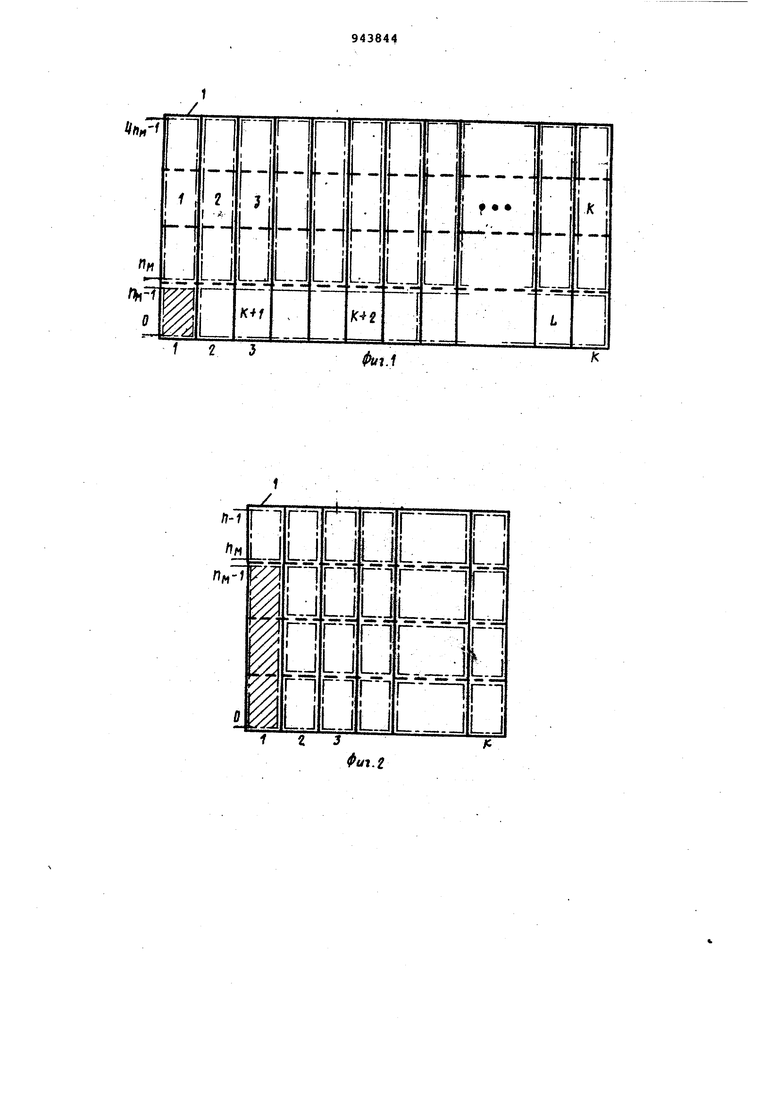

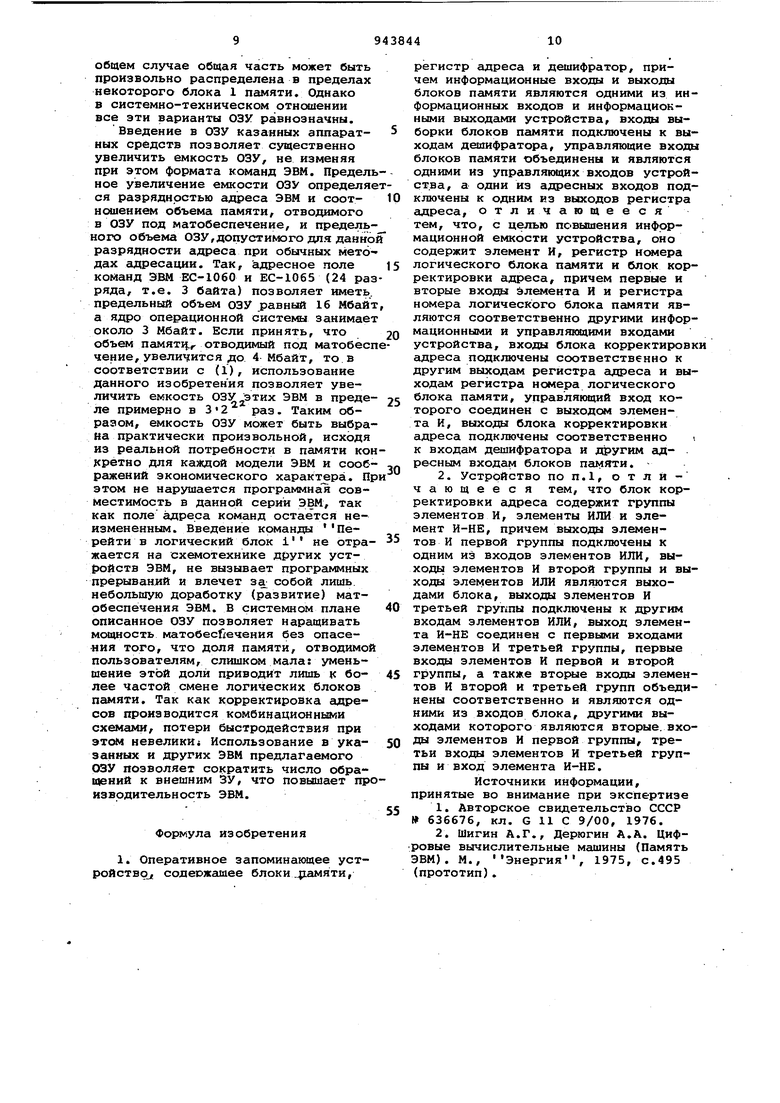

При этом блок корректировки адреса целесообразно выполнить в виде блока, содержащего группы элементов И, элементы ИЛИ и элемент И-НЕ, причем выходы элементов И первой группы подключены к одним из входов элементов 1ЛИ, выходы элементов И второй группы и ВЫХОДИ элементов ИЛИ являются выходами блока, выходы элементов И третьей группы подключены к другим входам элементов ИЛИ, выход элемента И-НЕ соедине с первыми входами элементов И третье группы, первы е входы элементов И пер вой и второй группы, а также вторые входы элементов И второй и третьей групп объединены соответственно и являются одними из входов блока, другими входами KOTopo.ro являются вторые входы элементов И первой группы, третьи входы элементов И третьей группы и вход элемента И-НЕ.

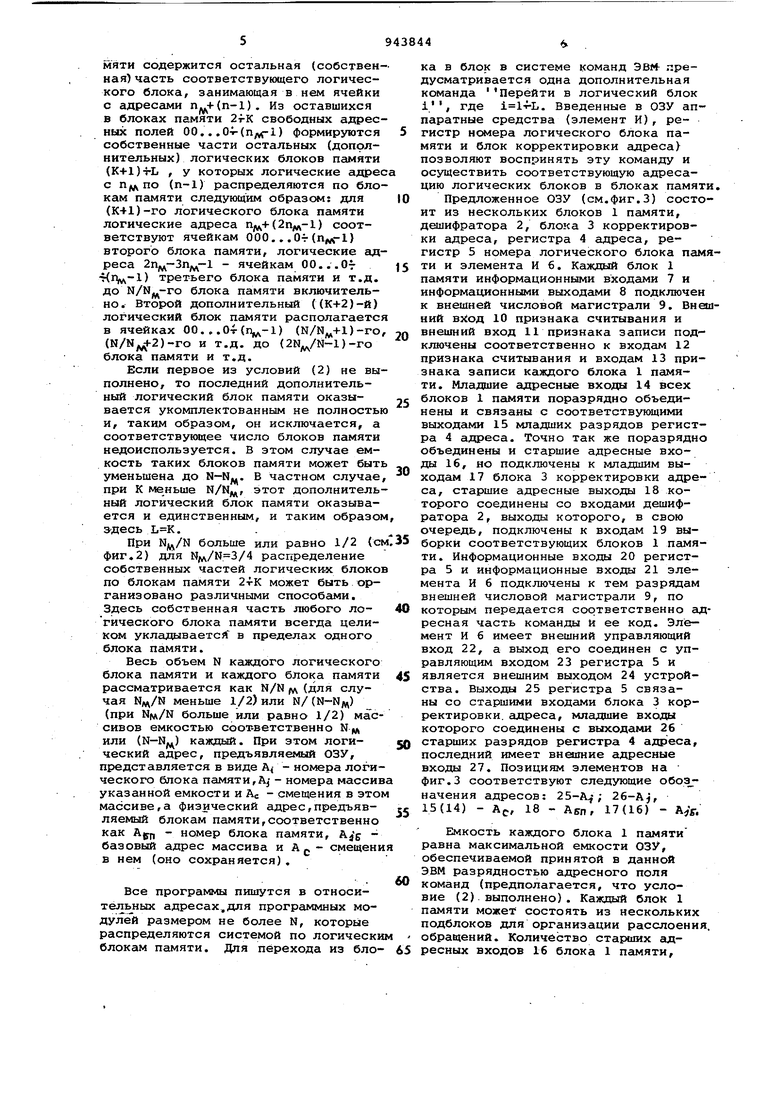

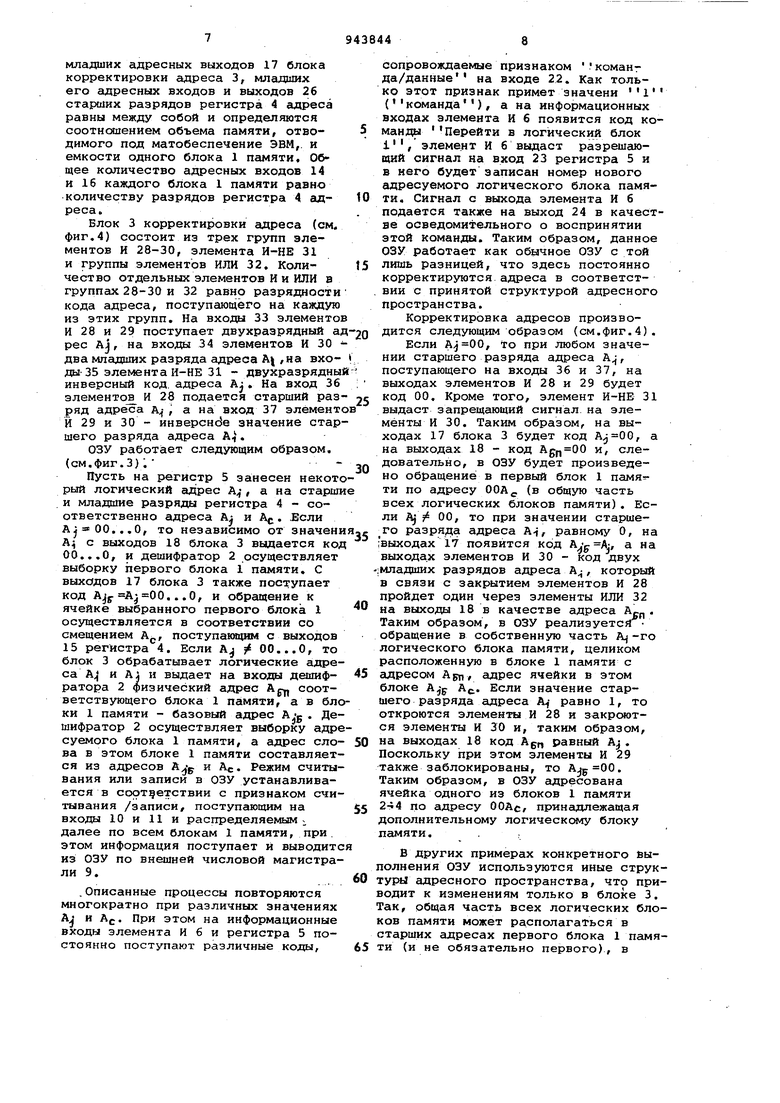

На-фиг. и 2 представлена структура адресного пространства ОЗУ для

«м/«

случаев соответственно

I

VN

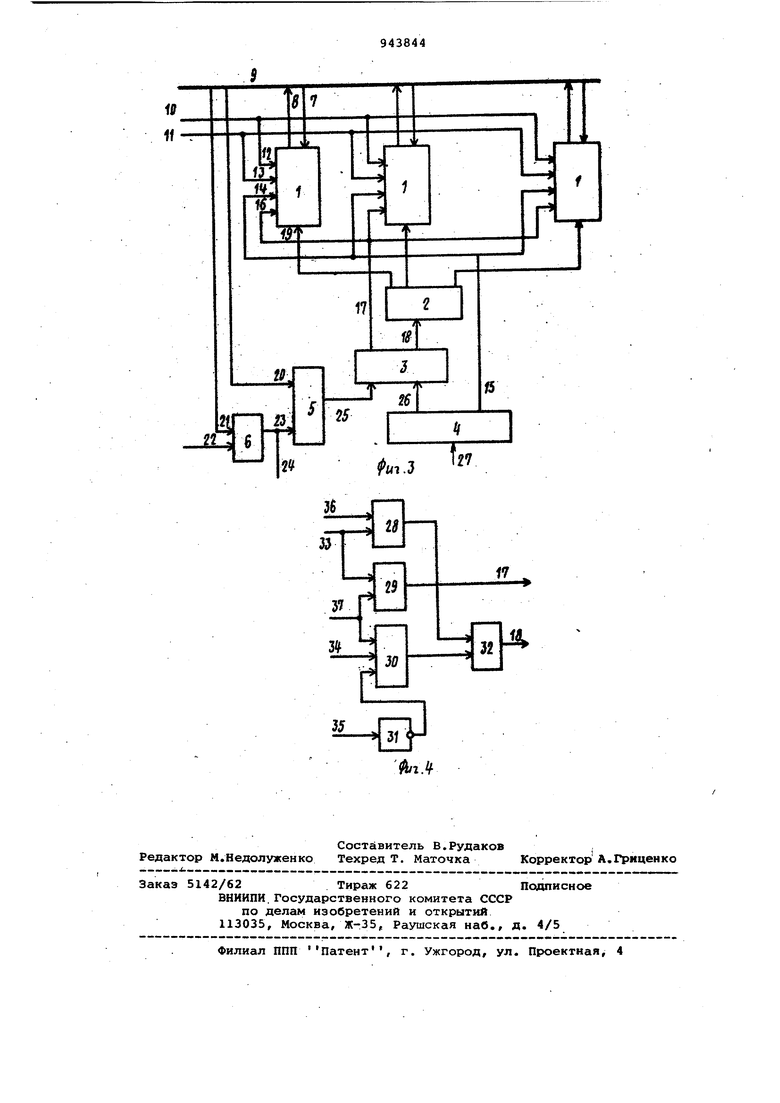

на фиг.З - структурная

схема предложенного ОЗУ, на фиг.4 функциональная схема блока корректировки адреса при 4, .

Емкость каждого блока памяти равна максимальной емкости ОЗУ, обеспечваемой принятой в данной ЭВМ разрядностью адресного поля команд. Предельное количество К р блоков памяти теоретически может быть очень большим и определяется выражением

NM N

(1),.

(1)

где а - разрядность адреса; N - емкость блока памяти;

NV.объем памяти, отводимый под

матобеспечение. Практически количество блоков памяти ограничивается реальными потребностями ЭВМ в емкости ОЗУ, повышающейся с ростом их числа сложностью согласования блоков памяти с внешней числовой магистралью и соображениями экономического характера. В общем случае для полного использорания емкости всех блоков памяти их количество должно выбираться из условия:

(...,

(2) К-- {если(,)(,-1/2) ,

(2Л4,... 1с„р если Мм/к|)/в/2)

Структура блока корректировки адреса зависит от отношения , которое удобно брать из ряда:...,15/16 7/8, 3/4, 1/2, 1/8, 1/16, ... .

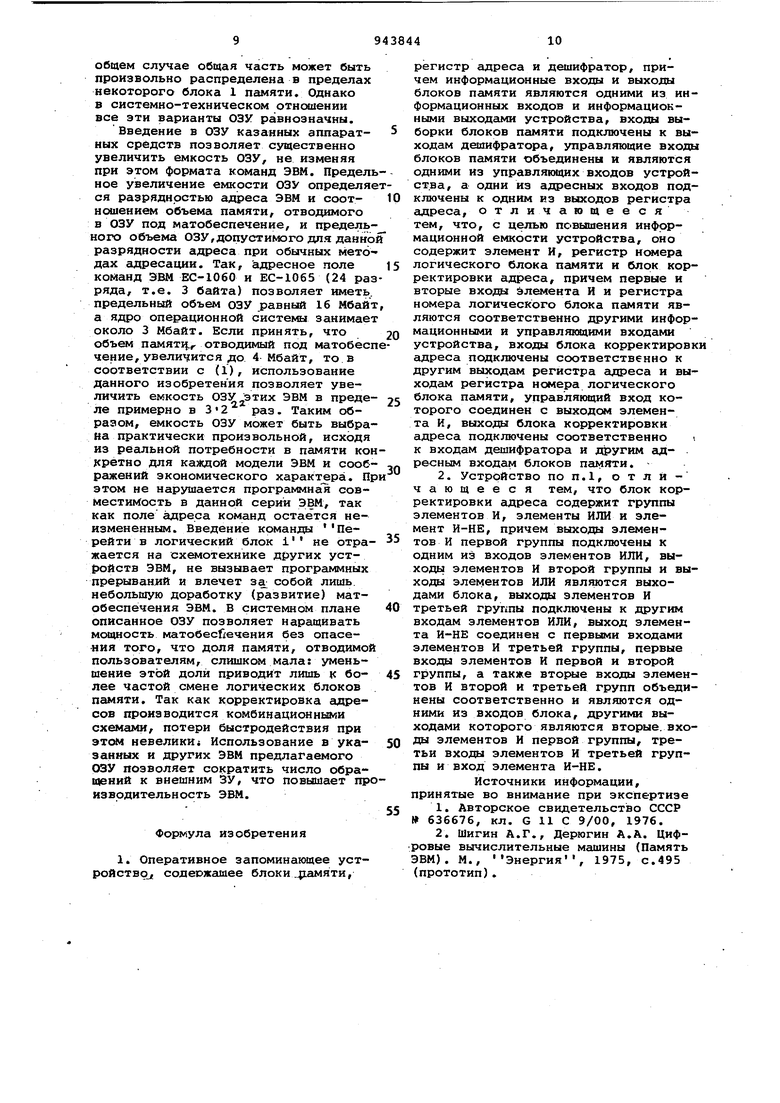

Рассмотрим структуру адресного пространства предложенного ОЗУ и прицип размещения в нем информации, предполагая условие (2) выполненным. Физический адрес слова в ОЗУ состоит из адреса Agp блока памяти и адреса СЛОВЕ ОО...От{п-1) в блоке памяти. В этом простраистве адресов ОЗУ организовано L логических блоков памяти (L больше К) емкостью N каждый таким образом, что некоторая часть адресного пространства является общей для всех логических блоков памяти. Она содержится в первом блоке памяти, занимая в нем ячейки с адресами 00...Of(п -1), и ей соответствует объем памяти Nf на фиг.1 и 2 она заштрихована). В этом поле адресов помещаются всё общие процедуры и данные, на которые есть ссылка из всех логических блоков памяти. В зависимости от соотношения Ыд и N могут быть два типа адресных пространств логических блоков памяти. При N/i/i/N меньше 1/2 (см.фиг.1 для ) в каждом из К блоков памяти содержится остальная (собственная) часть соответствуЕощего логического блока, занимающая в нем ячейки с адресами (п-1). Из оставшихся в блоках памяти 2гК свободных адресных полей 00,. .04-() формируются собственные части остальных (дополнительных) логических блоков Пс1МЯТИ (К+1)-гЬ , у которых логические адрес с п по (п-1) распределяются по блокам памяти следующим образом: для (К+1)-го логического блока памяти логические адреса (2пдл-1) соответствуют ячейкам 000,..От() второго блока памяти, логические адреса - ячейкам 00,,,От ) третьего блока памяти и т,д, до блока памяти включительно. Второй дополнительный ((К+2)-й) логический блок памяти располагается в ячейках 00,,,) ()-ro ()-го и т,д, до ()-ro блока памяти и т.д. Если первое из условий (2) не выполнено, то последний дополнительный логический блок памяти оказывается укомплектованным не полностью и, таким образом, он исключается, а соответствующее число блоков памяти недоиспользуется, В этом случае емкость таких блоков памяти может быть уменьшена до N-Nj, В частном случае при К меньше N/Nj, этот дополнительный логический блок памяти оказывается и единственным, и таким образом адесь , . При больше или равно 1/2 {см фиг.2) для N( распределение собственных частей логически-х блоко по блокам памяти 2-гК может быть организовано различными способами. Здесь собственная часть любого логического блока памяти всегда целиком укладываете) в пределах одного блока памяти, Весь объем N каждого логического блока памяти и каждого блока памяти рассматривается как N/N {для случая меньше 1/2) или N/(N-N) (при NfA/N больше или равно 1/2) массивов емкостью соот-ветственно N или (N-N() каждый. При зтом логический адрес, предъявляемый ОЗУ, представляется в виде А - номера логического блока памяти, - номера массив указанной емкости и АС смещения в это массиве,а физический адрес,предъявляемый блокам памяти,соответственно как Арп - номер блока памяти, базовый адрес массива и А - смещени в нем (оно сохраняется), Все программы пишутся в относительных адресах,для программных модулей размером не более N, которые распределяются системой по логически блокам памяти. Для перехода из блока в блок в системе команд ЭВМ- предусматривается одна дополнительная команда Перейти в логический блок i где i l-f-L, Введенные в ОЗУ аппаратные средства (элемент И), регистр номера логического блока памяти и блок корректировки адреса позволяют воспринять эту команду и осуществить соответствующую адресацию логических блоков в блоках памяти. Предложенное ОЗУ (см,фиг.З) состоит из нескольких блоков 1 памяти, дешифратора 2, блока 3 корректировки адреса, регистра 4 адреса, регистр 5 номера логического блока пг1мяти и элемента И 6, Каждый блок 1 памяти информационными входами 7 и информационными выходами 8 подключен к внешней числовой магистрали 9, Внешний вход 10 признака считывания и внешний вход 11 признака записи подключены соответственно к входам 12 признака считывания и входам 13 признака записи каждого блока 1 пеаляти. Младшие адресные входы 14 всех блоков 1 памяти поразрядно объединены и связаны с соответствующими выходами 15 младших разрядов регистра 4 адреса. Точно так же поразрядно объединены и старшие адресные входы 16, но подключены к младшим выходам 17 блока 3 корректировки адреса, старшие адресные выходы 18 которого соединены со входами дешифратора 2, выходы которого, в свою очередь, подключены к входам 19 выборки соответствующих блоков 1 Пс1МЯти. Информационные входы 20 регистра 5 и информационные входы 21 элемента И 6 подключены к тем разрядам внешней числовой магистрали 9, по которым передается соответственно адресная часть команды и ее код. Элемент И 6 имеет внешний управляющий вход 22, а выход его соединен с управляющим входом 23 регистра 5 и является внешним выходом 24 устройства. Выходы 25 регистра 5 связаны со старшими входами блока 3 корректировки, адреса, младшие входов которого соединены с выходами 26 старших разрядов регистра 4 адреса, последний имеет внешние адресные входы 27, Позициям элементов на фиг,3 соответствуют следующие обоз начения адресов: 26-Aj, 15(14) - АС, 18 - Арп, 17(16) - . Емкость каждого блока 1 памяти равна максимальной емкости ОЗУ, обеспечиваемой принятой в данной ЭВМ разрядностью адресного поля команд (предполагается, что условие (2) выполнено), Каждый блок 1 памяти может состоять из нескольких подблоков для организации расслоения, обращений. Количество старших адресных входов 16 блока 1 памяти.

младших адресных выходов 17 блока корректировки адреса 3, младших его адресных входов и выходов 26 старших разрядов регистра 4 адреса равны между собой и определяются соотнсяпением объема памяти, отводимого под матобеспечение ЭВМ, и емкости одного блока 1 памяти. Общее количество адресных входов 14 и 16 каждого блока 1 памяти равно количеству разрядов регистра 4 адреса.

Блок 3 корректировки адреса (см. фиг.4) состоит из трех групп элементов И 28-30, элемента И-НЕ 31 и группы элементов ИЛИ 32, Количество отдельных элементов И и ИЛИ в группах 28-30 и 32 равно разрядности кода адреса, поступающего на каждую из этих групп. На входы 33 элементов И 28 и 29 поступает двухразрядный ад рее Аj, на входы 34 элементов И 30 два младших разряда адреса А( ,на входы-35 элемента И-НЕ 31 - двухразрядныйинверсный код. адреса hj. На вход 36 элементо И 28 подается старший разряд адреса , а на вход 37 элементо И 29 и 30 - инверснйе значение старшего разряда адреса А.

ОЗУ работает следующим образом. (см.фиг.З);

Пусть на регистр 5 занесен некоторый логический адрес , а на старши и младшие разряды регистра 4 - соответственно адреса Ai и А. , .Вели AjstOO,, ,0, то независимо от значени А с выходов 18 блока 3 выдается код 00,,.О, и дешифратор 2 осуществляет выборку первого блока 1 памяти, С выходов 17 блока 3 также поступает код , ,,0, и обращение к ячейке выбранного первого блока 1 осуществляется в соответствии со смещением А, поступакицим с выходов 15 регистра 4, Если А ; 00.,,О, то блок 3 обрабатывает логические адреса А и Ai и выдает на входы дешифратора 2 физический адрес соответствующего блока 1 памяти, а в блоки 1 памяти - базовый адрес А -р , Дешифратор 2 осуществляет выборку адресуемого блока 1 памяти, а адрес елова в этом блоке 1 памяти составляется из адресов и АС. Режим считывания или записи в ОЗУ устанавливается в соответствии с признаком считывания /записи, поступающим на входы 10 и 11 и распределяемым далее по всем блокам 1 памяти, при этом информация поступает и выводитс из ОЗУ по внешней числовой магистрали 9,

.Описанные процессы повторяются многократно при различных значениях А и АС. При этом на информационные входы элемента И 6 и регистра 5 постоянно поступают различные коды,

сопровождаемые признаком команг да/данные на входе 22. Как только этот признак примет значени Ч (команда), а на информационных входах элемента И 6 появится код команда Перейти в логический блок i, элемент И 6 выдаст разрешающий сигнал на вход 23 регистра 5 и в него будет записан номер нового адресуемого логического блока памяти. Сигнал с выхода элемента И 6 подается также на выход 24 в качестве осведомительного о воспринятии этой команды. Таким образом, данное ОЗУ работает как обычное ОЗУ с той лишь разницей, что здесь постоянно корректируются, адреса в соответствии с принятой структурой адресного пространства.

Корректировка адресов производится следующим образом (см.фиг.4).

Если , то при любом значении старшего разряда адреса А, поступающего на входы 36 и 37, на выходах элементов И 28 и 29 будет код 00. Кроме того, элемент И-НЕ 31 выдаст запрещающий сигнал на элементы И 30. Таким образом, на выходах 17 блока 3 будет код A,, а на выходах 18 - код Agf,00 и, следовательно, в ОЗУ будет произведено обращение в первый блок 1 памя ти по адресу ООА (в общую часть всех логических блоков памяти). Если AJ 7 00, то при значении старшего разряда адреса Ai, равному О, на выходах 17 появится код А., а на выходах элементов И 30 - код двух .:младших разрядов адреса А, который в связи с закрытием элементов И 28 пройдет один через элементы ИЛИ 32 на выходы 18 в качестве адреса А, Таким образом, в ОЗУ реализуется обращение в собственную часть логического блока памяти, целиком расположенную в блоке 1 памяти с адресом , адрес ячейки в этом блоке Ajp А. Если значение старшего разряда адреса равно 1, то откроются элементы И 28 и закроются элементы И 30 и, таким образом, на выходах 18 код А равный AJ. Поскольку при этом элементы И 29 также заблокированы, то . Таким образом, в ОЗУ ещресована ячейка одного из блоков I памяти по адресу ООАс, принадлежащая дополнительному логическому блоку памяти. . ;

В других примерах конкретного быполнения ОЗУ используются иные структуры адресного пространства, что приводит к изменениям только в блоке 3 Так, общая часть всех логических блоков памяти может располагаться в старших адресах первого блока 1 памяти (и не обязательно первого), в общем случае общая часть может быть произвольно распределена в пределах некоторого блока 1 памяти. Однако в системно-техническом отношении все эти варианты ОЗУ равнозначны. Введение в ОЗУ казанных аппаратных средств позволяет существенно увеличить емкость ОЗУ, не изменяя при этом формата команд ЭВМ. Предел ное увеличение емкости ОЗУ определя ся разрядностью адреса ЭВМ и соотнсшением объема памяти, отводимого в ОЗУ под матобеспечение, и предель ного объема ОЗУ,допустимого для данно разрядности адреса при обычных мето дах адресации. Так, адресное поле команд ЭВМ ЕС-1060 и ЕС-1065 (24 ра ряда, т.е. 3 байта) позволяет иметь предельный объем ОЗУ равный 16 Мбай а ядро операционной системы занимае около 3 Мбайт. Если принять, что объем памятц,,. отводимый под матобес чение, увеличится до 4 Мбайт, то в соответствии с (1), использование данного изобретения позволяет увеличить емкость ОЗУ .jSTHX ЭВМ в преде ле примерно в 3«2 раз. Таким образом, емкость ОЗУ может быть выбра на практически произвольной, исходя из реальной потребности в памяти ко кретно для каждой модели ЭВМ и сооб ражений экономического характера. П этом не нарушается программная совместигЛость в данной серии ЭВМ, так как поле адреса команд остается неизмененным. Введение команда Перейти в логический блок i не отра жается на схетлотехнике других устройств ЭВМ, не вызывает программных прерываний и влечет за собой лишь небольшую доработку (развитие) матобеспечения ЭВМ. В системном плане описанное ОЗУ позволяет наращивать мощность матобеспечения без опасения того, что доля памяти, отводимо пользователям, слишком мала: уменьшение этой доли приводит лишь к более частой смене логических блоков памяти. Так как корректировка адресов производится комбинационными схемами, потери быстродействия при этом невелики; Использование в указанных и других ЭВМ предлагаемого ОЗУ позволяет сократить число обра прений к внешним ЗУ, что повышает пр изводительность ЭВМ. Формула изобретения 1. Оперативное запоминающее устройств содержащее блоки .хамяти. регистр адреса и дешифратор, причем информационные входы и выходы блоков памяти являются одними из информационных входов и информационными выходами устройства, входы выборки блоков памяти подключены к выходам дешифратора, управляющие входы блоков памяти объединены и являются одними из управляющих входов устройства, а одни из адресных входов подключены к одним из выходов регистра адреса, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит элемент И, регистр нсмера логического блока памяти и блок корректировки адреса, причем первые и вторые входы элемента И и регистра номера логического блока памяти являются соответственно другими информационными и управляющими входами устройства, входы блока корректировки адреса подключены соответственно к другим выходам регистра адреса и выходам регистра номера логического блока памяти, управляющий вход которого соединен с выходом элемента И, выходы блока корректировки адреса подключены соответственно i к входам дешифратора и другим адресным входам блоков памяти. 2. Устройство ПОП.1, отличающееся тем, что блок корректировки адреса содержит группы элементов И, элементы ИЛИ и элемент И-НЕ, причем выходы элементов И первой группы подключены к одним из входов элементов ИЛИ, выходы элементов И второй группы и выходы элементов ИЛИ являются выходами блока, выходы элементов И третьей группы подключены к другим входам элементов ИЛИ, выход элемента И-НЕ соединен с первыми входами элементов И третьей группы, первые входы элементов И первой и второй группы, а также вторые входы элементов И второй и третьей групп объединены соответственно и являются одними из входов блока, другими выходами которого являются вторые, входы элементов И первой группы, третьи входы элементов И третьей группы и вход элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 636676, кл. G 11 С 9/00, 1976. 2.ШИРИН А.Г., Дерюгин А.А. Цифровые вычислительные машины (Память ЭВМ). М., Энергия, 1975, с.495 (прототип).

г 3

iff If

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Опреративное запоминающее устройство | 1976 |

|

SU645204A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1293730A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Устройство для вывода информации | 1990 |

|

SU1727127A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Авторы

Даты

1982-07-15—Публикация

1980-12-24—Подача