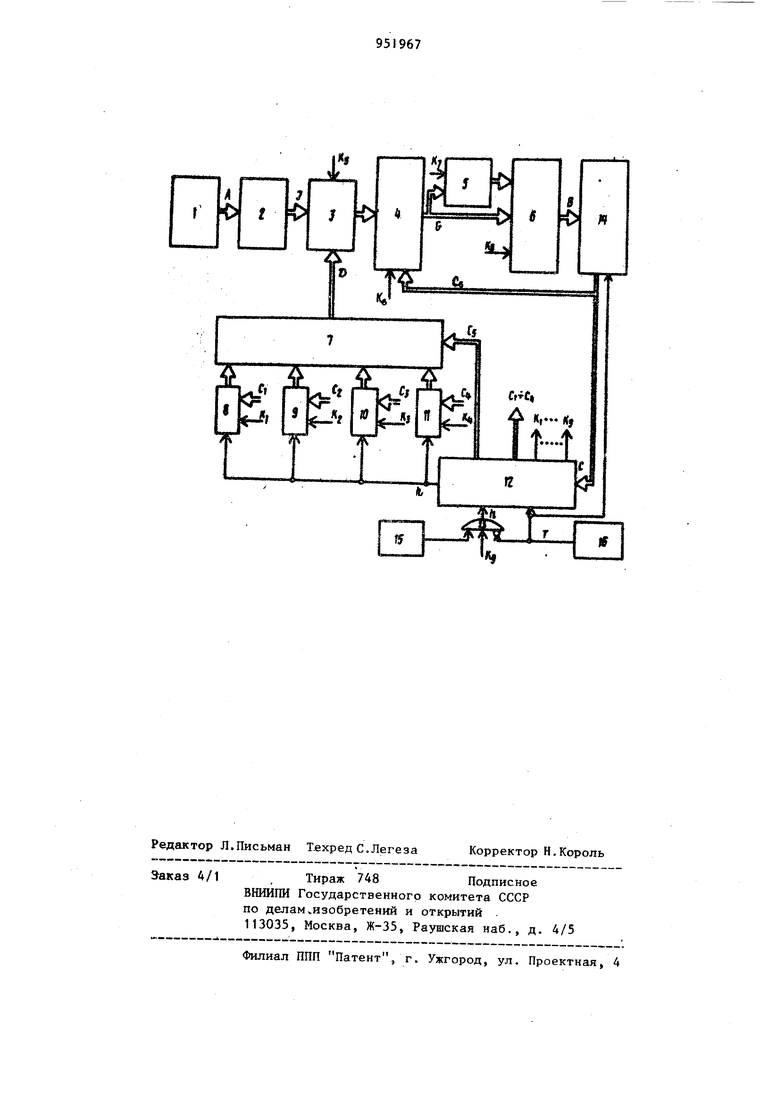

Изобретение относится к детекторам элементарных частиц и атомных ядер и может быть использовано в различных областях науки и техники при экcпвpимeнтaль cыx исследованиях Известны устройства для регистрации, схема и обработки информации с пропорциональных камер lj , содержащие усилители-формирователи для усиления сигнала с пропорциональных камер и формирования их до амплитуды логического уровня , схемы задержки для совпадений со стробом за си блоки памяти для запоминания информации и системы считывания, включающие в себя ворота считывания параллельные сдвиговые регистры, ло ку поиска, управление считыванием и обработкой. Данные из регистрирую щей электроники считываются параллельно-последовательным способом и заносятся в промежуточньм регистр. Разряды этого регистра проверяются последовательно на содержание и при обнаружении единицы кодируются и передаются в ЭВМ. Ввиду большого мертвого времен системы регистрации и считывания, в случае интенсивного и короткого сброса пучка ускорителя, происходит потеря полезной информации и требуе ся быстрая промежуточная память. Кроме того, отсутствует возможност получения необходимой информации о временном и пространственном распределении фоновых событий. При использовании этих устройств в установках с большим числом каналов регистрации наряду с проблемой повышения надежности электронной системы необходимо снижение стоимости канала регистрации. .Наиболее близким по технической сущности к предложенному является устройство 21 , содержащее усилите|ли, оперативные запоминающие устрой ства с произвольной выборкой, адресный счетчик, выходные ворота, блок считывания и управления, генератор синхроимпульсов. Информация, поступающая с пропорциональных камер, регистрируется в запоминающи устройствах синхронно с импульсами генератора в течение некоторого вре менного интервала, а затем параллельно считывается и обрабатывается программным путем. Устройство не позволяет непосред ственно указывать адрес ячеек запоминающих устройств, в которых содержится полезная информация. Для ее извлечения необходимо опросить с помощью ЭВМ все адреса запоминающих устройств, что ограничивает быстродействие считывания. Кроме того, из-за параллельного способа съема информации это устройство не может быть использовано в системах с большим числом каналов регистрации. Цель изобретения - повышение быстродействия считывания и расширение функциональных возможностей устройства. Цель достигается тем, что в устройство, содержащее последовательно включенные камеры, усилители-формирователи, оперативные запоминающие устройства с произвольной выборкой, а также блоки управления и считывания, источник тактовых сигналов, ввег дены четьфе адресных счетчика с предварительной установкой, мультиплексор информационный, мультиплексор адресный, буферный регистр, блок выходной логики, блок предварительного отбора событий и схема И, причем выход источника тактовых сигналов подключен к первому входу схемы И, второй вход которой соединен с выходом блока отбора событий, а также с входами блока управления и блока считывания, выход схемы И соединен с вторым входом блока управления, а соответствующий этому входу выход блока управления соединен с входами четырех адресных счетчиков, установочные и управляющие входы которых соединены с блоком управления, а их выходы - с входами адресного мультиплесора, адресный вход которого подключен к соответствующему выходу блока управления, а выход - к адресным входам оперативных запоминающих устройств; выходы запоминающих устройств соединены с соответствующими входами информационных мультиплексоров, управляющие входы которых соединены с блоком управления, а выходы мультиплексоров подключены к первому входу выходной логики и к выходу буферного регистра, выход которого соединен с вторым входом выходной логики, а выход выходной логики соединен с блоком считырзания, которьй соединен с командным входом блока управления и адресными входами информационных мультиплексоров . 3 управляющие входы буферного регистра и блока выходной логики подключены к соответствующим выходам блока управления. На чертеже изображена блок-схема описываемого устройства. Устройство содержит пропорциональные камеры 1, усилители-формирователи 2, оперативные запоминающие устройства 3 с произвольной выборкой (ОЗУ), мультиплексоры 4 информационные, буферный регистр 5, выходную логику 6, мульти плексор 7 адресный, адресные счетчики 8-11, блок 12 управления, логическую схему И 13, блок 14 считывания, источник 15 тактовых сигналов, блок 16 отбора событий. Регистрирующая часть устройства включающая усилители-формирователи 2, запоминающие устройства 3, мул типлексоры информационные 4, расположенные непосредственно на пропорциональных камерах 1. Буферный регистр 5, выходная логика 6, так же как и адресная логика, включающая в себя элементы 7-13, являются общими для всех пропорциональных камер 1 и расположены на первой камере. Каждая группа сигнальных электродов, на которые разбиты электроды каждой камеры, соединена по шинам А с соответствующими входами усилителей-формирователей 2,выходы которых подключены в том же соответствии к информационным входам запоминающих устройств 3. Адресные входы запомина щих устройств 3 соединены общей шиной D с выходом адресного мультиплексора 7. Для опроса запоминающих устройств 3 используются мультиплекс ры 4, входы которых соединены с соот ветствующими выходами запоминающих устройств 3. Мультиплексоры 4, расположенные на камерах 1, соединены с выходной логикой 6 и буферным регистром 5 шиной Q , а выход выходно логики 6 подключен к блоку 14 считывания через магистраль В. Устройство режиме записи информации работает следующим образом. По сигналам, поступившим по шине С с блока 14 считывания, в соответстви с программой его работы, в блок 12 управления, вырабатываются управляю1цие сигналы К. Сигналы разре шают предварительную установку начал ных состояний адресных счетчиков 8-11, которые поступают по шинам 7 12 управления. По сигС -Сд от блока , поступающим от блока 12 управления по шине С адресный мульти плексор 7 переключается на входы, соединенные с выходом разрядов адреса ного счетчика 8. С поступлением сигнала Кл импульсы от источника тактовых сигналов 15 поступают через логическую схему И 13 на блок управления, а затем на входы адресных счетчиков 8-11 и увеличивают на единицу число, хранящееся BI каждом счетчике 8-11. Отметим, что в качестве источника тактовых сигналов 15 могут быть использованы сигналы от тактового генератора или же, в случае работы на ускорителе с банчированной структурой пучка, - сигналы от каждого банча. Код адреса оперативных запоминакхцих устройств 3 поступает на их адресные входы с выхода адресного счетчика 8 через адресный мультиплексор 7 по шине D . Изменение кода адреса запоминающих устройств 3 происходит синхронно с импульсами h от источника тактовых сигналов 15. Информация, поступающая на входы оперативных запоминающих устройств по шинам А и от пропорциональных камер 1, записывается в тот адрес, который указывает в этот момент адресный счетчик 8. В момент смены адреса информационные входы запоминающих устройств 3 блокируются сигналами Кс, поступающими на их управляющий вход от блока 12 управления. В оперативные запоминающие устройства 3 записывается вся информация, которая поступает на их входы и прекращается к поступлением сигнала Т на логическую схему И 13. В этом случае блокируются импульсы от источника тактовых сигналов 15, т.е. прекращается смена адреса. Сигнал Т вырабатывается блоком 16 отбора только в случае регистрации камерами полезного события, определяемого по заданным пааметрам. Так как на выработку сигнала Т блоком 16 отбора событий и потупления его на логическую схеу И 1 3 требуется некоторое постояное время TQ, то момент запрета мены адреса запаздывает по отноению к моменту записи информации об тобранном событии в зяпоминающие

устройства 3 на это же время Т, Поэтому в течение этого времени коп адреса, поступающий на запоминающие устройства .по шине ) от адресного счетчика 8, может изменяться п раз ( П - число тактовых импульсов за время TQ ) наличии на входе запоминающих устройств 3 информации, она запишется в них, С поступлением сигнала Т на блок 12 управления и блок 14 считывания осуществляется переключение адресного мультиплексора 7 на входы, соединенные с выходом разрядов адресного счетчика 9, выдается сигнал t на управляющие входы Считывание запоминающими устройствами 3 , и начи- нается считывание информации из запоминающих устройств 3. Несмотря на то что в ячейках памяти записана как фоновая; так и полезная информация, считывается однако только информация об отобранном событии. Адрес ячеек, в. которых она записана, поступает по шине 1 на адресные входы запоминающих устройств 3 через мультиплексор 7 с выхода разрядов адресного счетчика 9. Непосредственное поступление на адресные входы запоминающих устройств 3 адреса ячеек, в которых записана полезная информация, возможно благодаря постоянству времени Т поступления сигнала Т на логическую схему И 13, равно nt , где {, - период источника тактовых сигналов. Как уже отмечалось ранее, за время Т состояние адресных счетчиков 8-11 изменится и раз. Поэтому, если предварительное начальное состояние адресного счетчика 5 увеличить на и единиц по отношению к предварительному начальноьгу состоянию адресного счетчика 9, то в момент их блокировки адресный счетчик 9 всегда будет показывать адрес ячеек, в которых записана информация об отобранном событии. Необходимая разность в начальных состояниях адресных счетчиков 8 и 9 устанавливается экспериментально перед началом измерений.

Таким образом, использование второго адресного счетчика 9 позволяет без каких-либо дополнительных on раций и логических блоков выдавать на адресные входызапоминающих устройств 3 требуемый адрес ячеек, информация из которых сразу же считывается, что значительно-повьшает быстродействие устройства при считывании информации.

Считывание информа,ции из оперативных запоминающих устройств 3 осуществляется следующим образом.

По сигналам, поступающим от блока 14 считьшания по шине С , блок 12 управления вырабатывает необходимые для считывания управляющие сигналы);. Сигналы К поступают на мультиплексоры 4, расположенные на выбранной камере, информацию от которой мы хотим : извлечь. Затем, для опроса запоминающих устройств 3, находящихся на В1м-бранной камере, блок 14 считывания включает по шине С н С , соединенной с адресными входами мультиплексоров 4, первьм вход этих мультиплексоров для каждой группы сигнальных электродов камеры. Информация, содержащаяся в ячейках соответствующих данному номеру входа мультиплексоров 4, адрес которых указывает адресный счетчик 9, поступает параллельно от каждой группы через мультиплексоры 4 и выходную логику 6, которая по сигналу Kg пропускает ее по магистрали В в блок 14 считывания. Затем блоком 14 считывания выдается номер следующего входа мультиплексоров и т.д.

По окончании считывания информации из оперативных запоминающих устройств 3, расположенных на выбранной камере, включаются мультиплексоры 4, расположенные на следующей камере, н процесс считьшания повторяется.

Таким образом, использование мультиплексоров 4 для опроса запоминающих устройств 3 позволяет перейти от параллельного способа передачи информации к параллельно-последовательному и, кроме того, позволяет получить информацию от любой заданной проволочки или группы проволочек пропорциональных камер. Информация о временном и пространственном распределении фоновых собьггий может быть получена программным управлением, считывая последовательно содержимое ячеек запоминающих устройств 3, адреса которых поступают на установочные входы адресного счетчика 9 по шине Сл от блока t2 управления.

Информация о фоновых событиях, приводящих к искажению полезной ниформации,, может быть получена автономным путем. Это позволяют сделать адресные счетчики 10 и И. Для этой цели предварительное начальное состояние адресных счетчиков 10 и 11 уменьшено и увеличено соответственно на 1 по отношению к предварительному начальному состояншо адресного счетчика 9. Считывание в этом случае осуществляется следукидим образом Мультиплексор 7 переключается блоком 12 управления на входы связанные с выходом разрядов адресного счетчика 10. Код адреса, показываемый этим счетчиком, поступает на запоминающие устройства 3, а информаци содержащаяся в этом адресе, поступает через мультиплексоры 4 в буферный регистр 5 и при наличии сигнала К 7 О блока. 12 управления запомиЗатем мультиплексор 7 кается в нем. переключается на входы, связанные с выходом разрядов адресного счетчика и информация, содержащаяся в ОЗУ, с адресом, указываемом зтим счетчиком, поступает на выходную логику 6, которая представляет собою арифметическое и логическое устройство и организована в режиме антисовпадения. На выходе выходной логики 6 сигнал п явится только в случае отсутствия единиц в соседних ячейках с адресами, показываемыми адресными счетчиками 9 и 10. Таким образом, использование адресного счетчика 10 и выходной логики 6 позволяет исключить на стадии считывания сопутствукнций полезному событию фон. Для этой же цели служит адресн счетчик 11, с тем лишь отличием, что он указывает адрес фоновых событий, поступивших на запоминающие устройства 3 вслед за полезным событи&4. По сравнению с известным устройством описанное устройство имеет большее быстродействие и может быть использовано в системах с любым числом каналов регистрации, так как введение информационных мультиплексоров 4 для опроса оперативных запоминающих устройств 3 позволяет сократить до минимума число линий, используемых для передачи данных, и позволяет, по желанию, получить информацию от любой проволочки камер. Кроме того, предлагаемое устройство позволяет провести предварительную обработку зарегистрированных событий на стадии передачи информации из регистрирукщей электроники в блок 14 считывания и управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ, СЪЕМА И ОБРАБОТКИ ИНФОРМАЦИИ С ПРОПОРЦИОНАЛЬНЫХ КАМЕР, содержащее последовательно включенные камеры, усилители-формирователи, оперативные запоминающие устройства (ОЗУ) с произвольной выборкой, а также блоки управления и считывания, источг ник тактовых сигналов, отличающееся тем. что, с целью повышения быстродействия считывания и расширения функциональных возможностей устройства, введены четыре адресных счетчика с предварительной установкой, мультиплексор информационный, мультиплексор адресный, буферньй регистр, блок выходной логики, блок предварительного отбора событий и схема И, причем выход источника тактовых сигналов подключен к первому входу схемы И, второй вход которой соединен с выходом блока предварительного отбора событий, а также с входами блока управления и блока считывания, выход схемы И соединен с вторым входом блока управления, а соответствующий этому входу выход блока управления соединен с входами четырех адресных счетчиков, установочные и управляющие входы которых соединены с блоком управления, а их выходы - с входами адресного мультиплексора, адресный вход которосл го подключен к соответствующему выходу блока управления, а выход - к адресным входам ОЗУ, выходы ОЗУ соединены с соответствзпощими входами информационных мультиплексоров, управляющие входы которых соединены с со :л блоком управления, а выходы мультиплексоров подключены к первому входу выходной логики и к входу буферного регистра, выход которого соединен с вторым входом выходной логики, а выход выходной логики соединен с блоком считывания, который соединен с командным входом блока управления и адресными входами .информационных мультиплексоров, управляющие входы буферного регистра | и блока выходной логики подключены к соответствующим выходам блока управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Колпаков И.Ф | |||

| Электронная аппаратура на линии с ЭВМ в физическом эксперименте, М,, Атомиздат , 1974, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Pernicka, S.Sychkov, The Advautages of a rotated Multiwire Proportional Ckamber with special drift - time electronics | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Насос | 1917 |

|

SU13A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

Авторы

Даты

1985-01-07—Публикация

1980-07-24—Подача