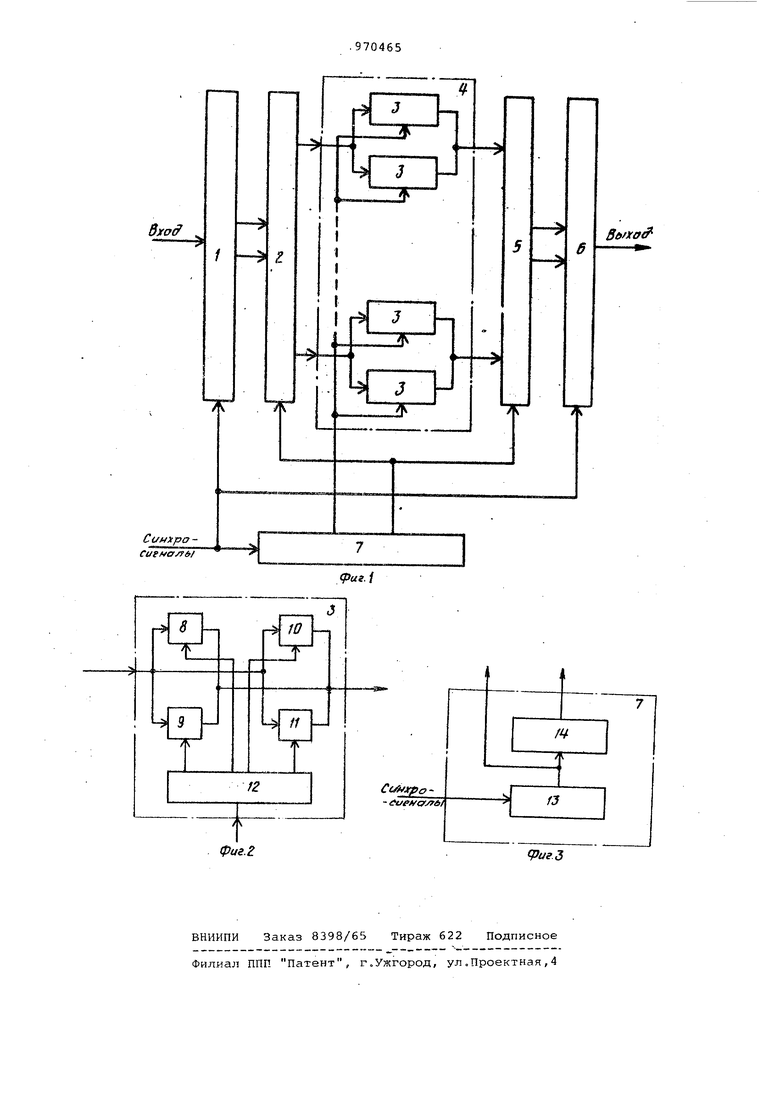

UK ко входам мультиплексора в режиме считывания/ быстродействие снижается за счет задержки вывода информации на время, определяемое скоростью поиска требуемого запоминающего элемента запоминающих ячеек. На выходе мультиплексора считываемая информация появляется через интервал времени, определяемый временем поиска адреса требуемого запоминающего элемен та и временем задержки считывания информации, что приводит, к низкому быстродействию устройства, Цель изобретения - повышение быст родействия запоминающего устройства. Поставленная цель достигается тем что в запоминающее устройствог содер жащее матричный накопитель, демульти плексор, выходы которого подключены соответствующим входам регистра,блок управления, первый вход которого под ключен к управляющим вкодс1м ячеек па мяти накопителя, а второй - к тактовому входу регистра, мультиплексор, выход которого является выходом уст ройства, вход блока управления мультиплексора и один из входов демульти плексора являются входом синхронизации устройства, а другой вход демуль типлексора является информационным входом устройства, введен дополнител ный регистр, выходы которого подключены к соответствующк.й входам мульти плексора. При этом информ 1цйонные входы каждой пары ячеек Пс1мяти накопителя объединены к подклвэчены к соответствующим выходам регистра, а выходы упомянутых пар ячеек памяти объединены и подключены к соответствующим входам дополнительного регист ра, тактовый вход которого подключен ко второму входу блока управления. Каждая ячейка памяти накопителя содержит запоминающие элементы, информационные входы которых объединены и являются входом ячейки памяти, выходы запоминающих элементов объеди йены и являются информационными выходами ячейки памяти, входы управления запоминающих элементов подключены к соответствующим выходам дешифратора, вход которого является управ ляющим входом ячейки памяти. Блок управления содержит счетчик, вход которого является входом-синхронизации устройства, сум;матор, вход которого подключен к выходу счетчика, а выходы сумматора и счетчика являются соответстве-нно первым и вто рым выходами блока управления. Такое построение предлагаемого устройства позволяет повысить быстродействие за счет того, что в процессе Обращения к первой запоминающей ячейке производится запись в п запоминающий элемент, а считывание производится из п+2 запоминающего элемента, причем информация переносится в дополнительный регистр, где i производится промежуточное хранение этой информации. В следующий период обращение производится к второй запоминающей ячейке, причем производится запись в п-1 3апомингиощий элементу а считывание - из п+1 запоминающего элемента (, 6, 10, 14...). Таким образом, в дополнительном регистре . ;информация, подлежащая выводу, появляется до начсша считывания, т.е. производится компенсация времени, необходимого для поиска требуемого запоминающего элемента. При поступлении команды считывания информация считывается не из запомннаиощих элементов, а из дополнительного регистра и переносится в мультиплексора выход которого является выходом устройства. При этом задержка вывода информации определяется не временем поиска адреса и вывода информации из запоминающего элемента, а только быстродействием дополнительного регистра. На фиг.1 представлена структурная схема запоминающего устройства; на фиг.2 - структурная ехема ячейки памяти запоминающего устройства; на фиг.З - структурная схема блока равления запоминающего устройства. Запоминающее устройство содержит демультиплексор 1 (фиг.1), вход которого является входом устройства, а выходы соединены с соответствующими . входами регистра 2. К каждому выходу регистра 2 подключены два входа ячеек 3 памяти накопителя 4. Выходы каж-. дых двух ячеек 3 памяти подключены к соответствующему входу дополнительного регистра 5, выходы которого соединены с входами мультиплексора 6. Выход мультиплексора 6 является выходом устройства. На тактовые входы демультиплексора 1, мультиплексора б и блока 7 управления поданы синхросигналы от синхрогенератора. Первый выход блока 7 управления подключен к управляющим входам ячеек 3 памяти. Ячейка 3 памяти (фиг.2) состоит из запоминающих элементов 8-11, входы которых подключены к входу ячейки 3 памяти. Выходы запоминающих элементов 8-11 подключены к выходу ячейки 3 памяти. Управляющие входы запоминающих элементов 8-11 подключены к соответствующим выходам дешифратора 12, вход которого подключен к управляющему входу ячейки памяти 3. Запоминающие элементы 8-11 выполнены, например, в виде МОП-прибора, хранение информации в котором происходит на емкости затвора. Блок 7 управления (фиг.З) состоит из двоичного счетчика 13, выполненнЬ го, например, на последовательно включенных триггерах. На вход счётчи ка 13 поданы синхросигналы. Выход счетчика 13 подключен к входу сумматора 14. Выход сумматора 14 подключе к первому выходу блока 7 управления, ко второму выходу которого подключен выход счетчика 13. Предлагаемое устройство работает следующим образом. На вход дёмультиплексора 1 посту(Пает цифровая информация. На выходах |демультиплексора 1 информация разделяется на ряд каналов, которая переносится в регистр 2, производящий промежуточное хранение поступающей информации. С выходов регистра 2 информация поступает в ячейки 3 Пс1мяти накопителя 4. На тактируклдие входы дёмультиплексора 1, мультиплексбра 6 и на вход счетчика 13 блока 7 управления поступают синхросигналы от синхрог«нератора. Сигналы управления в виде кодовых комбинаций поступают с выхода счетчика 13 блока 7 управле ния на тактирующие входы регистра 2 и дополнительного регистра 5, а также на вход сумматора 14. Сигналы управления с .выхода сумматора 14 блока управления 7 поступают на входы дешифраторов 12 ячеек памяти 3. На выходах дешифратора 12 ячейки 1 памяти формируются сигналы управления запоминаюсцими элементами 8-11. Поступающая на вход ячейки 3 информация записывается и считывается в том запомингиощем элементе 8-11/ на управ ляющий вход которого поступил сигнал управления с соответствукицего выхода дешифратора 12 ячейки 3 памяти. Сигнал с выхода запоминающего элемента 8 19-11) поступает на выход ячейки 3 памяти накопителя 4. С выходов каж дои пары ячеек 3 памяти оигналы поступают на соответствующие входы дополнительного регистра 5, в котором происходит хранение информации до по ступления команды считывания из запоминающего устройства. После поступ ления команды Считывание .хранимая в дополнительном регистре 5 информация поступает на входы мультиплексора б, выход которого являе.тся выходо устройства. Команда управления, формируемые на выходах дешифратора. Использование предлагаемого цифрового, запоминающего устройства позволит вести разработку надежной и быстродействующей аппаратуры цифровой обработки видеосигнала. Применег ние цифрового запоминсшзщего устройст ва позволит использовать динамически МОП запоминающие элементы, которые не обладают требуешлм быстродействием. Однако пЬ сравнению с другими ти пами запоминающих .элементов они обладают в 10 раз меньшей мощностью потребления, простри технологией про изводства (3 технологические операции) , и в 4 раза большей степенью интеграции. Проъишленное производств во предлагаемого устройства не требует дефицитных материалов и может быть реализовано с использованием серийно выпускаемых комплектующих изделий. Формула изобретения 1.Запоминающее устройство, содержащее матричный накопитель, демультиплексор, выходы которого подключены к соответствующим входам регистра, блок управления, первый вход котй{х го подключен к управляющим входам ячеек памяти накопителя, а второй к тактовому входу регистра, мультиплексор, выход которого является выходом устройства, вход управления, г льтиплексора и один из входов демультиплексора- являются входом синхронизации устройства, а другой вход демультиплексора является информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный регистр, выходы которого подключены к соответствующим входам мультиплексора, при . этом информационные входы каждой пары ячеек памяти накопителя объединены и подключены к соответствующим Btiходам регистра, а выходы упомянутых Пар ячеек памяти объединены и подключены к соответствующим входам дополнительного регистра, тактовый вход которого подключен к второму входу блока управления. 2.Устройство по г.1, отличающееся тем, что ячейка памяти накопителя содержит запоминал)щие элементы, информационные входы которых объединены и являются входом ячейки памяти, выходы запоминающих элементов объединены и являются информационными выходами ячейки памяти, входы управления запоминающих элементов подключены к соответствующим выходам дешифратора, вход которого является управляющим входом ячейки памяти. 3.Устройство по n.i, о т л и чающееся тем, что блок управления содержит счетчик, вход которюго является входом синхронизации . устройства, сукматор, вход которого подключен к выходу счетчика, а выходы сумматора и счетчика являются соответственно первым и вторым выходами блока управления. Источники информации, принятые во внимание при экспертизе 1. Заявка Франции № 2379133, л. G 11 С 11/34, опублик. 1979. 2. Кривошеев М.И. Цифровое телевиение. М., Связь, 1980, с. 122-128 (прототип).

фиг. 2

РигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство памяти на телевизионный кадр | 1987 |

|

SU1559430A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство коммутации | 1980 |

|

SU894866A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-23—Подача