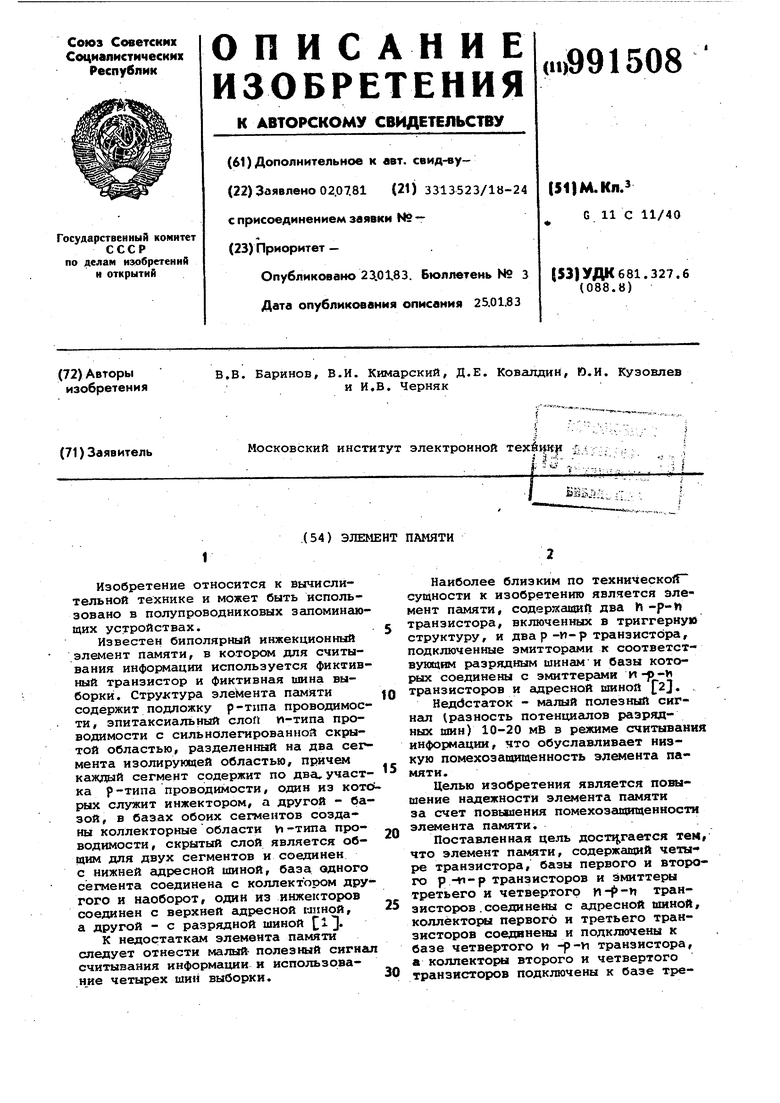

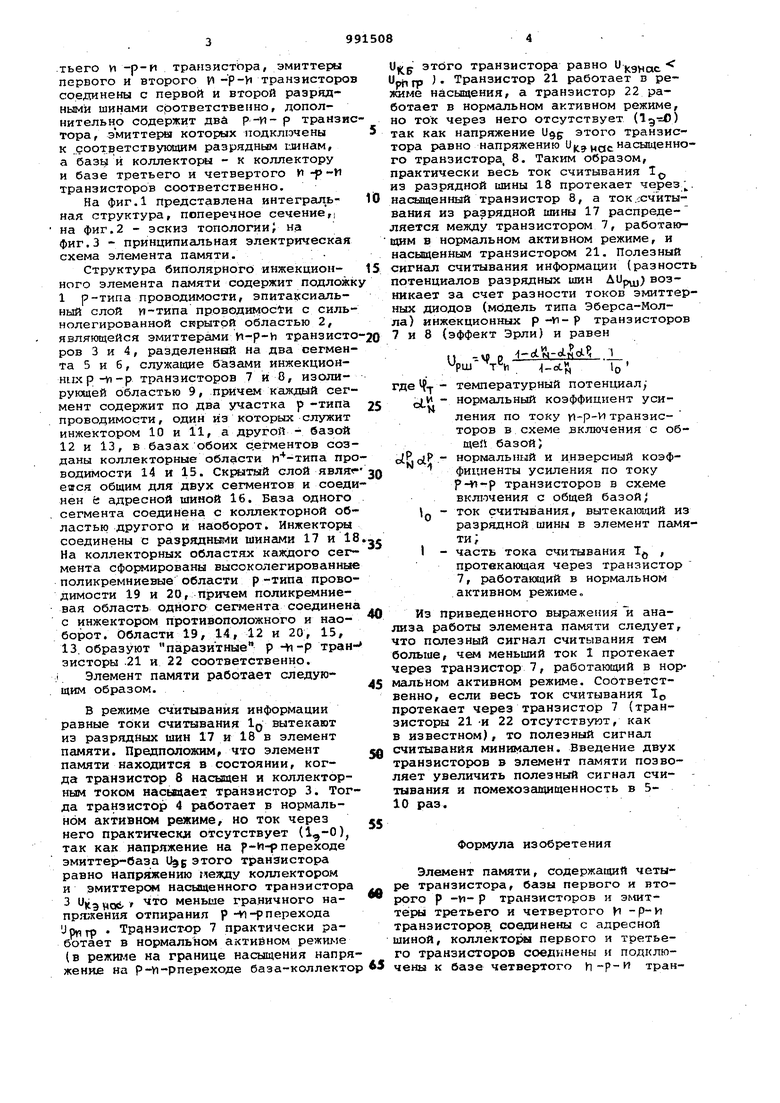

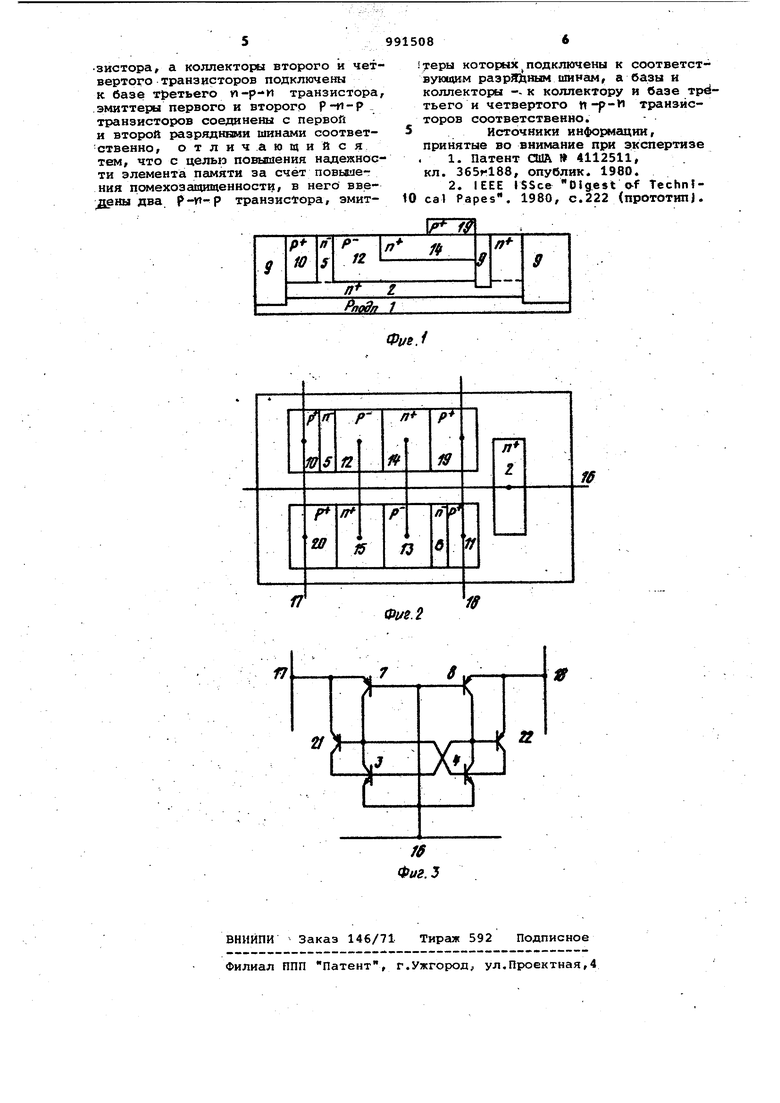

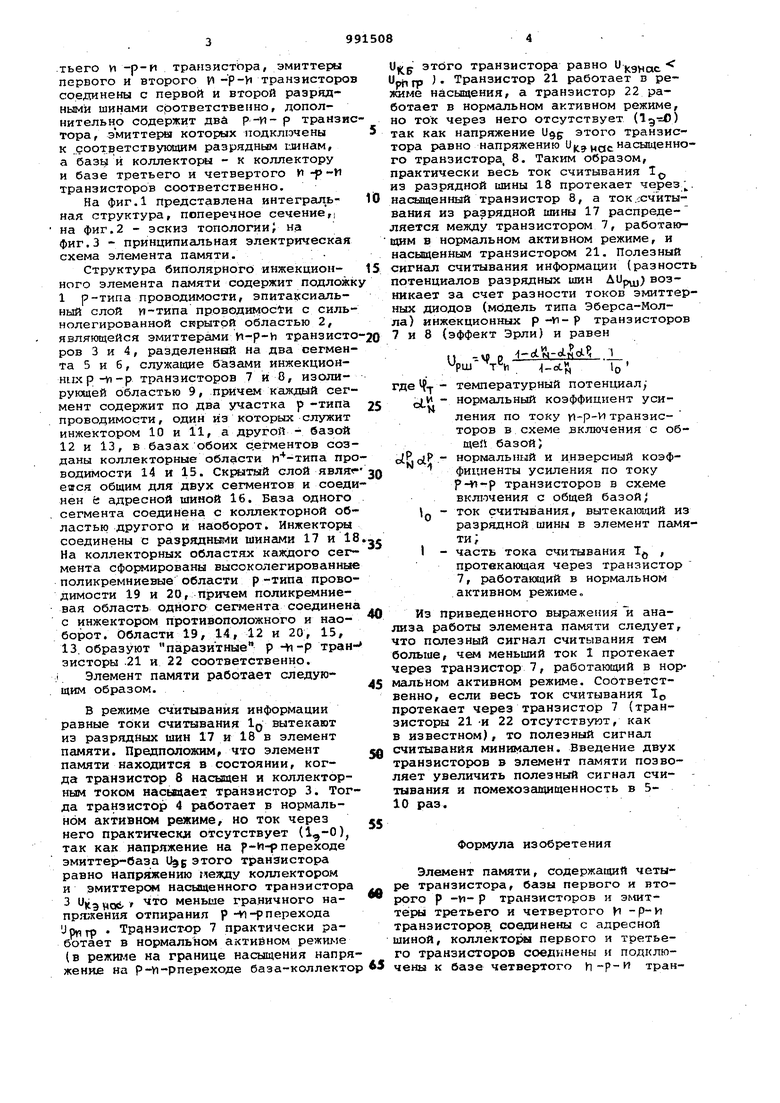

.(54) ПАМЯТИ Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых згшомингио щих устройствах. Известен биполярный инжекционный элемент паиняти, в котором для считывания информации используется фиктив ный транзистор и фиктивная шина выборки. Структура элемента памйти содержит подложку р-типа проводимос ти, зпитаксиальный слоп п-типа проводимости с сильнолегированной скрытой областью, разделенный на два сег мента изолирующей областью, причем каждый сегмент содержит по два участ ка р-типа проводимости, один из KOT рых служит инжектором, а другой - ба зой, в базах обоих сегментов созданы коллекторные области и-типа проводимости , скрытый слой является общим для двух сегментов и соединен с нижней адресной шиной, база одного сегмента соединена с коллектором дру гого и наоборот, один из инжекторов соединен с верхней адресной миной, а другой - с разрядной шиной 1. К недостаткам элемента памяти следует отнести малый- полезный сигна считывания информации и использование четырех шин выборки. Наиболее близким по технической сущности к изобретению является элемент памяти, содаржащиЛ два h -р-И транзистора, включенных в триггерную структуру, и двар-м-р транзистора, подключенные змитторами к соответствующим разрядным шинам и базы которых соединены с эмиттерами и-р- транзисторов и адресной шиной f2J. Неддстаток - малый полезный сигнал (разность потенциёшов разрядных шин) 10-20 мВ в режиме считывания информации, что обуславливает низкую помехозащищенность элемента памяти. Целью изобретения является повышение надежности элемента памяти за счет повьяаения помехозащищенности эл04ента памяти. Поставленная цель достц,гается тем, что элемент памяти, содержащий четыре транзистора, базы первого и второго p-f-p транзисторов и эмиттеры третьего и четвертого транзисторов .соединены с адресной шиной, коллектор первого и третьего транзисторов соединены и подключены к базе четвертого и -p-vi транзистора, а коллекторы второго и четвертого транзисторов подключены к базе тре.тьего и -p-fi xpanBHCTinpa, эмиттеры первого и второго (1 -p-Vi транзисторо соединены с первой и второй разрядными шинами срответственно, дополнительн.о содержит двй p-vi- р транзи тора, эмиттеры которых подключены к .соответствующим разрядным глинам, а баз1 и коллекторы - к коллектору и базе третьего и четвертого И -j -И транзисторов соответственно. На фиг.1 представлена интегральная структура, поперечное сечение, на фиг.2 - эскиз топологии на фиг.З - принципиальная электрическая схема элемента памяти. Структура биполярного инжекционнего элемента памяти содержит подложк 1 р-типа проводимости, эпитаксиальный слой м-типа проводимости с сильнолегированной скрытой областью 2, являющейся эмиттерами VI-p-V) транзисто ров 3 и 4, разделеннБгй на два сегмента 5 и 6, служащие б&зами инжекционHijxp-ti-p транзисторов 7 и О, изолирующей областью 9, причем каждый сегмент содержит по два участка р -типа проводимости, один из которых служит инжектором 10 и 11, а другой - базой 12 и 13, в базах обоих сегментов созданы коллекторные области м -типа про водимости 14 и 15. Скрытый слой явля еися общим для двух сегментов и соеди нен и адресной шИной 16. База одного сегмента соединена с коллекторной областью другого и наоборот. инжекторы соединены с разрвдныгли шинами 17 и 18 На коллекторных областях каждого сегмента сформированы высоколегированные поликремниевые области р-типа проводимости 19 и 20, Причем поликремниевая область одного сегмента соединена с инжектором противоположного и наоборот. Области 19, 14, 12 и 20, 15, 13, образуют паразитные р -V)-р транзисторы 21 и 22 соответственно. Элемент памяти работает следующим образом. . В режиме считывания информации равные токи считывания IQ вытекают из разрядных шин 17 и 18 в элемент пг1мяти. Предположим, что элемент памяти находится в состоянии, когда транзистор 8 насыщен и коллекторным током насыщает транзистор 3. Тогда транзистор 4 работает в нормальном активном режиме, но ток через него практически отсутствует (Ц-0), так как напряжение на р-и-р переходе эмиттер-база 1% этого транзистора равно напряжению иеящу коллектором и эмиттере насыщенного транзистора 3 OY, цосг f меньше граничного напряжения отпирания р -vi-рперехода Транзистор 7 практически работает в нормальном активном режиме (в режи1ле на границе насыщения напряженке на р-м-рпереходе база-коллектор этого транзистора равно U , Upf, гр ). Транзистор 21 работает в режиме насыщения, а транзистор 22 работает в нормальном активном режиме, но ток через него отсутствует () так как напряжение этого транзистора равно напряжению и((цо насыщенного транзистора, 8. Таким образом, практически весь ток считывания 1 из разрядной шины 18 протекает через. насыщенный транзистор 8, а ток.:считывания из разрядной шины 17 распределяется между транзистором 7, работающим в нормальном активном режиме, и насыщенным транзистором 21. Полезный сигнал считывания информации (разность потенциалов разрядных шин AUpuj) возникает за счет разности токов эмиттерных диодов (модель типа Эберса-Молла) инжекционных р-п-р транзисторов 7 и 8 (эффект Эрли) и равен I - в о /1 J 4-cL lo где -j-- температурный потешдаалу | и - нормальный коэффициент ления по току г1-р-и транзисторов в схеме включения с общей базой) olRolP.- нормальный и инверсный коэф фициенты усиления по току р-И-р транзисторов в сх.еме включения с общей базой; - - ток считывания, вытекаюидий из разрядной шины в элемент памяти;I - часть тока считывания Т , протекающая через транзистор 7, работающий в нормальном активном режиме с Из приведенного выражения и анализа работы элемента памяти следует, что полезный сигнал считывания тем больше, чем меньший ток 1 протекает через транзистор 7, работающий в нормальном активном режиме. Соответственно, если весь ток считывания 1о протекает через транзистор 7 (транзисторы 21 -и 22 отсутствуют, как в известном), то полезный сигнал считывания минимален. Введение двух транзисторов в элемент памяти позволяет увеличить полезный сигнал считывания и помехозащищенность в 510 раз. Формула изобретения Элемент памяти, содержащий четыре транзистора, базы первого и второго р -VI- р транзисторов и эьшттёры третьего и четвертого Ц -р-и транзисторов, соединены с адресной иной, коллекторы первого и третьего транзисторов соедннены н подключены к базе четвертого h-p- транзистора, а коллекторы второго и чет вертого транзисторов подключены к базе третьего vi-p-n транзистора эмиттеры первого и второго p-ti-p транзисторов соединены с первой и второй разрядннми соответственно, отличающийся тем, что с целью повышения надежнос ти элемента памяти за счёт повышег ния помехозавциценности, в него введены два p-yt- p транзистора, эмит086теры которых подключены к соответствукхцим разрЮ ным шинам, а базы и коллекторы -- к коллектору и базе третьего и четвертого it-р-И транзисторов соответственно. Источники информации, принятые во внимание при экспертизе . 1. Патент ОНА 4112511, кл. 365fl88, опублик. 1980. 2. IEEE ISSce Digest o-f Techn cal Papes. 1980, c.222 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковый элемент памяти | 1980 |

|

SU942150A1 |

| Накопитель для полупроводникового запоминающего устройства | 1980 |

|

SU955202A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Инжекционный запоминающий элемент | 1974 |

|

SU526951A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

17

Фце.

If

Авторы

Даты

1983-01-23—Публикация

1981-07-02—Подача