Изобретение относится к вычислительной технике, в частности к микропроцессорам.

Существуют микропроцессоры, например "Устройство для обработки информации" по европейской заявке N 0241946, содержащее блок выполнения команд и имеющий выводы для присоединения к системной шине блок интерфейса, входы/выходы которых соединены внутренней информационной магистралью и линией управления.

Недостатком данного микропроцессора является его ограниченная производительность в силу того, что операции обмена по системной шине производятся строго последовательно.

Задача, решаемая предлагаемым изобретением, заключается в увеличении производительности микропроцессора при сохранении возможности использования существующего программного обеспечения.

Выполнение поставленной задачи достигается тем, что в известный микропроцессор вводятся дополнительные блоки интерфейса, идентичные существующему, а также блок выбора системной шины, управляющий их работой. Выход блока выполнения команд и вход блока выбора системной шины соединены информационной магистралью, входы/выходы - линией управления, а выходы разрешения блока выбора системной шины соединены с входами разрешения блоков интерфейса. Количество блоков интерфейса соответствует числу системных шин.

Работа блока выбора системной шины основана на информации, передаваемой по информационной магистрали, чем обуславливаются различные варианты исполнения микропроцессора.

В случае, когда по информационной магистрали передаются данные о адресе, она подключается как к входу блока выбора системной шины, так и к входам блоков интерфейса, при этом данные о старших разрядах поступают только на вход блока выбора системной шины, остальная часть адреса поступает на входы блоков интерфейса и представляет собой физический адрес обращения по системной шине.

В случае, когда по информационной магистрали поступают данные о номере системной шины, в микропроцессор вводится блок регистров номера системной шины, вход/выход которого соединен информационной магистралью с входом/выходом блока выполнения команд, а выход номера информационной магистралью с входом блока выбора системной шины, вход/выход которого соединен линией управления с входом/выходом блока выполнения команд, чей выход управления соединен с входом управления блока регистров номера системной шины.

Предлагаемое решение поставленной задачи позволяет получить технический результат выражающийся в том, что благодаря наличию в микропроцессоре дополнительных блоков интерфейса имеется возможность подключения к неограниченному числу системных шин и, следовательно проводить операции обмена по ним одновременно, в параллельном режиме.

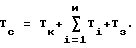

В существующих микропроцессорах, имеющих возможность подключения только к одной системной шине, операции обмена по шине происходят строго последовательно. Например при работе с блоком памяти, в частности при обработке массивов данных, для каждой команды возможно достаточно большое количество операндов, при этом суммарное время выполнения команды Tс складывается из времени выборки команды Tк, времени дешифрации кода Tд, времени выборки операндов Ti (где i - номер операнда), времени обработки операндов Tо. и времени записи результата Tз

где n - количество операндов.

Операции дешифрации кода и обработки операндов происходят внутри микропроцессора, а так как время на их исполнение значительно меньше времени операций обмена по системной шине, то в данном случае его можно не учитывать, т.е.

Таким образом, учитывая, что время выполнения операций обмена по системной шине одинаковое, т.е. Tк=Ti=Tз, а количество операндов примем например равным 10 (n=10), то

Tс = Tк+10•Ti+Tз = 12•Ti.

При использовании предлагаемого микропроцессора, каждая область памяти, в которой находится один из необходимых операндов, подключается к микропроцессору через отдельную системную шину, что создает возможность одновременной работы со всеми операндами, т.е.

при этом Tс=Tк+Ti+Tз = 3•Ti, т.е. производительность в данном случае увеличивается пропорционально числу операндов.

До пятидесяти процентов всех команд составляют команды с одним операндом типа MOV A1, A2 (операция пересылки). Для выполнения такой команды (сравнивая единичные команды) производительность существующего и предлагаемого микропроцессора одинакова и равна Tс=3•Ti, но если рассматривать последовательность из n команд, где n - число, отличное от единицы, то для существующего микропроцессора время выполнения данной последовательности ∑Tc составляет

∑Tc = 3•n•Ti,

а у предлагаемого микропроцессора, так как выборка команд происходит по одной шине, выборка операнда по другой, а запись результата по третьей, то за счет совмещения циклов обмена по системным шинам разных команд время выполнения последовательности команд составляет

∑Tc = n•Ti+2•Ti.

Например при n=10 время выполнения ∑Tc у существующего микропроцессора составляет

∑Tc = 30•Ti,

а у предлагаемого

∑Tc = 12•Ti.

На фиг.1 изображена функциональная блок-схема микропроцессора, на фиг.2 - то же при управлении посредством старших разрядов адреса, на фиг.3 - то же при управлении посредством содержимого регистров номера системной шины.

Микропроцессор 1 содержит блок выполнения команд 2, состоящий из устройства управления, операционного блока, блоков вспомогательной памяти и прерываний (на схеме не показаны), входы/выходы которого соединены внутренними информационными магистралями 3 и линиями управления 4 с входами/выходами блоков интерфейса 5, имеющих выводы (не показаны) для подключения к системным шинам 6 и входы разрешения, соединенные линиями разрешения 7 с выходами разрешения блока выбора системной шины 8 (выполненный например как комбинационная схема), входы/выходы управления и информационные входы которого соединены с входами/выходами управления и информационными выходами блока выполнения команд 2 линией управления 9 и информационной магистралью 10, которая в случае прохождения по ней информации о адресе подключается также к адресным входам блоков интерфейса 5 (см. фиг.2), а в случае передачи по ней содержимого регистров блока регистров номера системной шины 11 (см. фиг.3) информация поступает с выхода номера этого блока, информационный вход/выход и вход управления которого соединен информационной магистралью 12 и линией 13 с информационным входом/выходом и выходом управления блока выполнения команд 2.

Данное устройство работает следующим образом, после инициализации микропроцессор 1 начинает выбирать и выполнять команды с фиксированной системной шины начиная с фиксированного адреса. Блок выполнения команд 2 подает по информационной магистрали 10 и линии управления 9 информацию и сигналы управления на вход блока выбора системной шины 8, на основании которых он формирует вспомогательные сигналы управления, которые поступают по линии 9 на вход блока выполнения команд 2, номер системной шины и передает сигнал разрешения по соответствующей им линии 7 на вход разрешения соответствующего блока интерфейса 5, который, активизируясь, захватывает соответствующую системную шину 6 (если микропроцессор не работает с ней в монопольном режиме), приняв на вход по внутренней информационной магистрали 3 и линии управления 4 адрес и сигналы управления от блока выполнения команд 2 выставляет их на системную шину 6 и получает по ней информацию, которую передает по внутренней информационной магистрали 3 одновременно с сигналом синхронизации по линии 4 в блок выполнения команд 2, где она интерпретируется как код команды на основе которого вырабатываются адреса операндов текущей команды и адрес следующей команды, а также информация и сигналы управления, которые по информационной магистрали 10 и линии управления 9 передаются на вход блока выбора системной шины 8, который на их основе формирует номера системных шин операндов текущей команды и номер шины для выборки следующей команды и передает по линиям 9 и 7 вспомогательные сигналы управления на вход блока выполнения команд 2 и сигналы разрешения на входы соответствующих блоков 5, активизируя их. Активизированные блоки интерфейса 5 захватывают соответствующие системные шины 6 и после принятия на вход по внутренним информационным магистралям 3 и линиям управления 4 адресов и сигналов управления передают их на соответствующие системные шины 6, далее происходит выполнение действий над выбранными операндами, предписываемых текущей командой, дешифрация полученного кода следующей и цикл повторяется.

При использовании в качестве информации для выбора системной шины адреса обращения он передается из блока выполнения команд 2 по информационной магистрали 10 на входы блока выбора системной шины 8 и блоков интерфейса 5, при этом на вход блока выбора системной шины 8 передается только старшая часть адреса, соответствующая номеру системной шины, а на входы блоков интерфейса младшая его часть, представляя собой физический адрес обращения, дальнейшая работа микропроцессора соответствует вышеописанному.

Источником информации о номере системной шины могут служить регистры блока регистров номера системной шины 11. При этом блок выполнения команд 2 параллельно с формированием адреса в нем выдает по линии 13 сигналы управления, которые поступают на вход управления блока регистров номера системной шины 11, соответственно которым он выводит содержимое определенных регистров номера системной шины, входящих в его состав, по информационной магистрали 10 на вход блока выбора системной шины 8, куда поступают и сигналы управления по линии управления 9 с выходов управления блока выполнения команд 2. Содержимое регистров блока регистров номера системной шины 11 может изменяться и считываться при выполнении микропроцессором 1 определенных команд, при этом блок выполнения команд 2 по линии управления 13 выдает сигналы управления на вход блока регистров номера системной магистрали 11 и соответственно им по информационной магистрали 12 считывает информацию из определенного регистра этого блока или записывает в него. Далее процесс работы микропроцессора соответствует вышеописанному.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| СПОСОБ КОМПЛЕКСНОГО ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2027172C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Система обработки данных | 1980 |

|

SU1003063A1 |

Изобретение относится к вычислительной технике, в частности к микропроцессорам. Техническим результатом является повышение производительности микропроцессора за счет обеспечения возможности подключения к неограниченному числу системных шин и проведения операции обмена по ним одновременно в параллельном режиме. Микропроцессор содержит блок выполнения команд и блок интерфейса, имеющий выводы для подключения к системной шине, введены дополнительные блоки интерфейса, идентичные существующему, и блок выбора системной шины, управляющий работой блоков интерфейса. 2 з.п. ф-лы, 3 ил.

| УСТРОЙСТВО для ПРЕССОВАНИЯ ИЗДЕЛИЙ | 0 |

|

SU241946A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| US 5228130 A, 09.03.93 | |||

| US 5193199 A, 13.07.93 | |||

| US 5263141 A, 16.11.93 | |||

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

| Микропроцессорная система | 1981 |

|

SU1172455A3 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1999-02-27—Публикация

1995-07-26—Подача