Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления и др.

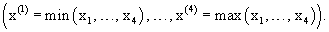

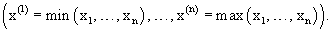

Известны реляторные селекторы (см., например, фиг.1 в описании изобретения к патенту РФ 2192045, кл. G 06 G 7/52, 2002 г.), которые обеспечивают выбор из четырех входных аналоговых сигналов х1,..., x4 сигнала x(r) любого заданного ранга r∈{1,..., 4}

К причине, препятствующей достижению указанного ниже технического результата при использовании известных реляторных селекторов, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка n входных аналоговых сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, реляторный селектор (фиг.1 в описании изобретения к патенту РФ 2192044, кл. G 06 G 7/52, 2002 г.), который содержит реляторы и обеспечивает выбор из n входных аналоговых сигналов х1,..., xn сигнала x(r) любого заданного ранга r∈{1,..., n}

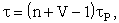

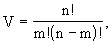

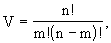

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения сигнала в прототипе определяется выражением  где τP есть время задержки релятора;

где τP есть время задержки релятора;  m=0,5(n+1) (m=0,5n) при нечетном (четном) n, n≠1 - любое натуральное число.

m=0,5(n+1) (m=0,5n) при нечетном (четном) n, n≠1 - любое натуральное число.

Техническим результатом изобретения является повышение быстродействия при сохранении функциональных возможностей прототипа.

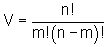

Указанный технический результат при осуществлении изобретения достигается тем, что в реляторном селекторе, содержащем реляторы, каждый из которых содержит компаратор, подключенный выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, все реляторы сгруппированы в V+1 групп так, что (V+1)-я группа содержит V-1 реляторов, в каждой группе выход предыдущего релятора соединен с первым входом последующего релятора, а выход (V-1)-го релятора (V+1)-й группы является выходом реляторного селектора, при этом  (n≠1 есть любое натуральное число, m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно), особенность заключается в том, что i-я

(n≠1 есть любое натуральное число, m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно), особенность заключается в том, что i-я  группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., V-й групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора, j-й

группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., V-й групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора, j-й  настроечный вход которого образован объединенными входами управления j-ых реляторов первой,..., V-й групп.

настроечный вход которого образован объединенными входами управления j-ых реляторов первой,..., V-й групп.

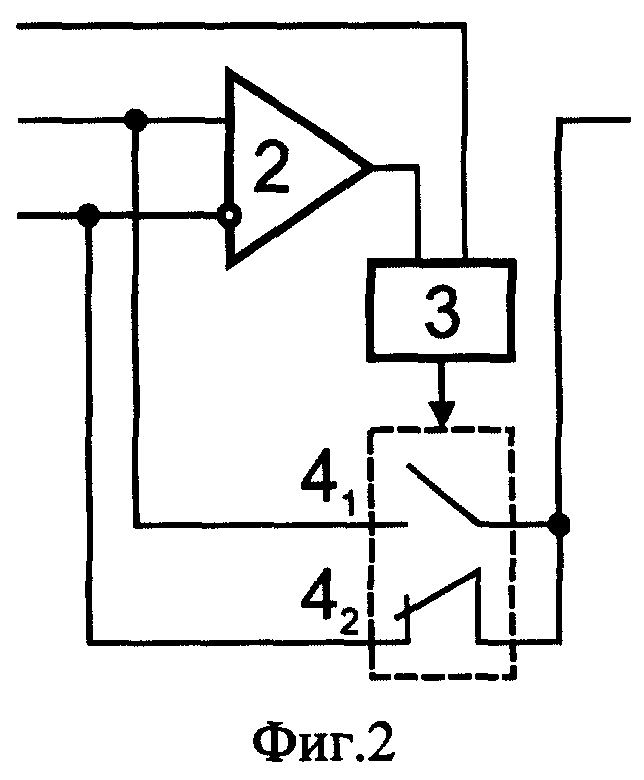

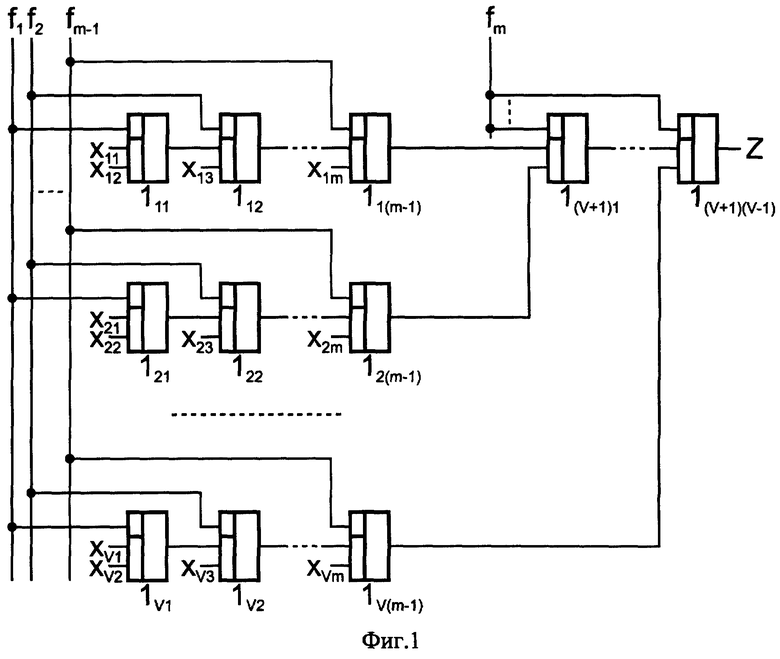

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого реляторного селектора и схема релятора, использованного при построении указанного селектора.

Реляторный селектор содержит реляторы 111,..., 1(V+1)(V-1), где  n≠1 есть любое натуральное число, m=0,5(n+1) (m=0,5n) при нечетном (четном) n. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора 2, присоединенные соответственно к входам ключей 41 и 42. Все реляторы сгруппированы в V+1 групп так, что i-я

n≠1 есть любое натуральное число, m=0,5(n+1) (m=0,5n) при нечетном (четном) n. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора 2, присоединенные соответственно к входам ключей 41 и 42. Все реляторы сгруппированы в V+1 групп так, что i-я  и (V+1)-я группы содержат соответственно реляторы 1i1,..., 1i(m-1) и 1(V+1)1,..., 1(V+1)(V-1), в каждой группе выход предыдущего релятора подключен к первому входу последующего релятора, а выход релятора 11(m-1) и выходы реляторов 12(m-1),..., 1V(m-1) соединены соответственно с первым входом релятора 1(V+1)1 и вторыми входами реляторов 1(V+1)1,..., 1(V+1)(V-1), подключенных входами управления к m-му настроечному входу реляторного селектора, выход и j-й

и (V+1)-я группы содержат соответственно реляторы 1i1,..., 1i(m-1) и 1(V+1)1,..., 1(V+1)(V-1), в каждой группе выход предыдущего релятора подключен к первому входу последующего релятора, а выход релятора 11(m-1) и выходы реляторов 12(m-1),..., 1V(m-1) соединены соответственно с первым входом релятора 1(V+1)1 и вторыми входами реляторов 1(V+1)1,..., 1(V+1)(V-1), подключенных входами управления к m-му настроечному входу реляторного селектора, выход и j-й  настроечный вход которого образованы соответственно выходом релятора 1(V+1)(V-1) и объединенными входами управления реляторов 11j,..., 1Vj.

настроечный вход которого образованы соответственно выходом релятора 1(V+1)(V-1) и объединенными входами управления реляторов 11j,..., 1Vj.

Работа предлагаемого реляторного селектора осуществляется следующим образом. На его первом,..., m-ом настроечных входах фиксируются соответственно необходимые управляющие сигналы f1,..., fm∈{0,1} (m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно, n≠1 - любое натуральное число). Когда n>2, на первый вход релятора 1i1, вторые входы реляторов 1i1,..., 1i(m-1) подается соответственно неповторяющийся набор xi1,..., хim входных аналоговых сигналов - напряжений (xi1,..., хim∈{х1,..., xn}, i1≠...≠im), причем неповторяющиеся наборы x11,..., x1m-xV1,..., xVm должны быть сформированы с учетом того, что подмножества {x1u,..., x1m}-{xNu,..., xNm}

подается соответственно неповторяющийся набор xi1,..., хim входных аналоговых сигналов - напряжений (xi1,..., хim∈{х1,..., xn}, i1≠...≠im), причем неповторяющиеся наборы x11,..., x1m-xV1,..., xVm должны быть сформированы с учетом того, что подмножества {x1u,..., x1m}-{xNu,..., xNm}

- число сочетаний из n по m+1-u) есть сочетания из n переменных (сигналов) x1,..., xn по m+1-u. Примеры упомянутых наборов при n=5 приведены в таблице.

- число сочетаний из n по m+1-u) есть сочетания из n переменных (сигналов) x1,..., xn по m+1-u. Примеры упомянутых наборов при n=5 приведены в таблице.

Когда n=2, имеем m=1, V=2 и неповторяющиеся входные аналоговые сигналы х11, х21∈{х1, x2} подаются соответственно на первый, второй входы единственного релятора 131. Если на входе управления релятора присутствует логический "0" (логическая "1") и сигнал на его первом входе больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут (разомкнут) либо разомкнут (замкнут), а ключ 42 соответственно разомкнут (замкнут) либо замкнут (разомкнут). Следовательно, если на входе управления релятора присутствует логический "0" (логическая "1"), то этот релятор будет выделять на своем выходе наибольший (наименьший) из сигналов, действующих на его первом и втором входах. Таким образом, сигнал на выходе предлагаемого реляторного селектора определяется выражением

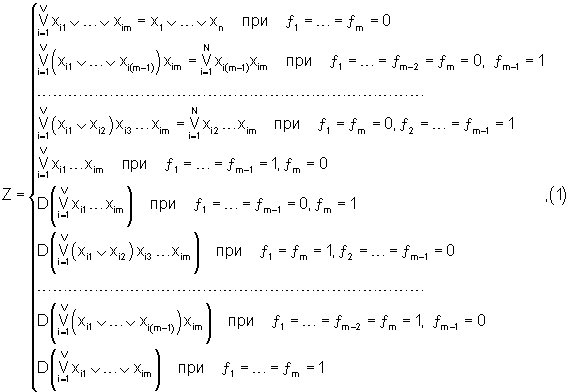

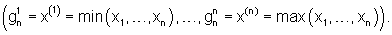

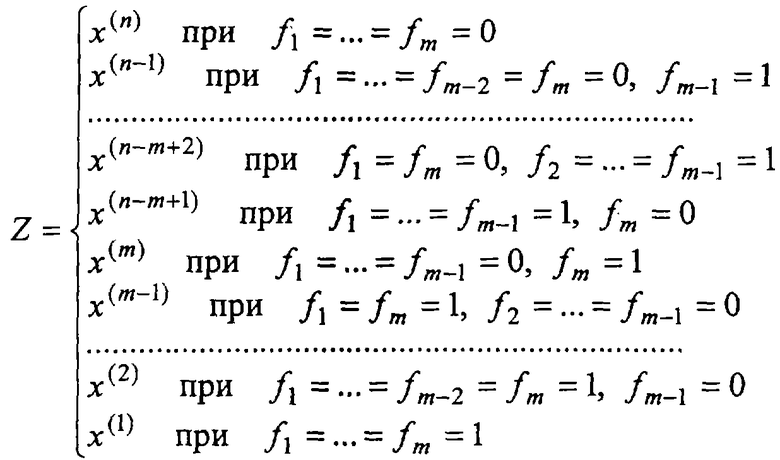

где символами ∨ и · обозначены соответственно операции max и min (базовые операции бесконечнозначной логики); D() есть оператор замены всех операций max и min соответственно на операции min и max. Логическая формула в k-й

где символами ∨ и · обозначены соответственно операции max и min (базовые операции бесконечнозначной логики); D() есть оператор замены всех операций max и min соответственно на операции min и max. Логическая формула в k-й  сверху строке выражения (1) является при k=n-r+1 частной реализацией поисковой функции

сверху строке выражения (1) является при k=n-r+1 частной реализацией поисковой функции  (функция (6.7) на стр.117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г. - Л1), которая реализует алгоритм поиска (выбора) элемента х(r) заданного ранга r∈{1,..., n} в множестве {х1,..., хn}

(функция (6.7) на стр.117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г. - Л1), которая реализует алгоритм поиска (выбора) элемента х(r) заданного ранга r∈{1,..., n} в множестве {х1,..., хn}  Кроме того, из анализа дизъюнктивной и конъюнктивной нормальных форм (см. формулы (2.26) и (2.27) на стр.24 в Л1) поисковой функции следует равенство

Кроме того, из анализа дизъюнктивной и конъюнктивной нормальных форм (см. формулы (2.26) и (2.27) на стр.24 в Л1) поисковой функции следует равенство С учетом указанного, на выходе селектора (фиг.1) окончательно имеем

С учетом указанного, на выходе селектора (фиг.1) окончательно имеем

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый реляторный селектор обеспечивает выбор из n входных аналоговых сигналов х1,..., хn сигнала х(r) любого заданного ранга r∈{1,..., n} и обладает более высоким по сравнению с прототипом быстродействием, так как максимальное время задержки распространения сигнала в предлагаемом реляторном селекторе определяется выражением τ=(m+V-2)τP, где τP есть время задержки релятора; m=0,5(n+1) (m=0,5n) при нечетном (четном) n, n≠1 - любое натуральное число;

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2001 |

|

RU2192044C1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ ИДЕНТИФИКАЦИИ ИНФОРМАЦИОННОГО СИГНАЛА ПО ПРИЗНАКУ ЕГО ПРИНАДЛЕЖНОСТИ К СУБМЕДИАННОМУ ИЛИ СУПРАМЕДИАННОМУ ПОДМНОЖЕСТВАМ МАССИВА АНАЛОГОВЫХ СИГНАЛОВ | 1998 |

|

RU2169945C2 |

| РАНГОВЫЙ СЕЛЕКТОР | 2004 |

|

RU2262740C1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ СУБМЕДИАННОГО И СУПРАМЕДИАННОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОЙ ПЕРЕМЕННОЙ | 1999 |

|

RU2177642C2 |

| РЕЛЯТОРНЫЙ ИДЕНТИФИКАТОР | 2001 |

|

RU2194304C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2248042C1 |

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2000 |

|

RU2181502C2 |

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2240597C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2005 |

|

RU2294008C1 |

| РЕЛЯТОРНЫЙ КОММУТАТОР АНАЛОГОВЫХ СИГНАЛОВ С АДРЕСНЫМ УПРАВЛЕНИЕМ | 2004 |

|

RU2256220C1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения функциональных узлов аналоговых вычислительных машин. Достигаемый технический результат - повышение быстродействия. Реляторный селектор содержит реляторы, каждый из которых содержит компаратор, булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и размыкающий и замыкающий ключи, все реляторы сгруппированы в V+1 групп так, что (V+1)-я группа содержит V-1 реляторов, в каждой группе выход предыдущего релятора соединен с первым входом последующего релятора, а выход (V-1)-го релятора (V+1)-й группы является выходом реляторного селектора, при этом  (n≠1 есть любое натуральное число, m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно), i-я

(n≠1 есть любое натуральное число, m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно), i-я  группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., V-й групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора. 2 ил.

группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., V-й групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора. 2 ил.

Реляторный селектор, содержащий реляторы, каждый из которых содержит компаратор, подключенный выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, все реляторы сгруппированы в V+1 групп так, что (V+1)-я группа содержит V-1 реляторов, в каждой группе выход предыдущего релятора соединен с первым входом последующего релятора, а выход (V-1)-го релятора (V+1)-й группы является выходом реляторного селектора, при этом

n≠1 есть любое натуральное число, m=0,5(n+1) либо m=0,5n при нечетном либо четном n соответственно,

отличающийся тем, что i-я  группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., пятой групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора, j-й

группа содержит m-1 реляторов, причем выход (m-1)-го релятора первой и выходы (m-1)-ых реляторов второй,..., пятой групп соединены соответственно с первым входом первого и вторыми входами первого,..., (V-1)-го реляторов (V+1)-й группы, подключенных входами управления к m-му настроечному входу реляторного селектора, j-й  настроечный вход которого образован объединенными входами управления j-х реляторов первой,..., пятой групп.

настроечный вход которого образован объединенными входами управления j-х реляторов первой,..., пятой групп.

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2001 |

|

RU2192044C1 |

| Способ метки скота | 1932 |

|

SU31528A1 |

| Приспособление для снятия дрезины с рельсов | 1932 |

|

SU31466A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2007-02-27—Публикация

2005-11-03—Подача