Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации преобразователя.

Известен функциональный преобразователь (авт.св. №591861 СССР, 1976 г.), содержащий сумматоры-вычитатели, регистры, блок анализа и блок управления.

Его недостатком являются ограниченные функциональные возможности, так как он предназначен для вычисления только двух функций.

Наиболее близким к заявляемому является функциональный преобразователь (авт.св. 960807 СССР, 1982 г.), содержащий пять (от первого до пятого) сумматоров-вычитателей, первый и второй регистры, блок анализа, блок управления, блок дополнения, два информационных входа X и Y, четыре выхода (по числу реализуемых функций). Выход первого сумматора-вычитателя соединен с входом блока анализа, первый выход которого подключен к входу блока управления. Первый выход блока управления соединен с первыми входами всех сумматоров-вычитателей, а второй выход - с первыми входами обоих регистров. Выход первого регистра соединен с третьим входом первого сумматора-вычитателя, выход второго регистра - с третьими входами второго, третьего и четвертого сумматоров-вычитателей. Вторые входы четвертого и пятого сумматора-вычитателя соединены с выходом блока дополнения, вход которого связан со входом X. Входы X и Y, кроме того, связаны со вторыми входами первого и второго регистров и со вторыми входами первого, второго, третьего и суммматора-вычитателя соответственно.

Его недостатком является также ограниченный круг реализуемых функций. Из четырех - одна тривиальная  , которая после преобразования равна = у-х, а вторая

, которая после преобразования равна = у-х, а вторая  известная ранее

известная ранее  , взятая с отрицательным знаком.

, взятая с отрицательным знаком.

Задача изобретения - расширение класса реализуемых функций.

Технический результат - возможность реализации дополнительных функции  и

и  , где X, Y, S, W - аргументы этих функции, без увеличения аппаратуры и при неснижении точности и быстродействия преобразователя.

, где X, Y, S, W - аргументы этих функции, без увеличения аппаратуры и при неснижении точности и быстродействия преобразователя.

Технический результат достигается за счет того, что дополнительно включается третий S и четвертый W информационные входы, а также третий регистр, причем первый X информационный вход связан с входом первого регистра и со вторым входом пятого сумматора-вычитателя, третий информационный вход S со вторыми входами второго и третьего сумматора-вычитателя, четвертый W - информационный вход связан с входом второго регистра, второй Y информационный вход связан с входом третьего регистра и со вторым входом первого сумматора-вычитателя, кроме того, второй выход блока управления связан со вторым входом третьего регистра, а выход третьего регистра - с третьими входами четвертого и пятого сумматоров-вычитателей.

Введение дополнительно двух информационных входов, замена блока дополнения на регистр и их связей с остальными блоками преобразователя позволили расширить класс решаемых задач.

Это является новым техническим решением в области цифровых вычислений, поскольку результаты проведенного авторами анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенный функциональный преобразователь промышленно применим, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

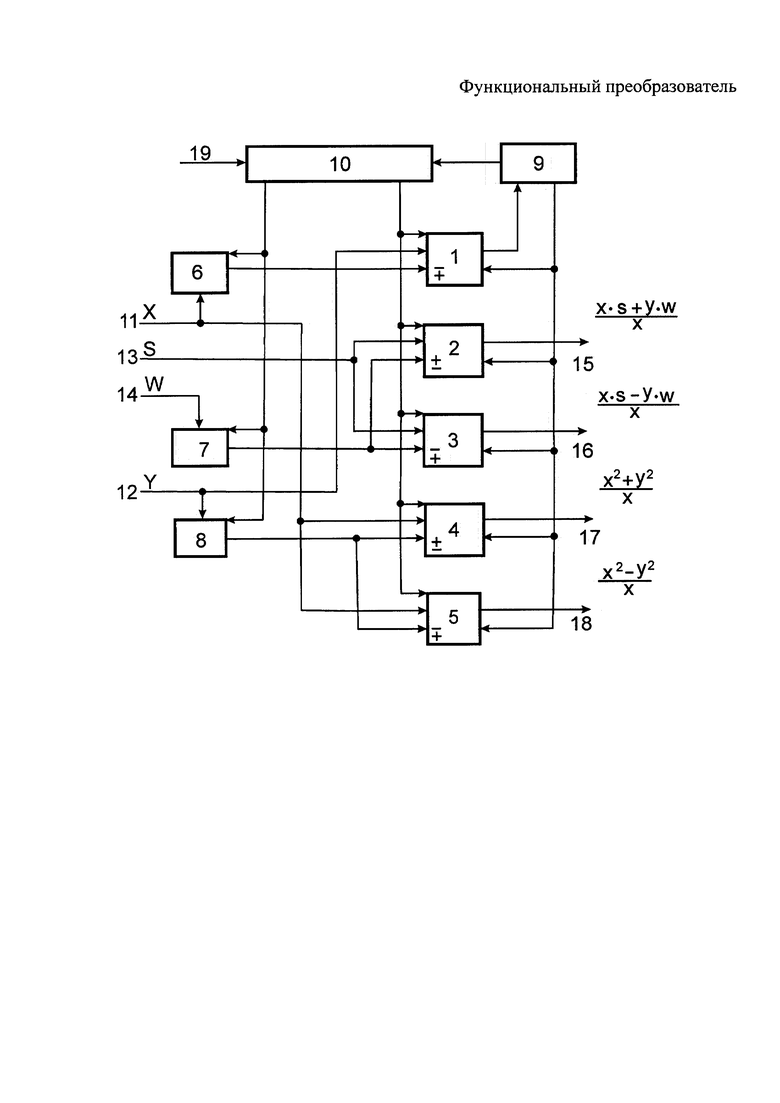

На фиг. представлена структурная схема функционального преобразователя. Он содержит пять (от первого до пятого) сумматоров-вычитателей 1, 2, 3, 4, 5, первый и второй и третий регистры 6, 7, 8, блок анализа 9, блок управления 10, четыре информационных входа 11(Х), 12(Y), 13(S), 14(W) и столько же выходов 15, 16, 17, 18. Кроме того есть еще вход запуска 19 всего преобразователя в работу.

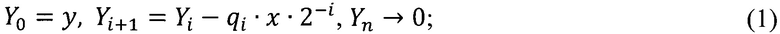

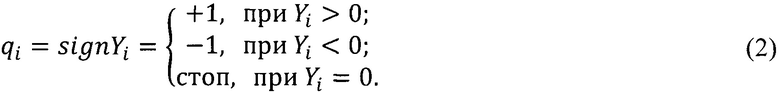

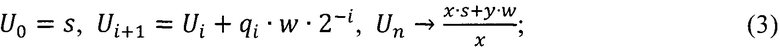

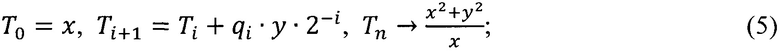

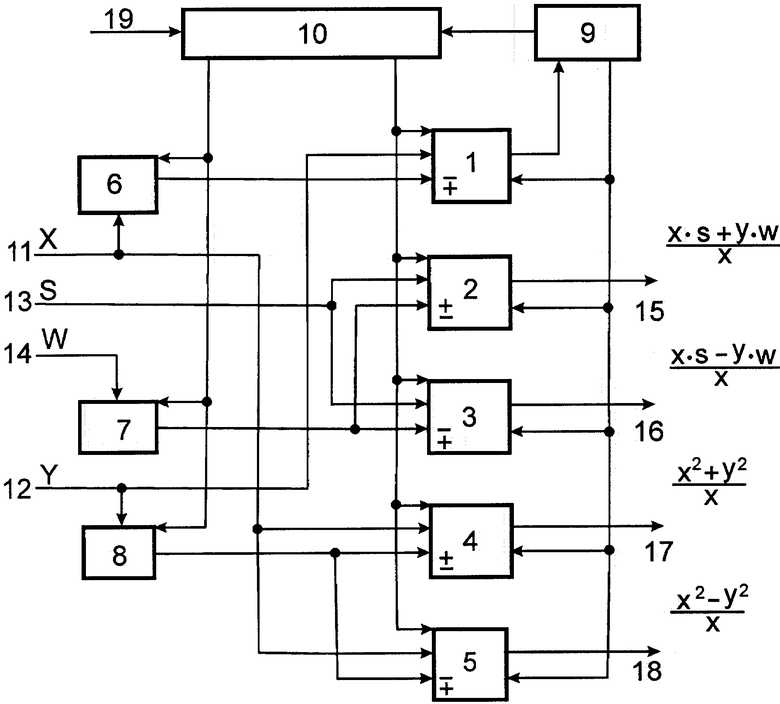

Вычисление функций в данном функциональном преобразователе основано на одновременном решении системы разностно-итерационных соотношений (алгоритм вычисления) в итерационном процессе.

где i=0, 1, …, n-1 - номер итерации, n - число двоичных разрядов аргументов.

Рекуррентные соотношения предложенного алгоритма обладают групповыми свойствами и вычисляются одновременно в одном итерационном цикле, причем каждое соотношение может вычисляться либо за один такт, либо за n+m тактов, где т=[log2n]int - число дополнительных защитных разрядов регистров и сумматоров-вычитателей для компенсации погрешности от усечения чисел при их сдвиге. Соотношение YI реализуется в сумматоре-вычитателе 1, соотношение Ui - в сумматоре-вычитателе 2, соотношение (4) - в сумматоре-вычитателе 3 выход 16, соотношение (5) - в сумматоре-вычитателе 4 выход 17, соотношение (6) - в сумматоре-вычитателе 5 выход 18. Логическое уравнение Yi> (<)0 решается в блоке 9 анализа, где формируются сигналы Yi>0 (первый выход) qi<0 (второй выход). Величины х⋅2-i и у⋅2-i получаются на выходах регистров 6 и 8 соответственно после окончания итерации, причем перед первой итерацией сдвиг не производится.

Вычисление указанных функций в данном функциональном преобразователе осуществляется следующим образом.

Первоначально в регистр 6, в сумматоры-вычитатели 4 и 5 заносится код аргумента X, а в регистр 8 и в сумматор-вычитатель 1 заносится код аргумента Y. Кроме того, в регистр 7 заносится аргумент W, а аргумент S заносится в сумматоры-вычитатели 2 и 3. По стартовому сигналу с входа 19 включается блок 10 управления и на первом и втором выходах появляется последовательности тактовых импульсов для продвижения содержимых регистров 6, 7 и 8 на соответствующие входы сумматоров-вычитателей 1-5 и для продвижения информации в последних.

При qi=+1 в сумматорах-вычитателях 1, 3 и 5 выполняется вычитание, а в сумматорах-вычитателях 2 и 4 - сложение. При qi=-1 режим работы меняется на обратный.

После выполнения определенного числа итераций при равенстве нулю содержания сумматора-вычитателя 1 процесс вычисления закончен. При этом в сумматоре-вычитателе 4 содержится значение функции  , в сумматоре-вычитателе 5 - значение функции

, в сумматоре-вычитателе 5 - значение функции  , в сумматоре-вычитателе 2 - значение функции

, в сумматоре-вычитателе 2 - значение функции  , а в сумматоре-вычитателе 3 - значение функции

, а в сумматоре-вычитателе 3 - значение функции  .

.

Максимальное время вычисления четырех функций для параллельного решения каждого соотношения алгоритма не увеличивается по сравнению с прототипом.

В общем случае погрешность вычисления указанных функций определяется длиной разрядной сетки регистров и сумматоров-вычитателей, и в случае использования дополнительных разрядов m всегда меньше единицы последнего младшего разряда n, то есть не увеличивается в сравнении с прототипом. Использование вместо блока дополнения третьего регистра не приводит к увеличению аппаратных затрат при осуществлении изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 2017 |

|

RU2642381C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Функциональный преобразователь | 1980 |

|

SU960807A2 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации. Технический результат заключается в расширении класса реализуемых функций. Функциональный преобразователь содержит пять сумматоров-вычитателей, три регистра, блок анализа, блок управления, по четыре входа и выхода (по числу аргументов и функций от них), при этом выход первого сумматора-вычитателя связан с блоком анализа, выходы которого - с блоком управления и входами режима работы сумматоров-вычитателей и регистров. 1 ил.

Функциональный преобразователь, содержащий первый, второй, третий, четвертый и пятый сумматоры-вычитатели, первый и второй регистры, блок анализа, блок управления, блок дополнения, первый X и второй Y два информационных входа, четыре выхода, причем выход первого сумматора-вычитателя соединен со входом блока анализа, первый выход которого подключен к блоку управления, первый выход которого соединен с первыми входами всех сумматоров-вычитателей, а второй выход - с первыми входами регистров, кроме того, выход первого регистра соединен с третьими входами первого сумматора-вычитателя, выход второго регистра - с третьими выходами второго, третьего сумматоров-вычитателей, отличающийся тем, что дополнительно включает третий S и четвертый W информационных входа, а также третий регистр, причем первый X информационный вход связан с входом первого регистра и со вторым входом пятого сумматора-вычитателя, третий информационный вход S связан со вторыми входами второго и третьего сумматора-вычитателя, четвертый W информационный вход связан с входом второго регистра, второй Y информационный вход связан с входом третьего регистра и со вторым входом первого сумматора-вычитателя, кроме того, второй выход блока управления связан со вторым входом третьего регистра, а выход третьего регистра - с третьим входом четвертого и пятого сумматоров-вычитателей.

| Функциональный преобразователь | 1976 |

|

SU591861A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU607223A1 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744590A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Функциональный преобразователь | 1980 |

|

SU960807A2 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| Огнетушитель | 0 |

|

SU91A1 |

| Огнетушитель | 0 |

|

SU91A1 |

| US 4525795 A1, 25.06.1985 | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

Авторы

Даты

2018-04-05—Публикация

2017-04-06—Подача