Изобретение относится к вычислительной технике и может быть применено, например, в специализированных вычислительных блоках.

Известны устройства для вычисления функции  , содержащие регистры операндов, сумматоры, счетчики, коммутаторы, логические элементы [А.с. 404082 СССР, 1971].

, содержащие регистры операндов, сумматоры, счетчики, коммутаторы, логические элементы [А.с. 404082 СССР, 1971].

Недостатком известного устройства являются значительные аппаратные затраты.

Наиболее близким к предлагаемому является устройство для вычисления функции  [А.с. 752332 СССР, 1980], содержащее регистр первого операнда, счетчик второго операнда, первый счетчик порядка, блок управления, второй счетчик порядка и дешифратор, входы которого подключены к разрядным выходам первого счетчика порядка, а выходы - к разрядным входам счетчика второго операнда, выход переполнения которого подключен к входу первого счетчика порядка, установочные входы и выходы которого соединены соответственно с выходами и входами второго счетчика порядка, выход и вход знакового разряда которого подключены к первому управляющему входу и выходу блока управления, подключенного также к входу первого счетчика порядка, разрядные входы регистра первого операнда соединены с соответствующими выходами счетчика второго операнда, выход нулевого разряда которого и выход первого разряда регистра первого операнда соединены с соответствующими входами блока управления, второй управляющий выход которого подключен к входам регистра первого операнда и счетчика второго операнда, установочные входы которого подключены к выходам регистра первого операнда.

[А.с. 752332 СССР, 1980], содержащее регистр первого операнда, счетчик второго операнда, первый счетчик порядка, блок управления, второй счетчик порядка и дешифратор, входы которого подключены к разрядным выходам первого счетчика порядка, а выходы - к разрядным входам счетчика второго операнда, выход переполнения которого подключен к входу первого счетчика порядка, установочные входы и выходы которого соединены соответственно с выходами и входами второго счетчика порядка, выход и вход знакового разряда которого подключены к первому управляющему входу и выходу блока управления, подключенного также к входу первого счетчика порядка, разрядные входы регистра первого операнда соединены с соответствующими выходами счетчика второго операнда, выход нулевого разряда которого и выход первого разряда регистра первого операнда соединены с соответствующими входами блока управления, второй управляющий выход которого подключен к входам регистра первого операнда и счетчика второго операнда, установочные входы которого подключены к выходам регистра первого операнда.

Недостатком этого устройства является его низкое быстродействие.

Задачей настоящего изобретения является совершенствование устройства для вычисления функции  .

.

Технический результат - возможность сокращения времени получения результата вычислений.

Технический результат достигается тем, что в известное устройство для вычисления функции  , содержащее регистр первого операнда, первый и второй счетчики порядка, счетчик второго операнда, дешифратор, блок управления, дополнительно вводятся два (

, содержащее регистр первого операнда, первый и второй счетчики порядка, счетчик второго операнда, дешифратор, блок управления, дополнительно вводятся два ( )-входовые логические элементы И-НЕ, соединенные между собой по схеме "монтажное ИЛИ", общий выход которых связан с блоком управления, причем

)-входовые логические элементы И-НЕ, соединенные между собой по схеме "монтажное ИЛИ", общий выход которых связан с блоком управления, причем  входов каждой из них подключены к

входов каждой из них подключены к  старшим разрядам регистра первого операнда и к

старшим разрядам регистра первого операнда и к  старшим разрядам счетчика второго операнда соответственно (где n - разрядность операндов).

старшим разрядам счетчика второго операнда соответственно (где n - разрядность операндов).

Введение дополнительно двух логических элементов И-НЕ и их связей с другими блоками устройства позволило сократить время получения результата вычислений. Это является новым техническим решением в технике цифровых вычислений, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют сократить время получения результата вычислений.

Предложенное устройство для вычисления функций промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

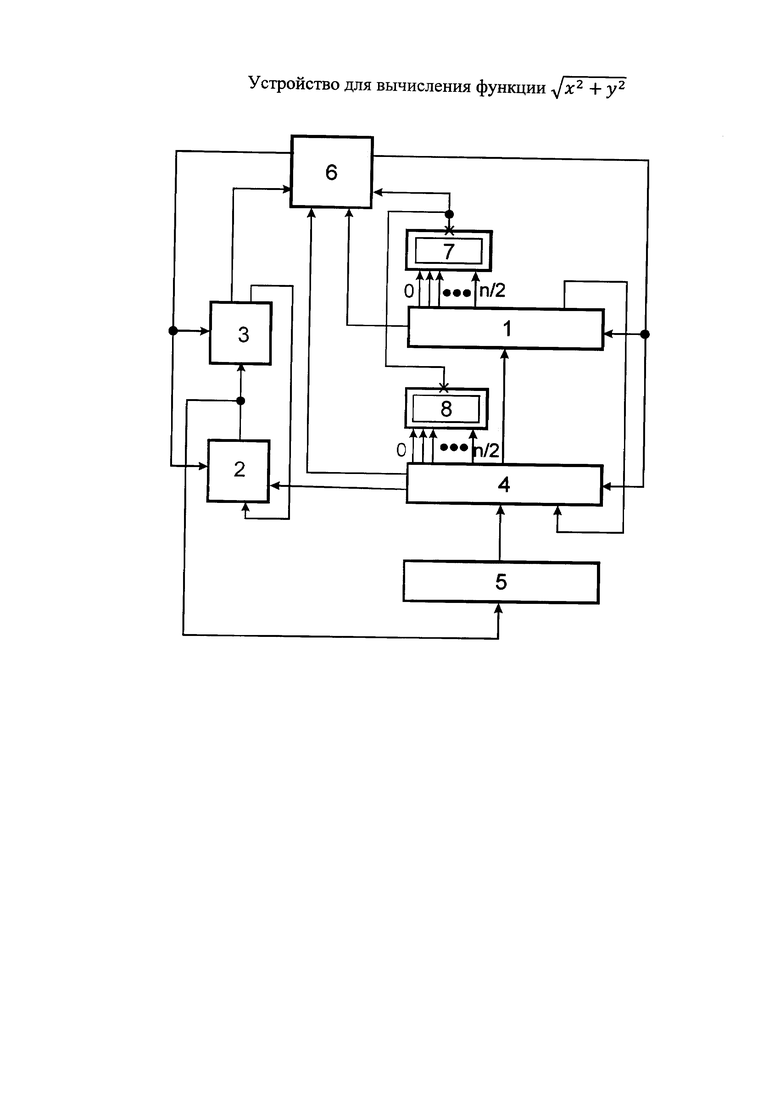

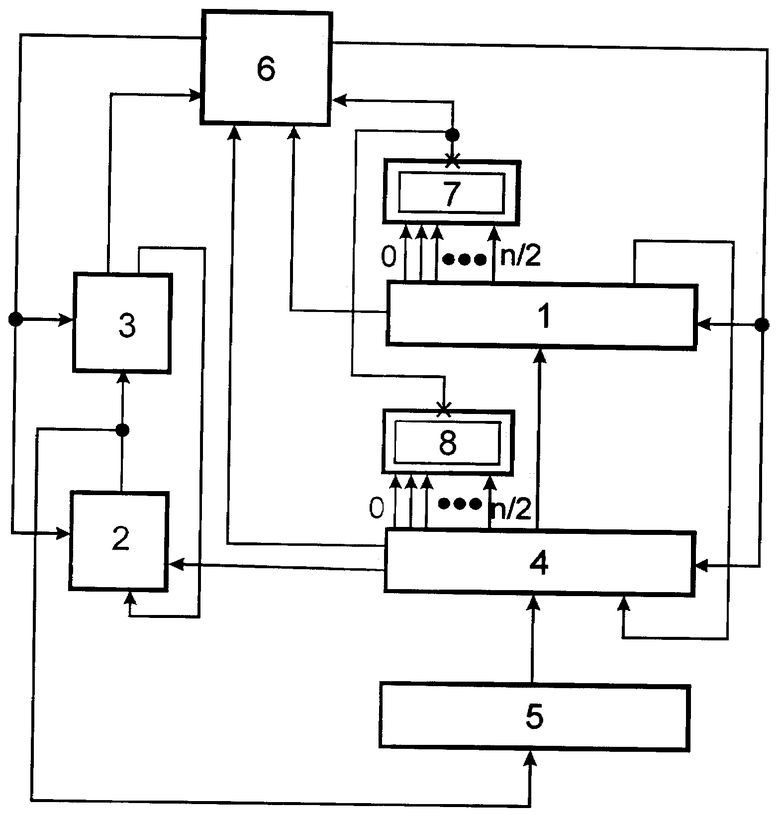

На чертеже представлена блок-схема устройства.

Устройство содержит регистр 1 первого операнда, первый 2 и второй 3 счетчики порядка, счетчик 4 второго операнда, дешифратор 5, блок 6 управления и два логических элемента И-НЕ 7, 8, соединенных друг с другом по схеме "монтажное ИЛИ".

Многоразрядный выход первого 2 счетчика порядка подключен ко входам дешифратора 5, каждый i-й выход которого (i=0, 1, 2, …, n-1, первыми будем считать старшие разряды) связан со счетным входом i-го разряда счетчика второго операнда 4, выход нулевого разряда которого соединен со счетным входом младшего разряда первого 2 счетчика порядка, выходы первого 2 счетчика порядка со сдвигом на один разряд влево соединены с установочными входами второго 3 счетчика порядка, выходы которого со сдвигом на один разряд влево соединены с установочными входами первого 2 счетчика порядка. Выходы регистра 1 первого операнда соединены с установочными входами счетчика 4 второго операнда, выходы которого со сдвигом на n разрядов вправо соединены со входами регистра 1 первого операнда. Кроме того, устройство содержит блок 6 управления, связанный с выходами нулевого и первого разрядов счетчика 4 второго операнда, регистра 1 первого операнда и второго 3 счетчика порядка, с управляющими входами счетчиков 4, 2, 3 и регистра 1 первого операнда. Кроме того,  входов каждого из элементов И-НЕ 7 и 8 соединены с

входов каждого из элементов И-НЕ 7 и 8 соединены с  старшими разрядами регистра 1 первого и счетчика 4 второго операндов соответственно. Общий выход элементов И-НЕ 7 и 8 связан со входом блока 6 управления.

старшими разрядами регистра 1 первого и счетчика 4 второго операндов соответственно. Общий выход элементов И-НЕ 7 и 8 связан со входом блока 6 управления.

Устройство работает следующим образом. В исходном состоянии в счетчиках 4, 2, 3 и регистре 1 первого операнда записаны нули. В первом цикле вычисления блок 6 управления подключает к управляющему входу счетчика 4 второго операнда входную шину, по которой в устройство поступают импульсы в количестве, равном х. По каждому управляющему сигналу производится прибавление единицы в i-й разряд счетчика 4 второго операнда, где i - число, поступающее на входы дешифратора 5 с первого 2 счетчика порядка. Когда в счетчике 4 второго операнда в нулевом разряде образуется единица, то последующие счетные сигналы, поступающие на вход этого разряда, не изменяя состояния последнего, проходят на вход младшего разряда первого 2 счетчика порядка и второго 3 счетчика порядка. Цикл заканчивается по сигналу от источника информации об окончании передачи кода х. В результате выполнения первого цикла на счетчике 4 второго операнда получается мантисса mx, а на первом 2 счетчике порядка - порядок рх числа, записанного в форме с плавающей запятой. (Цифра, стоящая в i-м разряде счетчика 4 второго операнда имеет вес 2-i). Во втором цикле по сигналу блока 6 управления осуществляется передача содержимого счетчика 4 второго операнда в регистр 1 первого операнда (со сдвигом на n разрядов вправо) и одновременно с этим - передача содержимого регистра 1 первого операнда в счетчик 4 второго операнда, а второй 3 счетчик порядка устанавливается в состояние - n.

В третьем цикле аналогично первому на управляющий вход счетчика 4 второго операнда поступает в число-импульсном коде операнд y. Если порядок числа y превосходит порядок числа х на величину S (S ∈ {0, 1, 2, 3, …, n}), то в счетчике 4 второго операнда S раз будет наблюдаться переполнение и, следовательно, в первый 2 счетчик порядка и второй 3 счетчик порядка прибавится по S единиц. Цикл заканчивается по сигналу от источника информации об окончании передачи кода y. В результате выполнения третьего цикла на первом 2 счетчике порядка получаем Py=Px+S, а на счетчике 4 второго операнда - мантиссу my числа y.

В четвертом цикле блок 6 управления выдает серию сигналов, по каждому из которых осуществляется сдвиг содержимого регистра 1 первого операнда и прибавление единицы во второй 3 счетчик порядка. Цикл заканчивается по достижении вторым 3 счетчиком порядка состояния "0". Если при этом в нулевом и первом разрядах регистра 1 первого операнда записаны единицы или в нулевом разряде счетчика 4 второго операнда записан ноль, то выполняется пятый цикл, в противном случае устройство переходит к выполнению шестого цикла.

Пятый цикл вычисления полностью аналогичен второму.

В шестом цикле блок 6 управления вырабатывает серию сигналов, по каждому из которых осуществляется сдвиг содержимого регистра 1 первого операнда и прибавление "1" во второй 3 счетчик порядка. Цикл заканчивается, когда в нулевом разряде регистра 1 первого операнда появится единица, т.е. когда выполняется нормализация мантиссы числа в регистре 1 первого операнда.

При этом во втором 3 счетчике порядка получают код  .

.

В седьмом цикле осуществляется запись во втором 3 счетчике порядка со сдвигом влево на один разряд содержимого первого 2 счетчика порядка и запись в первый 2 счетчик порядка со сдвигом влево на один разряд содержимого второго 3 счетчика порядка. Содержимое первого разряда счетчика 4 второго операнда заносится в младший разряд первого 2 счетчика порядка и второго 3 счетчика порядка. В нулевой и первый разряды счетчика 4 второго операнда заносятся соответственно "0" и "1". Если в первом разряде регистра 1 первого операнда записана "1", то в регистре 1 первого операнда выполняется сдвиг на один разряд, в противном случае в нулевой и первый разряды этого регистра заносятся собственно "0" и "1".

Седьмой цикл выполняется по двум вариантам:

1 вариант. Если все  старших разрядов регистра 1 первого операнда или счетчика 4 второго операнда содержат нули, то на выходе логических элементов И-НЕ 7, 8 возникнет сигнал "0". Он передается в блок 6 управления, который прекращает дальнейшие вычисления. Устройство выдает результат одного из операндов, не равного нулю, в качестве мантиссы, и их общий порядок в качестве порядка результата. Это математически базируется на том, что двоичное число с

старших разрядов регистра 1 первого операнда или счетчика 4 второго операнда содержат нули, то на выходе логических элементов И-НЕ 7, 8 возникнет сигнал "0". Он передается в блок 6 управления, который прекращает дальнейшие вычисления. Устройство выдает результат одного из операндов, не равного нулю, в качестве мантиссы, и их общий порядок в качестве порядка результата. Это математически базируется на том, что двоичное число с  нулями в старшей части двоичного числа при возведении его в квадрат превращается в двоичное число с n нулями в своей старшей части.

нулями в старшей части двоичного числа при возведении его в квадрат превращается в двоичное число с n нулями в своей старшей части.

2 вариант. Сигнал от двух логических схем И-НЕ 7, 8 в блок 6 управления равен "1". Тогда седьмой, восьмой, девятый и десятый циклы выполняются как у прототипа, т.е. с затратой времени.

Таким образом, исключение ряда времяемких циклов при вычислении функции  создает предпосылки существенного повышения технико-экономической эффективности - быстродействия предложенного устройства.

создает предпосылки существенного повышения технико-экономической эффективности - быстродействия предложенного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для вычисления функции | 1978 |

|

SU752332A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в возможности сокращения времени для получения результата вычислений. Устройство содержит регистр первого операнда, первый и второй счетчики порядка, счетчик второго операнда, дешифратор, блок управления. Дополнительно содержит два логических элемента И-НЕ, обеспечивающие досрочное завершение вычислений, если один из операндов значительно меньше другого. 1 ил.

Устройство для вычисления функции  , содержащее регистр первого операнда, первый и второй счетчики порядка, счетчик второго операнда, дешифратор, блок управления, причем входы дешифратора подключены к разрядным выходам первого счетчика порядка, а выходы - к разрядным входам счетчика второго операнда, выход переполнения которого подключен ко входу первого счетчика порядка, установочные входы и выходы которого соединены соответственно с выходами и входами второго счетчика порядка, выход и вход знакового разряда которого подключен к первому управляющему входу и выходу блока управления, подключенного также ко входу первого счетчика порядка, разрядные входы регистра первого операнда соединены с соответствующими выходами счетчика второго операнда, выход нулевого разряда которого и выход первого разряда регистра первого операнда соединены с соответствующими входами блока управления, второй управляющий выход которого подключен ко входам регистра первого операнда и счетчика второго операнда, установочные входы которого подключены к выходам первого операнда, отличающееся тем, что дополнительно содержит два

, содержащее регистр первого операнда, первый и второй счетчики порядка, счетчик второго операнда, дешифратор, блок управления, причем входы дешифратора подключены к разрядным выходам первого счетчика порядка, а выходы - к разрядным входам счетчика второго операнда, выход переполнения которого подключен ко входу первого счетчика порядка, установочные входы и выходы которого соединены соответственно с выходами и входами второго счетчика порядка, выход и вход знакового разряда которого подключен к первому управляющему входу и выходу блока управления, подключенного также ко входу первого счетчика порядка, разрядные входы регистра первого операнда соединены с соответствующими выходами счетчика второго операнда, выход нулевого разряда которого и выход первого разряда регистра первого операнда соединены с соответствующими входами блока управления, второй управляющий выход которого подключен ко входам регистра первого операнда и счетчика второго операнда, установочные входы которого подключены к выходам первого операнда, отличающееся тем, что дополнительно содержит два  - входовые логические элементы И-НЕ, соединенные между собой по схеме "монтажное ИЛИ", общий выход которых связан с блоком управления, причем

- входовые логические элементы И-НЕ, соединенные между собой по схеме "монтажное ИЛИ", общий выход которых связан с блоком управления, причем  входов каждого из них подключены к

входов каждого из них подключены к  старшим разрядам регистра первого и к

старшим разрядам регистра первого и к  старшим разрядам счетчика второго операндов соответственно.

старшим разрядам счетчика второго операндов соответственно.

| US 3431407 A, 04.03.1969 | |||

| Штамп для гибки | 1986 |

|

SU1315079A1 |

| US 2009024777 A1, 22.01.2009 | |||

| RU 2028661 C1, 09.02.1995. | |||

Авторы

Даты

2017-10-11—Публикация

2016-11-15—Подача