Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ДОУ) с существенными различными параметрами. Особое место занимают ДОУ на основе комплементарных входных каскадов (так называемых dual-input-stage), двух токовых зеркал, согласованных с шинами положительного и отрицательного источников питания, и буферного усилителя [1-30]. ДОУ данного класса реализуются как на биполярных [1-16], так и на КМОП транзисторах [17-30]. Такая архитектура ДОУ [1-30] является основой более чем 50 серийных микросхем, выпускаемых ведущими микроэлектронными фирмами мира.

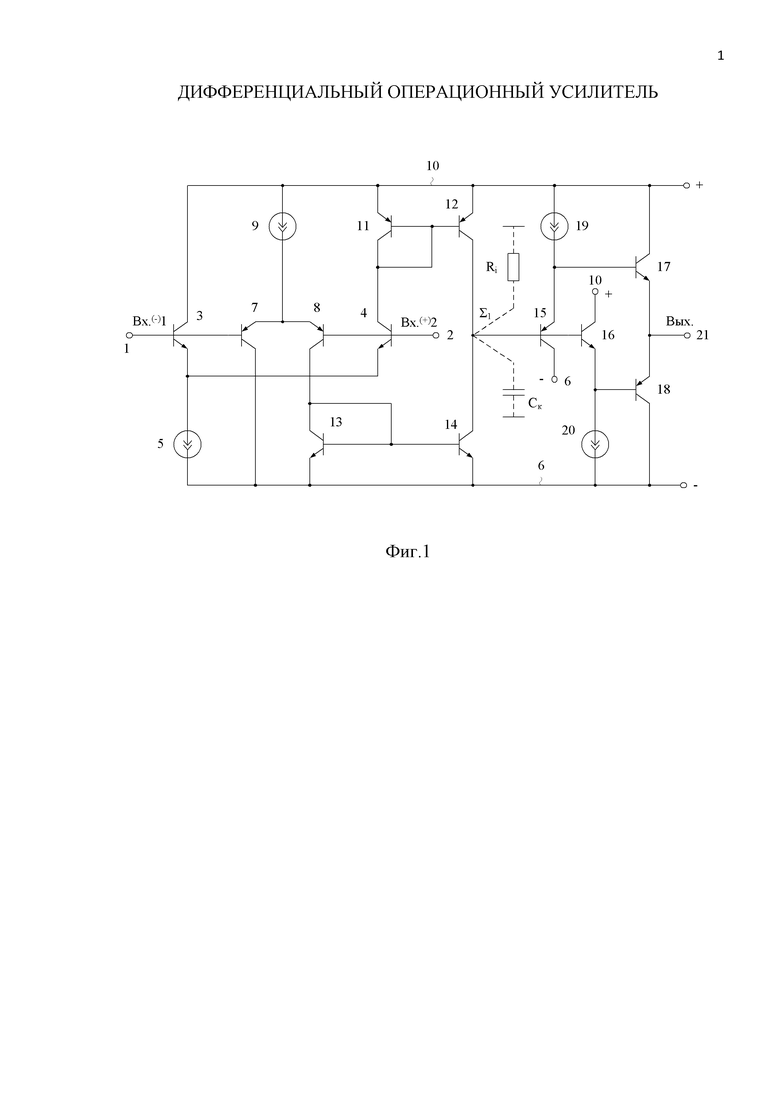

Ближайшим прототипом (фиг. 1) заявляемого устройства является ДОУ по патентной заявке US № 2005/0024140, fig. 12, 2005г. Он содержит (фиг. 1) первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, второй 4 входной транзистор, база которого подключена ко второму 2 входу устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 3 и второго 4 входных транзисторов и первой 6 шиной источника питания, третий 7 входной транзистор, база которого соединена с первым 1 входом устройства, четвертый 8 входной транзистор, база которого соединена со вторым 2 входом устройства, второй 9 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами третьего 7 и четвертого 8 входных транзисторов и второй 10 шиной источника питания, первый 11 и второй 12 входные транзисторы промежуточного каскада, базы которых объединены, эмиттеры связаны со второй 10 шиной источника питания, третий 13 и четвертый 14 входные транзисторы промежуточного каскада, базы которых объединены, а эмиттеры связаны с первой 6 шиной источника питания, коллекторы второго 12 и четвертого 14 входных транзисторов промежуточного каскада соединены друг с другом и связаны с базами первого 15 и второго 16 входных транзисторов буферного усилителя, первый 17 и второй 18 выходные транзисторы буферного усилителя, причем база первого 17 выходного транзистора буферного усилителя соединена с эмиттером первого 15 входного транзистора буферного усилителя и через третий 19 токостабилизирующий двухполюсник подключена ко второй 10 шине источника питания, база второго 18 выходного транзистора буферного усилителя соединена с эмиттером второго 16 входного транзистора буферного усилителя и через четвертый 20 токостабилизирующий двухполюсник подключена к первой 6 шине источника питания, объединенные эмиттеры первого 17 и второго 18 выходных транзисторов буферного усилителя связаны с выходом устройства 21, коллектор первого 17 выходного транзистора буферного усилителя подключен ко второй 10 шине источника питания, коллектор второго 18 выходного транзистора буферного усилителя соединен с первой 6 шиной источника питания.

Существенный недостаток известного ДОУ состоит в том, что при малых напряжениях питания он не обеспечивает повышенные значения коэффициента усиления по напряжению. Это связано с тем, что его входной каскад имеет усиление по напряжению меньше единицы, а основное усиление обеспечивается промежуточным каскадом (второй 12 и четвертый 14 входные транзисторы).

Основная задача предполагаемого изобретения состоит в повышении разомкнутого коэффициента усиления по напряжению ДОУ без увеличения напряжения питания и ухудшения диапазона изменения его выходного напряжения.

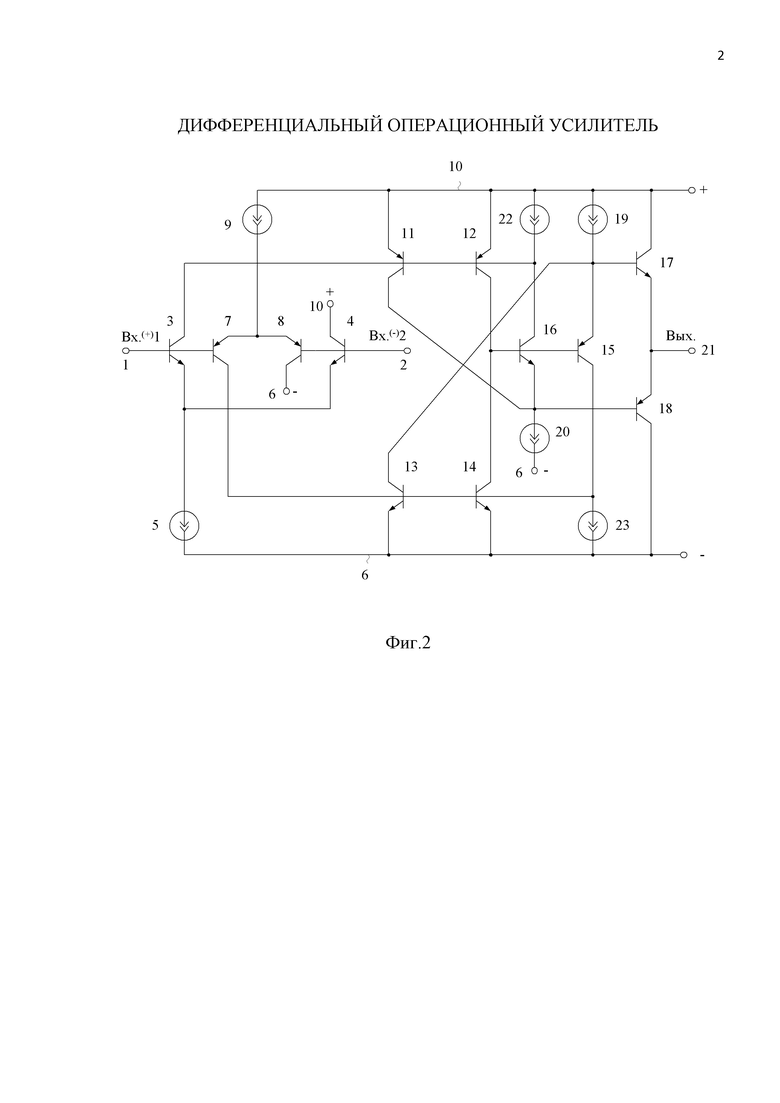

Поставленная задача достигается тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, второй 4 входной транзистор, база которого подключена ко второму 2 входу устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 3 и второго 4 входных транзисторов и первой 6 шиной источника питания, третий 7 входной транзистор, база которого соединена с первым 1 входом устройства, четвертый 8 входной транзистор, база которого соединена со вторым 2 входом устройства, второй 9 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами третьего 7 и четвертого 8 входных транзисторов и второй 10 шиной источника питания, первый 11 и второй 12 входные транзисторы промежуточного каскада, базы которых объединены, эмиттеры связаны со второй 10 шиной источника питания, третий 13 и четвертый 14 входные транзисторы промежуточного каскада, базы которых объединены, а эмиттеры связаны с первой 6 шиной источника питания, коллекторы второго 12 и четвертого 14 входных транзисторов промежуточного каскада соединены друг с другом и связаны с базами первого 15 и второго 16 входных транзисторов буферного усилителя, первый 17 и второй 18 выходные транзисторы буферного усилителя, причем база первого 17 выходного транзистора буферного усилителя соединена с эмиттером первого 15 входного транзистора буферного усилителя и через третий 19 токостабилизирующий двухполюсник подключена ко второй 10 шине источника питания, база второго 18 выходного транзистора буферного усилителя соединена с эмиттером второго 16 входного транзистора буферного усилителя и через четвертый 20 токостабилизирующий двухполюсник подключена к первой 6 шине источника питания, объединенные эмиттеры первого 17 и второго 18 выходных транзисторов буферного усилителя связаны с выходом устройства 21, коллектор первого 17 выходного транзистора буферного усилителя подключен ко второй 10 шине источника питания, коллектор второго 18 выходного транзистора буферного усилителя соединен с первой 6 шиной источника питания, предусмотрены новые элементы и связи – коллектор первого 3 входного транзистора связан с объединенными базами первого 11 и второго 12 входных транзисторов промежуточного каскада, а также коллектором второго 16 входного транзистора буферного усилителя и через пятый 22 токостабилизирующий двухполюсник связан со второй 10 шиной источника питания, коллектор третьего 7 входного транзистора соединен с объединенными базами третьего 13 и четвертого 14 входных транзисторов промежуточного каскада, а также коллектором первого 15 входного транзистора буферного усилителя и через шестой 23 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, причем коллектор первого 11 входного транзистора промежуточного каскада соединен с базой второго 18 выходного транзистора буферного усилителя, а коллектор третьего 13 входного транзистора промежуточного каскада связан с базой первого 17 выходного транзистора буферного усилителя, коллектор второго 4 входного транзистора согласован со второй 10 шиной источника питания, а коллектор четвертого 8 входного транзистора согласован с первой 6 шиной источника питания.

На фиг. 1 показана схема ДОУ-прототипа.

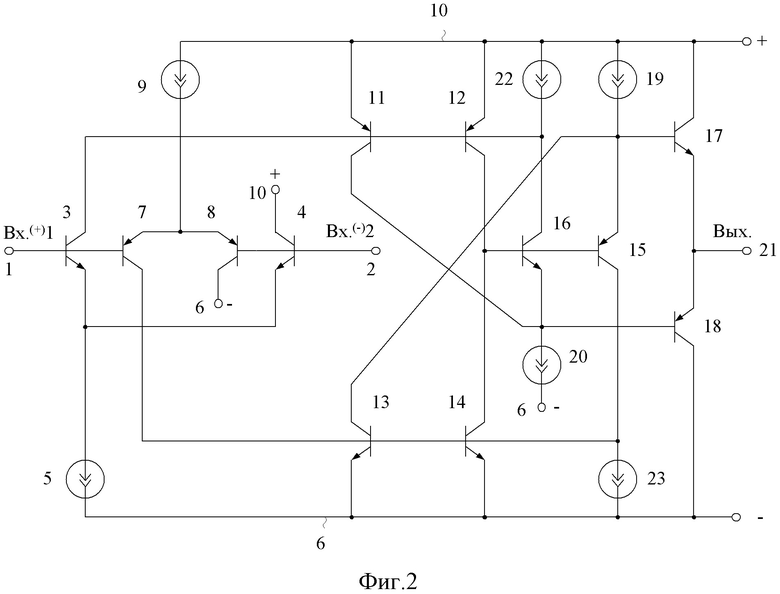

На фиг. 2 представлена схема заявляемого ДОУ.

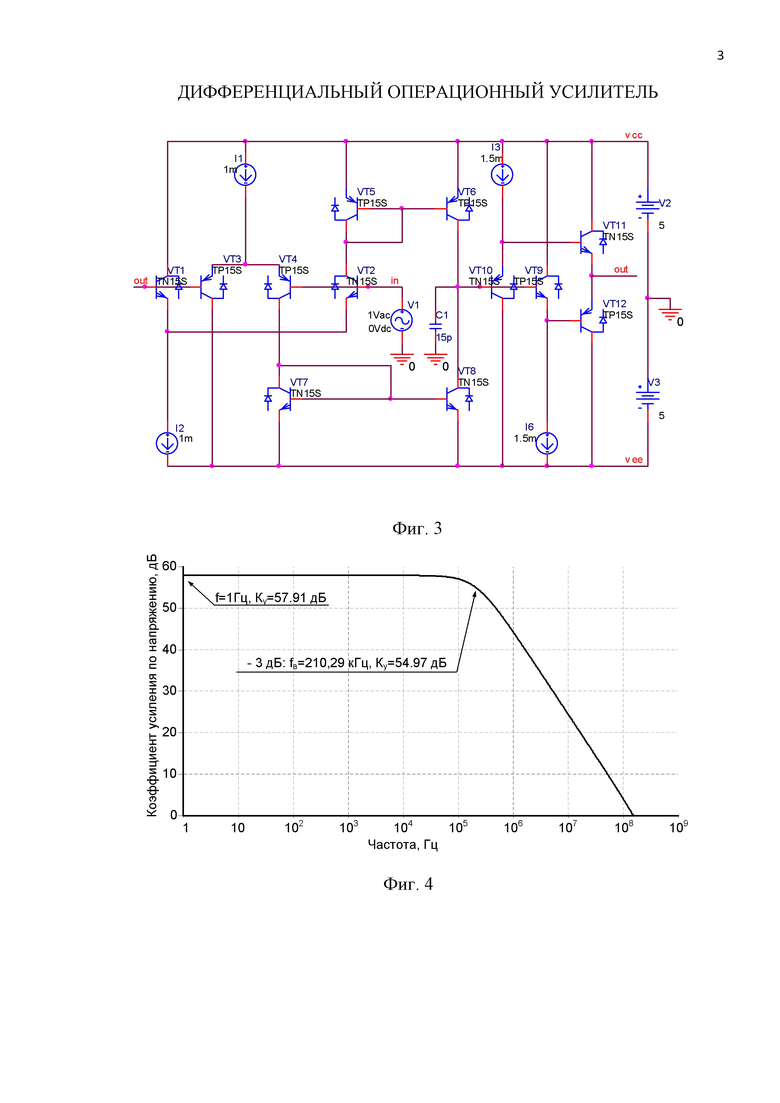

На фиг. 3 приведена схема ДОУ-прототипа фиг. 1 при 100% отрицательной обратной связи (ООС) в среде PSpice на моделях интегральных транзисторов TP15S и TN15S АО «НПП Пульсар» (г. Москва).

На фиг. 4 представлена амплитудно-частотная характеристика коэффициента усиления разомкнутого ДОУ-прототипа фиг. 3.

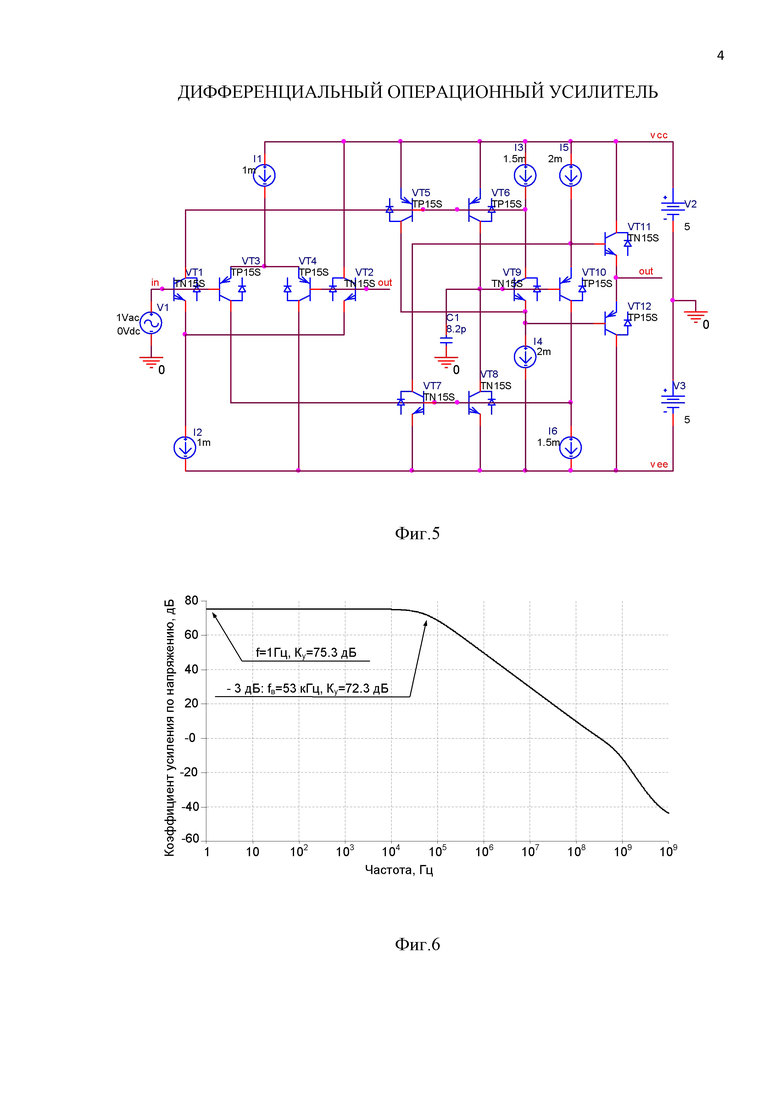

На фиг. 5 приведена схема заявляемого ДОУ фиг. 2 при 100% отрицательной обратной связи в среде PSpice на моделях интегральных транзисторов TP15S и TN15S АО «НПП Пульсар» (г. Москва).

На фиг. 6 представлена амплитудно-частотная характеристика коэффициента усиления разомкнутого ДОУ фиг. 5.

Дифференциальный операционный усилитель фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 входной транзистор, база которого подключена к первому 1 входу устройства, второй 4 входной транзистор, база которого подключена ко второму 2 входу устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 3 и второго 4 входных транзисторов и первой 6 шиной источника питания, третий 7 входной транзистор, база которого соединена с первым 1 входом устройства, четвертый 8 входной транзистор, база которого соединена со вторым 2 входом устройства, второй 9 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами третьего 7 и четвертого 8 входных транзисторов и второй 10 шиной источника питания, первый 11 и второй 12 входные транзисторы промежуточного каскада, базы которых объединены, эмиттеры связаны со второй 10 шиной источника питания, третий 13 и четвертый 14 входные транзисторы промежуточного каскада, базы которых объединены, а эмиттеры связаны с первой 6 шиной источника питания, коллекторы второго 12 и четвертого 14 входных транзисторов промежуточного каскада соединены друг с другом и связаны с базами первого 15 и второго 16 входных транзисторов буферного усилителя, первый 17 и второй 18 выходные транзисторы буферного усилителя, причем база первого 17 выходного транзистора буферного усилителя соединена с эмиттером первого 15 входного транзистора буферного усилителя и через третий 19 токостабилизирующий двухполюсник подключена ко второй 10 шине источника питания, база второго 18 выходного транзистора буферного усилителя соединена с эмиттером второго 16 входного транзистора буферного усилителя и через четвертый 20 токостабилизирующий двухполюсник подключена к первой 6 шине источника питания, объединенные эмиттеры первого 17 и второго 18 выходных транзисторов буферного усилителя связаны с выходом устройства 21, коллектор первого 17 выходного транзистора буферного усилителя подключен ко второй 10 шине источника питания, коллектор второго 18 выходного транзистора буферного усилителя соединен с первой 6 шиной источника питания. Коллектор первого 3 входного транзистора связан с объединенными базами первого 11 и второго 12 входных транзисторов промежуточного каскада, а также коллектором второго 16 входного транзистора буферного усилителя и через пятый 22 токостабилизирующий двухполюсник связан со второй 10 шиной источника питания, коллектор третьего 7 входного транзистора соединен с объединенными базами третьего 13 и четвертого 14 входных транзисторов промежуточного каскада, а также коллектором первого 15 входного транзистора буферного усилителя и через шестой 23 токостабилизирующий двухполюсник соединен с первой 6 шиной источника питания, причем коллектор первого 11 входного транзистора промежуточного каскада соединен с базой второго 18 выходного транзистора буферного усилителя, а коллектор третьего 13 входного транзистора промежуточного каскада связан с базой первого 17 выходного транзистора буферного усилителя, коллектор второго 4 входного транзистора согласован со второй 10 шиной источника питания, а коллектор четвертого 8 входного транзистора согласован с первой 6 шиной источника питания.

Работу и эффективность предлагаемого ДОУ фиг. 2 иллюстрируют результаты сравнительного компьютерного моделирования схем ДОУ-прототипа фиг. 3 и заявляемого устройства фиг. 5, представленные на графиках фиг. 4 и фиг.6. Анализ эти графиков показывает, что при идентичных выходном и входном каскадах, а также идентичных напряжениях питания заявляемый ДОУ фиг. 2 имеет на порядок более высокое разомкнутое усиление по напряжению. Данный эффект достигается за счет создания условий для усиления сигнала входным каскадом, в то время как в ДОУ-прототипе этот каскад обеспечивает усиление менее единицы.

Таким образом, в сравнении с ДОУ-прототипом предлагаемый ДОУ при одинаковых напряжениях питания обладает существенным преимуществом по величине разомкнутого коэффициента усиления по напряжению. В конечном итоге, это снижает погрешности преобразования сигналов и аналоговых интерфейсов на основе заявляемого устройства, в том числе в экстремальных условиях эксплуатации [31].

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4.783.637, fig. 1, 1988 г.

2. Патент US 5.515.005, fig.1, fig. 2, 1996 г.

3. Патентная заявка US 2005/0024140, fig. 9, fig. 11, 2005 г.

4. Патент SU № 1220105, 1984 г.

5. Патент US 3.968.451, fig.7, 1976 г.

6. Патент US 5.374.897, fig. 3a, 1994 г.

7. Патент US 6.504.419, fig. 2, 2003 г.

8. Патент US 5.512.859, fig. 1, 1996 г.

9. Патент US 4.636.743, fig. 1,1987 г.

10. Патент US 6.268.769, fig. 3, 2001 г.

11. Патент US 3.974.455, 1976 г.

12. Патент US 5.291.149, 1994 г.

13. Авт. свид. СССР № 530425

14. Патент US 5.814.953, 1998 г.

15. Патент US 5.225.791, 1993 г.

16. Авт. свид. СССР № 611288

17. Патент US 5.714.906, fig. 9a, fig. 15, 1998 г.

18. Патент US 6.794.940, fig. 1, 2004 г.

19. Патентная заявка US 2006/0125522, fig. 1a, fig. 1b, 2006 г.

20. Патентная заявка US 2006/0226908, fig. 4, 2006 г.

21. Патентная заявка US 2001/0052818, fig. 1, 2001 г.

22. Заявка на патент US 2004/0174216, fig. 1, fig. 2, 2004 г.

23. Патент EP 1150423 fig.3, 2001 г.

24. Патентная заявка US 2003/0206060, 2003 г.

25. Патент US 6.642.789, 2003 г.

26. Патент US 4.377.789, 1983 г.

27. Патент US 6.100.762, fig. 1, 2000 г.

28. Патент US 5.909.146, fig. 1, 1999 г.

29. Патент US 5.621.357, fig. 4, 1997 г.

30. Патент US 6.844.781, fig.2, 2005 г.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2013 |

|

RU2536376C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков. Технический результат заключается в повышении разомкнутого коэффициента усиления по напряжению дифференциального операционного усилителя без увеличения напряжения питания и ухудшения диапазона изменения его выходного напряжения. Дифференциальный операционный усилитель содержит входные транзисторы, токостабилизирующие двухполюсники, эмиттеры, шину источника питания, транзисторы промежуточного каскада, транзисторы буферного усилителя. 6 ил.

Дифференциальный операционный усилитель, содержащий первый (1) и второй (2) входы устройства, первый (3) входной транзистор, база которого подключена к первому (1) входу устройства, второй (4) входной транзистор, база которого подключена ко второму (2) входу устройства, первый (5) токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого (3) и второго (4) входных транзисторов и первой (6) шиной источника питания, третий (7) входной транзистор, база которого соединена с первым (1) входом устройства, четвертый (8) входной транзистор, база которого соединена со вторым (2) входом устройства, второй (9) токостабилизирующий двухполюсник, включенный между объединенными эмиттерами третьего (7) и четвертого (8) входных транзисторов и второй (10) шиной источника питания, первый (11) и второй (12) входные транзисторы промежуточного каскада, базы которых объединены, эмиттеры связаны со второй (10) шиной источника питания, третий (13) и четвертый (14) входные транзисторы промежуточного каскада, базы которых объединены, а эмиттеры связаны с первой (6) шиной источника питания, коллекторы второго (12) и четвертого (14) входных транзисторов промежуточного каскада соединены друг с другом и связаны с базами первого (15) и второго (16) входных транзисторов буферного усилителя, первый (17) и второй (18) выходные транзисторы буферного усилителя, причем база первого (17) выходного транзистора буферного усилителя соединена с эмиттером первого (15) входного транзистора буферного усилителя и через третий (19) токостабилизирующий двухполюсник подключена ко второй (10) шине источника питания, база второго (18) выходного транзистора буферного усилителя соединена с эмиттером второго (16) входного транзистора буферного усилителя и через четвертый (20) токостабилизирующий двухполюсник подключена к первой (6) шине источника питания, объединенные эмиттеры первого (17) и второго (18) выходных транзисторов буферного усилителя связаны с выходом устройства (21), коллектор первого (17) выходного транзистора буферного усилителя подключен ко второй (10) шине источника питания, коллектор второго (18) выходного транзистора буферного усилителя соединен с первой (6) шиной источника питания, отличающийся тем, что коллектор первого (3) входного транзистора связан с объединенными базами первого (11) и второго (12) входных транзисторов промежуточного каскада, а также коллектором второго (16) входного транзистора буферного усилителя и через пятый (22) токостабилизирующий двухполюсник связан со второй (10) шиной источника питания, коллектор третьего (7) входного транзистора соединен с объединенными базами третьего (13) и четвертого (14) входных транзисторов промежуточного каскада, а также коллектором первого (15) входного транзистора буферного усилителя и через шестой (23) токостабилизирующий двухполюсник соединен с первой (6) шиной источника питания, причем коллектор первого (11) входного транзистора промежуточного каскада соединен с базой второго (18) выходного транзистора буферного усилителя, а коллектор третьего (13) входного транзистора промежуточного каскада связан с базой первого (17) выходного транзистора буферного усилителя, коллектор второго (4) входного транзистора согласован со второй (10) шиной источника питания, а коллектор четвертого (8) входного транзистора согласован с первой (6) шиной источника питания.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВЫХОДОМ | 2009 |

|

RU2393627C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2019-05-21—Публикация

2018-07-20—Подача