«

(Л

7.«

со со

4

О

,

31499Д06.

элемента 8 соединены с выходами эле-тов 9 и 10 соедн)1ены с выходами элементом 1-6 первой ячейки 7, а выходментов 1-6 последнеГг ячейки 7, а выявляется уг равляюи1 1М выходом 11 запи-ходы являются информационны ш выхо- си регистра, информагщснные входы дами 14 и 15 регистра, утгравляюп ий 12 и 13 которого соединены с входамивход 16 считывания которого соединен элементов 1, 2, 3, 4 и 3, 4, 5, 6с входагш элементов 1-6 последней первой ячейки памяти 7, входы элемён-ячеЙ1ш 7. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Устройство программного управления | 1987 |

|

SU1418710A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Устройство для вывода информации | 1984 |

|

SU1180876A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

| Устройство для лексического анализа метатранслятора | 1983 |

|

SU1153329A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

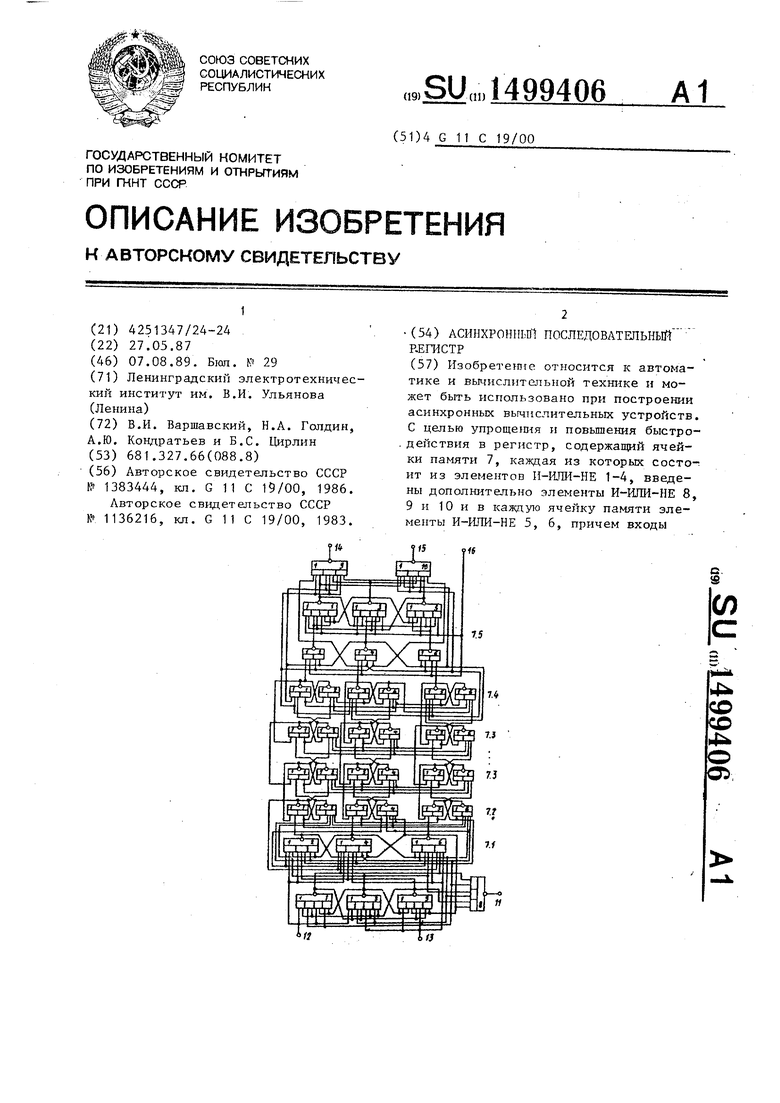

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных вычислительных устройств. С целью упрощения и повышения быстродействия в регистр, содержащий ячейки памяти 7, каждая из которых состоит из элементов И-ИЛИ-НЕ 1-4, введены дополнительно элементы И-ИЛИ-НЕ 8,9 и 10 и в каждую ячейку памяти элементы И-ИЛИ-НЕ 5,6, причем входы элемента 8 соединены с выходами элементов 1-6 первой ячейки 7, а выход является управляющим выходом 11 записи регистра, информационные входы 12 и 13 которого соединены с входами элементов 1,2,3,4 и 3,4,5,6 первой ячейки памяти 7, входы элементов 9 и 10 соединены с выходами элементов 1-6 последней ячейки 7, а выходы являются информационными выходами 14 и 15 регистра, управляющий вход 16 считывания которого соединен со входами элементов 1-6 последней ячейки 7. 1 ил.

Изобретение относится к автоматике и-вычислительной технике и может быть использовано при построении асинхронных вы-числитель.зплх устройств

Цель изобретеш-ш - упрощение асинхронного регистра сдвига и иовьшюние его быстродействия.

На чертеже представлен предлагае- мьй регистр.

Регистр содерлсит элементы И-ИЛН- ИЕ 1-6, образую11р1е элементы 7 и 8-10 памяти. На чертеже показаны также управляющий выход 11 записи, прямой 12 и инверсный 13 информационные входы, прямой 14 и инверсный 15 информационные выходы и управляющий вход 16 считывания регистра.

Регистр работает следующим образом.

Каждая ячейка 7.1, if2, ..., п-1 памяти имеет следующие уст6йчивые состояния (значения выходов ее элементов 1-6):100101 - в ячейке записана едишпда;- 010110 - в ячейке записан нуль; 011001 - значение разряда сдвигаемого кода, записанного в ячейку, совпадает со значегшем предьдущего разряда - в этом случае в ячейку записа 1а метка; 010101- информация в я1;1ейкс отсутствует - состояние гашения.

Благодаря блокирующим связям с выходов элементов 1 , 3 и 5 ячей1си 7.(i+1) памяти с входами элементов 1, 3 и 5 ячейки 7.1 памяти изменение состояния последней становится возможным только после того, как состояния ячеек 7.1 и 7. (1+1) будут одинаковыми. Иначе говоря, перепись информации из ячейки 7.(1-1) в ячейку 7.1 возможна только после того, как информация, записанная ранее в ячейку 7.1, перепишется в, ячейку 7. (1+1) При записи очередного состояш1я в ячейку 7.1 памяти она переходит из одного из указанных состояний в дру

0

5

0

5

0

5

0

5

гое через транзитные состояния 000101, 010001, 010100 и состояние гашения. Поскольку ячейка 7.1 памяти изменяет свое состояние нри подаче единичных значений на входы ее элементов 1-6 с входов элементов 2,1, 4, 3, 6, 5 ячейки 7.(1-1) и элементов 1, 3, 5 ячейки 7. (1+1), то она воспринимает только устойчивые состоя1шя этих ячеек памяти, а их транзитные состояния не воспринимаются, т.е. последние не нарушают правильного функционирования регистра при любых величинах задержек его элементов.

Элементы i, 3, 5 и 2, 4, 6 ячеек 7.1 и памяти образуют трехста- бильные триггеры, состояния которых 100 и 011, 001 и 110 и 010 и 101 соответствуют записи единицы, нуля и метки в эти триггеры.

Когда на обоих информационных входах 12 и 13 регистра имеются нулевые значения, т.е. информация на этих входах отсутствует, состояние триггера из элементов 2, 4, 6 ячейки 7.1 переписывается в триггер из . ее элементов 1, 3, 5. По завершении этого процесса значения на выходах пар элементов 1 и2, Зи4и5и6 ячейки 7.1 становятся противоположныо

МИ, в результате чего на одном из входов каждой группы И элемента 8 появится нулевое значение, а на его выходе, т.е. на управляющем выходе 11 записи регистра, - единичное значение. При этом изменение состояния триггера из элементов 2, 3, 6 ячейки 7 памяти, блотшруется нулевыми зна-- чениями на информационных входах 12 и 13 регистра.

Приняв единичное значение с выхода 11 регистра, источник информации может подать очередной разряд сдвигаемого кода на информационные входы 12 и 13 регистра, установив на одном из них единичное значение. Если к этому моменту предыдущее состояние триггера из элементов 2, 4, 6 ячейки 7. памяти переписано в ячейку 7,2 памяти, то состояние этого триггера изменяется следующим образом. При единичном значеьши на входе 12 в этот триггер записывается единица (011), если в триггере из элементов 1, 3, 5 ячейки 7.1 записана метка (010) или нуль (001), и записывается метка (101), если в триггере из элементов 1, 3, 5 ячейки 7.1 записана единица (100). При единичном значении на входе 13 в триггер из элементов 2, 4, 6 ячейки 7.1 записывается нуль (110), если в триггере элементов 1,3, 5 записана метка (010) или единица (100), и записьшается метка (101), ес-гги в триггере из ее элементов 1, 3, 5 записан нуль (001). По завершении этого процесса на входах одной из групп И элемента 8 появятся единичные значения, а па вьЕходе этого элемента, т.е. управляющем выходе 11 регистра, - нулевое значение При этом изменегше состояния триггера из элементов 1, 3, 5 ячейки 7.1 блокируется единичным значением на одном из входов 12 или 13 регистра.

Приняв нулевое значение с выхода 11 регистра, источник может снять информацию с его входов 12 и 13, т.е. снова установить на них нулевые значешш, и т.д. 1

При нулевом значении на управляющем входе 16 регистра изменение состояния триггера из элементов 2, 4, 6 ячейки 7.П памяти заблокировано и разрешена перепись состояния из этого триггера в триггер из ее элементов 1, 3, 5. По завершении этого процесса значения на выходах пар элементов 1и2, Зи4и5и6 ячейки 7.П становятся противоположными, в результате чего на одном из входов каждой группы И элементов 9 и 10 появится нулевое значение, а на их выходах, т.е. на информационных выходах 14 и 15 регистра, - единичные значения, что означает отсутствие на них информации.

Для того, чтобы считать информацию из регистра, приемник должен установить на его управляющем входе 16 считывания единичное значение. При этом блокируется изменение состояния триггера из элементов 1, 3, 5 ячейки 7.П, а в триггер из ее эле0

5

0

5

0

5

0

0

5

ментов 2, 4, 6 переписывается информация из ячейки 7.(п-1). Если при этом значе ие предьщущего разряда сдвигаемого кода бьшо едишгчным (состояние триггера из элементов I, 3, 5 ячейки 7.П - 100), то в триггер из элементов 2, 4, 6 ячейки 7.П может быть записан нуль (110) юти метка (101) - последнее означает, что значение очередного разряда совпадает с пред дпу1ф1м, т.е. в данном cjjj iiae един1-гчнос. В первом случае нулевое значение появится на выходе элсмептл 10, т.е. на информационном выходе 15 регистра, а во втором случае - на выходе элемента 9, т.е. на информационном выходе 14 регистра. Если значение пре- дьщущего разряда сдвигаемого кода 6iino нулевым (состояние триггера из элементов 1,3, 5 я гейки 7.п - 001), то в триггер из элементов 2, 4, 6 ячейк - 7.П может быть записана единица (011) или метка (101) - последнее означает, что значение очередного разряда сдвигаемого кода нулевое. В первом случае нулевое значение появится на выходе элемента 9, т.е. на информационном выходе 14 регистра, а во втором случае - на выходе элемента 10, т.е. на информационном выходе 15 регистра. Наконец, если в триггер из элементов 1, 3, 5 ячейки 7.П записана метка (010), то в триггер из ее элементов 2, 4, 6 может быть записана единица (011) или нуль (Т 10). В первом случае нулевое значение появится на выходе элемента 9, т.е. на информационном выходе 14

регистра, а во втором случае - на выходе элемента 10, т.е. на информационном выходе 15 регистра.

Получив информацию с выходов 14 5 И 15 регистра, приемник может снова установить нулевое значение на его управляющем входе 16 считьшания и т.д.

Дпя того, чтобы очистить регистр перед началом работы, надо изменением значения на его управляющем входе 16 считьшания считать из -него информацию до тех пор, пока состояние всех ячеек 7.1 не станут, одинаковыми.

Частота выполнения операции сдвига в предлагаемом регистре составляет 17(61), где С - задержка элемента И-ИЖ-НЕ.

в известном регистре частота выполнения операции сдвих а, раилая l/CGt), достигается только при определенном сочетании значений разрядов сдвигаеиого кода, т,е, предлагаемое техническое решение обеспечивает повьшюние быстродействия регистра но сравнепн. о с известным.

оВ предлагаемом асгапфонном после- доватшгьном регистре, для хранения одного разряда сдвигаемого кода требу- етс51 только одна ячейка, тогда как 1 изнестиом регистре - дпе ячейки. Оценивая затраты оборуиования регистра суммарны. числом вх.одов и выходов элементов, Hpitxv, на одгтн раз-ряд сдвигаемого код., для

10

15

„ иредлагаемого ре.гисчр;. д,ля известного.

77

- Л

20

Ф о р м у л

и

о б р е т о п. и

Лсикхронныл лосуюдпга.гель илй ро содержащий ячейки памят.и, кажГИСЧ р ,

дал из 7соторьтх coCTOi T и.з четырех элег.йентов И 11ПИ-НЕ, npir-isM в каждой памяти, кроме первой и последней, выходы iiepiBoro, второго, третьего и г1етлертого элементов НЕ сосдигшны с входами первых И второго, нервог о, четвертого и третьего элементов И--ИЛ1-1-НЕ данной, ячейки намяти, выходы второго и четвертого .элементов И Ш1И-НЕ - с пер- П1).Я1 входами- вторых групп четвертого и второго элеме.нтов И-ШШ-ПЕ данной ячейки памяти, выходы и первые входы иторык, .г руин И первого и третьего .ч.лементоп - с вторьпш входами вторь х групп И второго и хщтвертого элементов И-ИЛИ-НЕ следующей ячейки памяти и выходами второго и четвертого элементов И- ИЛИ-ПЕ предьиуд;ей яче.йки памяти, при этом выходы первого и третьего элементов И-1-Ш11-НЕ .1,ой я чейки -памяти, кроме первой, второй и нослед- ней, соединены с втopы яl входами вторых грунп И первого и третьего элементов И-ИЛИ-ПЕ нредццущей ячейки памяти, а выходы второго и четвертого элементов И-ИЛИ НЕ первой и последней ячейки памяти - с первь а- входами иервых групп И первого и третьего элементов И-Ш1И-НЕ данной ячейют, о т л и-ч а ю щ и и с я тем, что, с целью yнpolцe ия и повышения быстродействия регистра, в него введены три

выходных элемента И-НЛИ-НЕ и в каж- , -душ ячейку - пятый и шестой элементы И-ЩШ-НЕ, причем в каждой ячейке памяти, кроме первой и носледней, выходы пятого и шестого элементов И- ШШ-ИЕ соединены с входами первых групп И шестого и пятого, элементов И-Ш М-ИЕ данной ячейки памяти, вькод и первый-и второй входы второй группы И шестого элемента И-ШТИ-НЕ - с тре- тьимя входами вторых групп И и выхо- второго и четвертого элементов И--ИЛИ ИЕ да1Н1ой ячейки памяти, а выход и пер.вый вход второй группы И пятого элемента И-ИШ-1-НЕ - с третьим входом второй группы И шестого ЭJ eмeнтa И-ШШ-ИЕ следу1ош,е.й ячейки памяти II выходом шестого элемента предьцо цей ячейки памяти, при этом вЬгход пятого элемента И- ИЛИ--11Е ка)кд:ой ячейки памяти, кроме первой, второй и последней, соединен с вторым входом второй группы И пято- го элемента И-ИГШ-НЕ предьщущей ячейки памяти, а .выход шестого элемента последней ячейки - с первым входом первой группы И пятого элемен- ч а И-ИЛ1 1-НЕ данной ячейки памяти, первые входы перво.й, второй и третьей групп И первого выходного э.пе- мента Ы-Т-ШИ-НЕ соединены с выходами первого, третьего и пятого, с первыми входами первьк И четвертого и шестого и второго, вторых групп И шестого, второго и четвертого, с вто рь&ш входами первых и вторых групп И третьего, пятого и первого и третьих и четвертых групп И пятого, первого и третьего элементов ИЧ ШИ-НЕ первой ячейки памяти, а вторые входы первой, второй и третьей групп И - с выходами второго, четвертого.и шестого, с первыми входа1 ш третьих групп И четвертого, шестого и второго, с вто- 4S pMNM входами третьих,групп И шестого, BTOpoi o и четвертого и с первыми входаш пер.вых и третьих групп И пер- вог о, третьего и пятого элементов И-ШШ-FIE первой ячейки памяти, -первые входы вторых и четвертьк групп И первого, второго, грзшпы И третьего и вторые входы первой и второй групп И и первой группы И четвертого элементов И-ИЛИ-НЕ первой ячейки памяти являются прямььм информационным входом регистра, а первые входы второй и четвертой групп И пятого, четвертой группы И третьего, вторые входы первой и второй групп И шестого и второй

30

35

40

50

55

группы и четвертого элементов И-ИЛИ- НЕ первой ячейки памяти являются инверсным информационным входом регистра, третьи входы первых групп И второго, четвертого и шестого элементов И-ИЛИ-НЕ первой ячейки памяти соединены с выходами пятого, первого и третьего элементов И-ИЛИ-НЕ второй ячейки памяти, а третьи входы вторых групп И - с выходами третьего, пятого и первого элементов И-ИЛИ-НЕ второй ячейки памяти, первые входы их первых, вторых и третьих групп И второго и третьего выходных элементов И-ИЛИ-НЕ соединены с выходами первого, третьего и пятого, с вторыми входами первых и вторых групп И третьего, пятого и первого и третьих и четвертых групп И пятого, первого и третьего элементов И-ШШ-НЕ последней ячейки памяти, вторые входы первых, вторых и третьих ;групп И .второго и третьего выходных элементов И-ШШ-НЕ соединены с выходами второго, четвертого и шестого с первыми входами первых групп И четвертого, шестого и второго, с BTopbiNiH входами первых групп И шестого, второго и четвертого и с первыми входами вторых и третьих

Редактор Н. Тупида

Составитель А.Дерюгин Техред М.Ходанич

Заказ 4700/51

Тираж 558

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

И первого, третьего и пятого элементов И-1-ШИ-иЕ последней иейки памяти, с п ервьми входаья вторых групп И третьего, пятого и первого и с третьими входам вторых групп И пятого, первого и третьего элементов И-ИЛИ-НЕ предпоследней ячейки памяти третьи входы первой и второй групп И второго выходного элемента И-ИЛИ-Н соединены с выходом шестого, а третьей группы И - с выходом четвертого элементов И-ИЛИ-НЕ последней ячейки памяти, третьи входы второй п третье групп И третьего доиопнительного элемента И-ИЛИ-НЕ соедине Ш с выходом второго, а первой группы И - с выходом четвертого элемента И-ИЛИ-НЕ по- следней ячейк} памяти, первые входы второй I четвертой групп И первого, третьего и пятого и вторьк групп И второго, четвертого и шестого элементов И-ИЛИ-НЕ последней ячеГпш памяти являются управляют ;- входом считывания регистра, выходы первого, второго- и третьего выходных элементов И-ИЛИ-НЕ являются соответственно управляющим выходом записи, прямым и инверсным информационным- выходами регистра.

Корректор М.Ма1«симишинец

Поднисное

| Асинхронный последовательный регистр | 1986 |

|

SU1383444A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-07—Публикация

1987-05-27—Подача