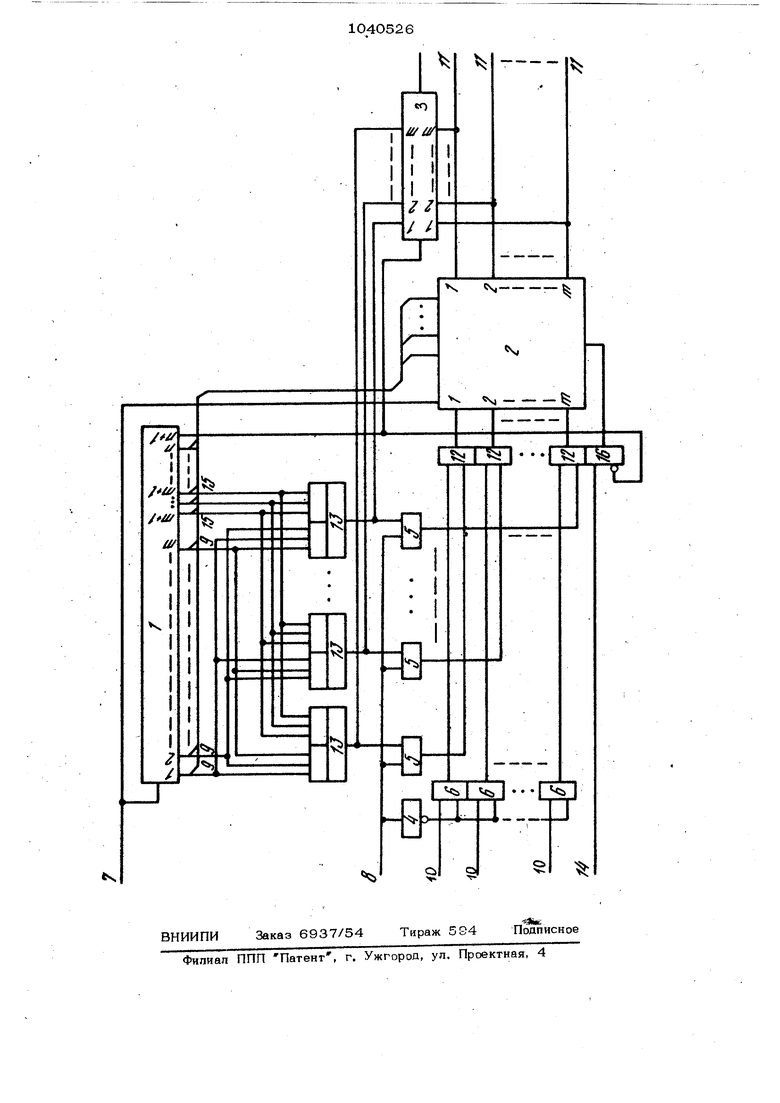

Изобретение относится к вычислитель ной технике, в частности к запоминающи устройствам. Известно устройство для контроля опе ративной памяти, содержащее блок формирования тестовых последовательностей блок управления, адресный блок, блок подключения матриц, блок , блок обнаружения неисправностей, регистры, блок местаюго управления, схему сравнения, элементы И и элемент НЕ Cl J Недостатком устройства является сложность, обусловленная применением формирователей тестовых последовательностей, требующих большого объема оборудования. Наиболее близкой к предлагаемой по технической сущности является система для проверки запоминающего устройства, содержащая счетчик, первую и вторую группы элементов И, элемент НЕ, группу элементов ИЛИ, блок сравнения. К системе подключается проверяемый блок пам ти. В этой системе источниками тестовой Ш1фор,4ации, записываемой в блок памяти, $юляются младшие разряды счетчика, выходы которого являются адресны ми входами блока памяти С 2 . Однако такая система характеризуетс невысокой достоверностью контроля, поскольку динамические качества адресного кода формирования теста слишком ограни чены из-за различной скорости смены информации в разных разрядах блока памяти. 11ель изобретения - повышение точнос ти контроля. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, информационные выходы которого подключе ны к одним информационным входам блока сравнения и являются информационным выходами устройства, блока сравнения 5шляется управляющим выходом устройства, адресные входы накопителя подключены к выходам первой и второй группы счетчика, тактовый вход которого подключен к первому управл5оощему входу накопителя и является первым управляющим входом устройства, информационные ВХОД1Ы накопителя подключены к выходам элементов ИЛИ, одни входы которых подключены к выходам первых элементов И, другие - к выходам вторых элементов И, одни входы которьк являют ся шй{юрмационными входами устройства, , другие подключены к выходу элемента НЕ, вход которого подключен к одним входам первых- элеМЬнтов И и является вторым управляющим входом устройства, дополнительно содержит коммутаторы и элемент ЗАПРЕТ| выход которого подключен к второму управляющему входу накопителя, первый вход элемента ЗАПРЕТ является третьим управляющим входом устройства, второй вход элемента ЗАПРЕТ подключен к соответствующему выходу счетчика, информационные входы коммутатора подключены к соответствующим выходам первой группы счетчика, управляющие входы коммутаторов подключены к выходам второй группы счетчика, выходы коммутаторов подключены к другим входам блока сравнения, управляющий вход которого подключен к второму входу элемента ЗАПРЕТ. На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит счетчик 1, служащий для задания кодов адресов проверяемого блока 2 памяти, блок 3 сравнения, элемент НЕ 4, первую группу элементов И 5, вторую группу элементов И 6, управляющий вход 7 (вход синхронизации) устройства, управляющий вход 8 устройства, m младших разрядов 9 счетчика 1, информационные входь Ю устройства, информационные выходы 11 устройства, группу элементов ИЛИ 12, коммутаторы 13, управляющий вход 14 (Запись-считывание) устройства, Q старших разрядов 15 счетчика, элемент ЗАПРЕТ 16. Вход 8 и первая 5 и вторая 6 группы элементов И устройства предназначены для подключения к информационным входам блока 2 памяти либо младших m разрядов счетчика 1 (через коммутатором 13), либо входных шин 10 устройства при работе от внешнего источника тестовой последовательности. Устройство работает следующим образом.. На входе 8 устройства устанавливает ся высокий уровень сигнала. Счетчик 1 обнуляется (цепи обнуления условно не показаны). На выходах 15 счетчика 1 присутствуют низкие уровни сигналов. Информационные входы коммутаторов 13 подключены к гп младшим разрядам счетчика 1 таким образом, что выход каждого из m разрядов счетчика 1 скоммутирован с выходом только одного (любого) коммутатора. По входной шине 7 поступают импульсы синхронизации, при этом через элеент ЗАПРЕТ 16 разрешено прохождение

импульсов записи на вход блока 2 памяти Текущое значение кодов счетчика 1 поступает на адресные входы блока 2 памяти, а на его информационные входы поступает текущее значение кодов младших m разрядов счетчика 1 через коммутаторы 13, открытую группу элементов И 6 и группу элементов ИЛИ 12. Происходит рабочий цикл записи информации в блок 2 памяти. Через 2 адреса происходит изменение кода на выходах 15 счетчика 1 и к каждому Ш1фо1 1ацнш ному входу блока 2 памяти коммутаторы 13 подключают другие разряда c4eT4iqcai 1. Таким образом, в каждый разряд 2 памяти в различных циклах (шгательностью 2 периодов синхрочастоты) записывается информация с различных младших разрядов счетчика 1, чем достигается выравнивание скорости смены ии- формации в разных разрядах блока 2 памят, т. е. динамические качества проверки улучшаются. Через 2 адреса в весь блок 2 памяти записывается тестовая информация. Сигнал с выхода (п + 1) разряда счетчика 1 поступает на управляющий вход элемента ЗАПРЕТ и запрещает прохождение импульсов записи на блок 2 памяти. Одновременно разрешается работа блока 3 сравнения. В следующем цикле происходит считывание информации из блока 2 памяти и сравнение с записгшной в режиме записи информацией. В случае несовпаде1Я1я записанной и считываемы информации по каким-либо адресам появляется сигнал Не равно на выходе устройства. Количество управляющих щин коммутаторов Р Р2- m , :где m - количество информационных шин. Для 16-разрядных блоков памяти могут быть применены камиутеао 16x1 с четы1я мя управляющими входами.

Таким офазом, введение в предлагавмое устрс ство элемента ЗЛПРЕТ и коммтаторов позволяет существенно повысить достове шость ксжтрсля за счет вырашш,вания скорости смеиы инфо1 |1ации в разг ных разрядах проверяемого блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накрпитель, информационные выходы которого подключены к одним информацисшным входам блока сравнения и являются информа 1(ионными вькодами устройства, выход 6iKvка сравнения является управлякпцим вы- ходом устройства, адресные входы на ксшителя подключены к выходам пер вой и -второй группы счетчика, тактобый вход которого подключен к первому управляющему входу накопителя и являет ся первым управляющим входом устрейст&а, информационные входы накопителя подключены к выходам элементов ИЛИ, одни . . ВХОДЫ которых подключены к выходам первых элементов И, другие - к выходам вторых элементов И, одни входы которых являются {Щформаиионными входами уст ройства, другие подключены к выходу элемента НЕ, вход котс рогчэ подключен к одним входам первых элементов И и является вторьш упрсшляющим входом устрс ства, отлича.ющееся тем, что, с целью ловышення точности контроля, оно содержит коммутаторы и элемент ЗАПРЕТ, выход которого подключен к второму управляющему входу накопителя, первый вход элемента ЗАПРЕТ является третьим управляющим входом устройсотза, с S второй вход элемента ЗАПРЕТ подключен к соответствукицему выходу счетчика, (Л информационные входы коммутатора подклочены к соответствующим выходам первой группы счетчика, управляющие входы коммутаторов подключены к выходам второй группы счетчика, выходы коммутаторов подключе к Д1Щ11М входам блока сравнения, управяякшшй вход которого 4 О подключен к второму входу элемента ЗАПРЕТ. сл 1C О)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР, № 750570 | |||

| кл | |||

| Q | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-09-07—Публикация

1982-02-22—Подача